1、PCI地址空間

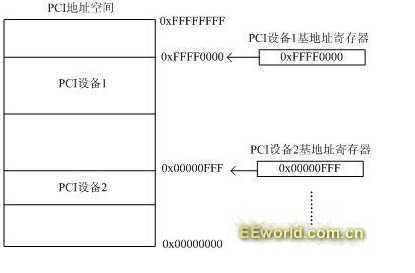

PCI總線具有32位數據/地址復用總線,所以其存儲地址空間為2的32次方=4GB。也就是PCI上的所有設備共同映射到這4GB上,每個PCI設備占用唯一的一段PCI地址,以便于PCI總線統一尋址。每個PCI設備通過PCI寄存器中的基地址寄存器來指定映射的首地址。PCI地址空間對應于計算機系統結構中的PCI總線。

2、系統地址空間

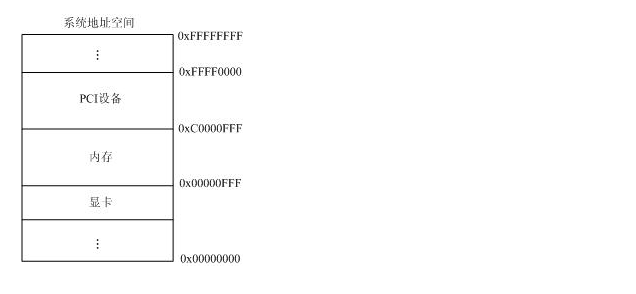

如果處理器具有32位的地址總線,其理論可尋址空間為2的32次方=4GB。但這并不意味著內存就可以4GB大小,其實XP系統最大內存大約為2GB,這與CPU訪問系統中其它設備的存儲器方式有關(比如CPU訪問PCI總線上的存儲器)。

計算機系統中在不同的物理位置上存在著不同設備,不同的設備又各自具有存儲器,那么CPU如何訪問這些存儲器呢?CPU把系統中各個設備的存儲空間映射到一個統一的存儲空間上,稱為系統存儲空間共4GB,這樣CPU就可以訪問到所有的存儲器。比如PCI存儲器映射到從0xFFF80000開始的地址空間,顯卡映射到0XFFF00000,再加上操作系統會占用一些空間,就只剩下不到2G能真正分配給物理內存了。(具體數值是為解釋需要取的任意值,不代表真實情況)

系統地址空間對應于計算機系統結構中的前端總線(FSB)。

3、PCI總線地址與系統存儲空間轉換映射

3、PCI總線地址與系統存儲空間轉換映射

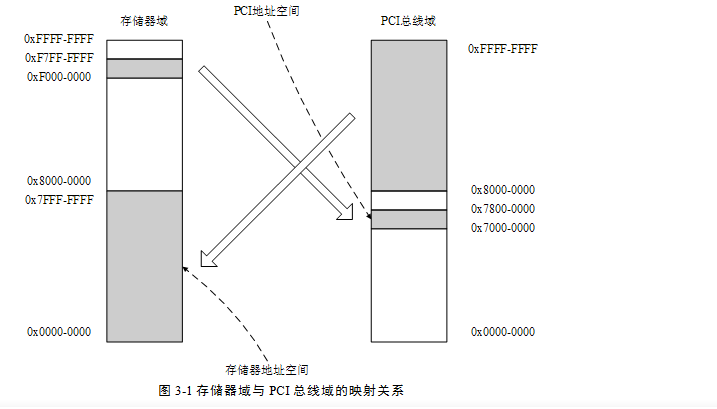

我們假設在一個32位處理器中,其存儲器域的0xF000-0000~0xF7FF-FFFF(共128MB)這段物理地址空間與PCI總線的地址空間存在映射關系。

當處理器訪問這段存儲器地址空間時,HOST主橋將會認領這個存儲器訪問,并將這個存儲器訪問使用的物理地址空間轉換為PCI總線地址空間,并與0x7000-0000~0x77FF-FFFF這段PCI總線地址空間對應。

為簡化起見,我們假定在存儲器域中只映射了PCI設備的存儲器地址空間,而不映射PCI設備的I/O地址空間。而PCI設備的BAR空間使用0x7000-0000~0x77FF-FFFF這段PCI總線域的存儲器地址空間。

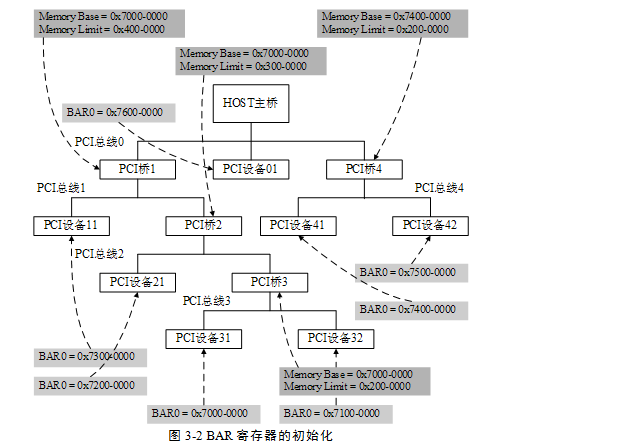

PCI橋的Base、Limit寄存器保存“該橋所管理的PCI子樹”的存儲器或者I/O空間的基地址和長度。值得注意的是,PCI橋也是PCI總線上的一個設備,在其配置空間中也有BAR寄存器,本節不對PCI橋BAR寄存器進行說明,因為在多數情況下透明橋并不使用其內部的BAR寄存器。下文以圖3?2所示的處理器系統為例說明上述寄存器的初始化過程,該處理器系統使用的存儲器域與PCI總線域的映射關系如圖3?1所示。

注意觀察上圖中PCI設備的BAR0寄存器值,如果PCI設備向下級聯了(相當于PCI橋),BAR0是不變的,而且LIMIT寄存器受PCI未繼續級聯(而是直接接了PCI設備)的BAR0影響。

在PCI設備的BAR寄存器中,包含該設備使用的PCI總線域的地址范圍。在PCI設備的配置空間中共有6個BAR寄存器,因此一個PCI設備最多可以使用6組32位的PCI總線地址空間,或者3組64位的PCI總線地址空間。這些BAR空間可以保存PCI總線域的存儲器地址空間或者I/O地址空間,目前多數PCI設備僅使用存儲器地址空間。而在通常情況下,一個PCI設備使用2到3個BAR寄存器就足夠了。

為簡化起見,我們首先假定在圖3?2中所示的PCI總線樹中,所有PCI Agent設備只使用了BAR0寄存器,其申請的數據空間大小為16M字節(即0x1000000字節)而且不可預讀,而且PCI橋不占用PCI總線地址空間,即PCI橋不含有BAR空間。并且假定當前HOST主橋已經完成了對PCI總線樹的編號。

根據以上假設,系統軟件該PCI總線樹的遍歷過程如下所示。

(1)系統軟件根據DFS算法,系統軟件率先尋找到第一組PCI設備,分別為PCI設備31和PCI設備32[1],并根據這兩個PCI設備需要的PCI空間大小,從PCI總線地址空間中(0x7000-0000~0x77FF-FFFF)為這兩個PCI設備的BAR0寄存器分配基地址,分別為0x7000-0000和0x7100-0000。

(2)當系統軟件完成PCI總線3下所有設備的BAR空間的分配后,將初始化PCI橋3的配置空間。這個橋片的Memory Base寄存器保存其下所有PCI設備使用的“PCI總線域地址空間的基地址”,而Memory Limit寄存器保存其下PCI設備使用的“PCI總線域地址空間的大小”。系統軟件將Memory Base寄存器賦值為0x7000-0000,而將Memory Limit寄存器賦值為0x200-0000。

(3)系統軟件回朔到PCI總線2,并找到PCI總線2上的PCI設備21,并將PCI設備21的BAR0寄存器賦值為0x7200-0000。

(4)完成PCI總線2的遍歷后,系統軟件初始化PCI橋2的配置寄存器,將Memory Base寄存器賦值為0x7000-0000,Memory Limit寄存器賦值為0x300-0000。

(5)系統軟件回朔到PCI總線1,并找到PCI設備11,并將這個設備的BAR0寄存器賦值為0x7300-0000。并將PCI橋1的Memory Base寄存器賦值為0x7000-0000,Memory Limit寄存器賦值為0x400-0000。

(6)系統軟件回朔到PCI總線0,并在這條總線上發現另外一個PCI橋,即PCI橋4。并使用DFS算法繼續遍歷PCI橋4。首先系統軟件將遍歷PCI總線4,并發現PCI設備41和PCI設備42,并將這兩個PCI設備的BAR0寄存器分別賦值為0x7400-0000和0x7500-0000。

(7)系統軟件初始化PCI橋4的配置寄存器,將Memory Base寄存器賦值為0x7400-0000,Memory Limit寄存器賦值為0x200-0000。系統軟件再次回到PCI總線0,這一次系統軟件沒有發現新的PCI橋,于是將初始化這條總線上的所有PCI設備。

(8) PCI總線0上只有一個PCI設備,PCI設備01。系統軟件將這個設備的BAR0寄存器賦值為0x7600-0000,并結束整個DFS遍歷過程。

精彩推薦 至芯科技12年不忘初心、再度起航12月17日北京中心FPGA工程師就業班開課、線上線下多維教學、歡迎咨詢! 至芯科技精品寒假班來襲,1月7號線上授課,歡迎廣大學子,電子愛好者前來學習! FPGA學習-IO延遲的約束方法 關于數字信號處理中的降采樣掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:PCI總線地址空間與系統地址空間的關系

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604340

原文標題:PCI總線地址空間與系統地址空間的關系

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MAC地址的作用范圍,MAC地址怎么申請?

一文分清IP地址、子網和子網掩碼的關系

怎么綁定IP地址和MAC地址

電壓空間矢量與磁鏈矢量的關系是什么

IP地址會被黑?

IP地址與子網劃分

IP 地址管理與無類域間路由

PCI總線地址空間與系統地址空間的關系

PCI總線地址空間與系統地址空間的關系

評論