時(shí)序約束條件

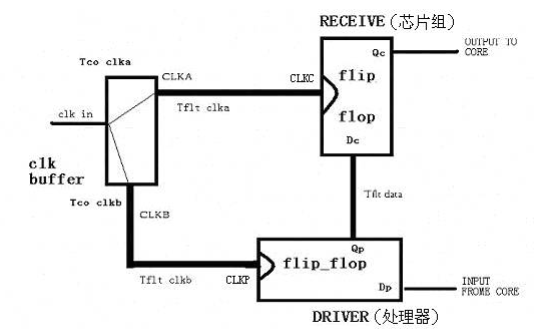

下面來(lái)具體討論一下系統(tǒng)時(shí)序需要滿足的一些基本條件。我們?nèi)匀灰韵聢D的結(jié)構(gòu)為例,并可以據(jù)此畫出相應(yīng)的時(shí)序分析示意圖。

在上面的時(shí)序圖中,存在兩個(gè)時(shí)序環(huán),我們稱實(shí)線的環(huán)為建立時(shí)間環(huán),而虛線的環(huán)我們稱之為保持時(shí)間環(huán)。可以看到,這兩個(gè)環(huán)都不是閉合的,缺口的大小就代表了時(shí)序裕量的多少,因此設(shè)計(jì)者總希望盡可能增大這個(gè)缺口。同時(shí)還要注意到,每個(gè)環(huán)上的箭頭方向不是一致的,而是朝著正反兩個(gè)方向,因?yàn)檎麄€(gè)系統(tǒng)時(shí)序是以時(shí)鐘上升沿為基準(zhǔn)的,所以我們時(shí)序環(huán)的起點(diǎn)為系統(tǒng)時(shí)鐘clk in的上升沿,而所有箭頭最終指向接收端的控制時(shí)鐘CLKC的邊沿。

先來(lái)分析建立時(shí)間環(huán):

缺口的左邊的半個(gè)時(shí)序環(huán)代表了從第一個(gè)系統(tǒng)時(shí)鐘上升沿開始,直到數(shù)據(jù)傳輸至接收端的總的延時(shí),我們計(jì)為數(shù)據(jù)延時(shí),以Tdata_tot表示:

Tdata_tot=Tco_clkb+Tflt_clkb +Tco_data +Tflt_data

上式中:Tco_clkb是系統(tǒng)時(shí)鐘信號(hào)CLKB在時(shí)鐘驅(qū)動(dòng)器的內(nèi)部延遲;Tflt_ clkb 是CLKB從時(shí)鐘驅(qū)動(dòng)器輸出后到達(dá)發(fā)送端(CPU)觸發(fā)器的飛行時(shí)間;Tco_data是數(shù)據(jù)在發(fā)送端的內(nèi)部延遲;Tflt_data是數(shù)據(jù)從發(fā)送端輸出到接收端的飛行時(shí)間。

從CLKC時(shí)鐘邊沿的右邊半個(gè)時(shí)序環(huán)代表了系統(tǒng)時(shí)鐘到達(dá)接收端的總的沿時(shí),我們計(jì)為時(shí)鐘延時(shí),以Tclk_tot表示:

Tclk_tot =Tcycle +Tco_clka +Tflt_clka – Tjitter

其中,Tcycle是時(shí)鐘信號(hào)周期;Tco_clka 是系統(tǒng)時(shí)鐘信號(hào)CLKA(第二個(gè)上升沿)在時(shí)鐘驅(qū)動(dòng)器的內(nèi)部延遲;Tflt_clka是時(shí)鐘信號(hào)從時(shí)鐘驅(qū)動(dòng)器輸出到達(dá)接收端觸發(fā)器的飛行時(shí)間;Tjitter是時(shí)鐘的抖動(dòng)誤差。

因此我們可以根據(jù)建立時(shí)間裕量的定義,得到:

Tsetup_margin = Tclk_tot – Tdata tot – Tsetup

將前面的相應(yīng)等式帶入可得:

Tsetup_magrin = Tcycle + Tco_clka + Tflt_clka – Tjitter – Tco_clkb – Tflt_clkb – Tco_data – Tflt_data – Tsetup

我們定義時(shí)鐘驅(qū)動(dòng)器(PLL)的兩個(gè)時(shí)鐘輸出之間的偏移為Tclock_Skew ,兩根CLOCK走線之間的時(shí)鐘偏移為TPCB_Skew ,即:

Tclock_Skew = Tco_clkb - Tco_clka;

TPCB_Skew = Tflt_clkb - Tflt_clka

這樣就可以得到建立時(shí)間裕量的標(biāo)準(zhǔn)計(jì)算公式:

Tsetup_magrin =Tcycle – TPCB_skew –Tclock_skew –Tjitter – Tco_ data -Tflt_data-Tsetup (1.6.1)

再來(lái)看保持時(shí)間環(huán):

對(duì)照上圖,我們可以同樣的進(jìn)行分析:

Tdata_delay = Tco_clkb + Tflt_clkb + Tco_data + Tflt_data

Tclock delay = Tco_clka + Tflt_clka

于是可以得出保持時(shí)間裕量的計(jì)算公式:

Thold margin = Tdata_delay – Tclock_dalay – Thold_time

即: Thold margin = Tco_data + Tflt_data + Tclock_skew + Tpcb_skew – Thold (1.6.2)

可以看到,式1.6.2中不包含時(shí)鐘抖動(dòng)Jitter的參數(shù)。這是因?yàn)镴itter是指時(shí)鐘周期間(Cycle to Cycle)的誤差,而保持時(shí)間的計(jì)算和時(shí)鐘周期無(wú)關(guān)。

對(duì)于任何時(shí)鐘控制系統(tǒng),如果要能保證正常工作,就必須使建立時(shí)間余量和保持時(shí)間裕量都至少大于零,即Tsetup marin 》0;Thold margin 》0,將公式1.6.1和1.6.2分別帶入就可以得到普通時(shí)鐘系統(tǒng)的時(shí)序約束條件不等式:

TPCB_skew +Tclock_skew +Tjitter + Tco_data + Tflt_data+Tsetup《 Tcycle (1.6.3)

Tco_data + Tflt_data + Tclock_skew + Tpcb_skew 》 Thold (1.6.4)

需要注意的是:

1. 數(shù)據(jù)在發(fā)送端的內(nèi)部延時(shí)Tco_data可以從芯片的datasheet查到,這個(gè)值是一個(gè)范圍,在式1.6.3中取最大值,在式1.6.4中取最小值。

2.?dāng)?shù)據(jù)在傳輸線上的飛行時(shí)間Tflt_data在實(shí)際計(jì)算中應(yīng)該取最大/最小飛行時(shí)間參數(shù),在式1.6.3中取最大飛行時(shí)間,在式1.6.4中取最小飛行時(shí)間。

3. 時(shí)鐘的偏移TPCB_skew和Tclock_skew也是一個(gè)變化的不確定參數(shù),一般為+/-N ps,同樣,在建立時(shí)間約束條件1.6.3中取+Nps,而在保持時(shí)間約束條件1.6.4中取-Nps。

從上面的分析可以看到,對(duì)于PCB設(shè)計(jì)工程師來(lái)說(shuō),保證足夠穩(wěn)定的系統(tǒng)時(shí)序最有效的途徑就是盡量減小PCB skew和信號(hào)傳輸?shù)娘w行時(shí)間,而其它的參數(shù)都只和芯片本身的性能有關(guān)。實(shí)際中經(jīng)常采取的措施就是嚴(yán)格控制時(shí)鐘和數(shù)據(jù)的走線長(zhǎng)度,調(diào)整合理的拓補(bǔ)結(jié)構(gòu),并盡可能減少信號(hào)完整性帶來(lái)的影響。然而,即便我們已經(jīng)考慮的很周全,普通時(shí)鐘系統(tǒng)的本身的設(shè)計(jì)瓶頸始終是無(wú)法打破的,也就是建立時(shí)間的約束,我們?cè)诒M可能減少由PCB布線引起的信號(hào)延遲之外,器件本身的特性如Tco、Jitter、TSetup等等將成為最主要的制約因素,盡管我們可以通過(guò)提高工藝水平和電路設(shè)計(jì)技術(shù)來(lái)不斷提高數(shù)字器件的性能,但得到的效果也僅僅是在一定范圍之內(nèi)提升了系統(tǒng)的主頻,在頻率超過(guò)300MHz的情況下,我們將不得不放棄使用這種普通時(shí)鐘系統(tǒng)設(shè)計(jì)。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605727 -

pll

+關(guān)注

關(guān)注

6文章

781瀏覽量

135301 -

時(shí)序圖

+關(guān)注

關(guān)注

2文章

58瀏覽量

22484 -

時(shí)鐘驅(qū)動(dòng)器

+關(guān)注

關(guān)注

0文章

34瀏覽量

13880

原文標(biāo)題:FPGA知識(shí)匯集-FPGA系統(tǒng)時(shí)序理論

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA的IO口時(shí)序約束分析

FPGA知識(shí)匯集-FPGA時(shí)序基礎(chǔ)理論

FPGA時(shí)序約束的基礎(chǔ)知識(shí)

FPGA I/O口時(shí)序約束講解

FPGA時(shí)序分析

FPGA實(shí)戰(zhàn)演練邏輯篇48:基本的時(shí)序分析理論1

FPGA時(shí)序約束--基礎(chǔ)理論篇

FPGA設(shè)計(jì):時(shí)序是關(guān)鍵

FPGA中的時(shí)序約束設(shè)計(jì)

FPGA時(shí)序約束的理論基礎(chǔ)知識(shí)說(shuō)明

時(shí)序約束系列之D觸發(fā)器原理和FPGA時(shí)序結(jié)構(gòu)

FPGA知識(shí)匯集-源同步時(shí)序系統(tǒng)

FPGA設(shè)計(jì)-時(shí)序約束(理論篇)

FPGA知識(shí)匯集-FPGA系統(tǒng)時(shí)序理論

FPGA知識(shí)匯集-FPGA系統(tǒng)時(shí)序理論

評(píng)論