作者:Abhilasha Kawle and Roberto Maurino

在本文中,我們將重點(diǎn)介紹新型連續(xù)時(shí)間Σ-Δ(CTSD)精密ADC最重要的架構(gòu)特征之一:易于驅(qū)動(dòng)的阻性輸入和基準(zhǔn)電壓源。實(shí)現(xiàn)最佳信號(hào)鏈性能的關(guān)鍵是確保輸入源或基準(zhǔn)電壓源本身在與ADC接口時(shí)不會(huì)損壞。對(duì)于傳統(tǒng)ADC,需要復(fù)雜的信號(hào)條件電路設(shè)計(jì)(稱為前端設(shè)計(jì))來(lái)實(shí)現(xiàn)ADC的輸入和基準(zhǔn)電壓源的無(wú)縫接口。CTSD ADC獨(dú)特的架構(gòu)特性使該ADC與輸入和基準(zhǔn)電壓源的接口方式得以簡(jiǎn)化和創(chuàng)新。首先,讓我們快速回顧一下傳統(tǒng)的ADC前端設(shè)計(jì)。

傳統(tǒng)ADC的前端設(shè)計(jì)

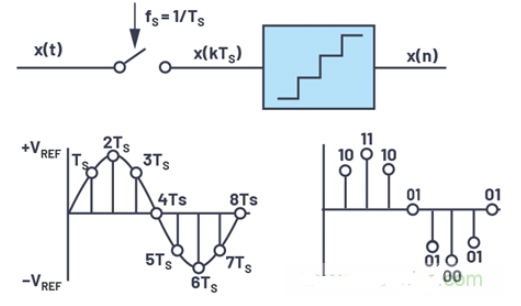

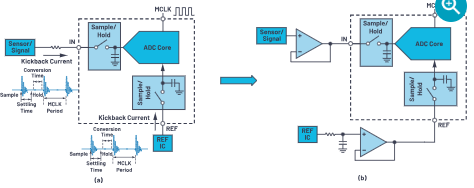

在本文中,我們將交替使用術(shù)語(yǔ)“傳感器”或“輸入信號(hào)”來(lái)表示ADC信號(hào)鏈的任何類型的電壓輸入。ADC信號(hào)鏈的輸入信號(hào)可以是傳感器、來(lái)自某個(gè)源的信號(hào)或控制環(huán)路的反饋。眾所周知,在傳統(tǒng)的離散時(shí)間Σ-Δ(DTSD)ADC和逐次逼近寄存器(SAR)ADC中,輸入和基準(zhǔn)電壓源處的采樣網(wǎng)絡(luò)是開(kāi)關(guān)電容負(fù)載。當(dāng)開(kāi)關(guān)導(dǎo)通時(shí),電容器向輸入充電,當(dāng)開(kāi)關(guān)關(guān)閉時(shí),電容器保持采樣值。在每個(gè)采樣時(shí)鐘邊沿,當(dāng)開(kāi)關(guān)將電容重新連接到輸入端時(shí),需要一種稱為反沖電流的有限電流,將電容充電或放電至新的采樣值。電流曲線如圖1a所示。大多數(shù)傳感器和基準(zhǔn)電壓源IC都無(wú)法驅(qū)動(dòng)如此大的反沖電流,如果直接與ADC接口,輸入信號(hào)或基準(zhǔn)電壓源損壞的可能性很高。避免這種損壞的已知解決方案之一是使用驅(qū)動(dòng)緩沖放大器將輸入傳感器和基準(zhǔn)電壓源與ADC隔離。驅(qū)動(dòng)放大器應(yīng)能夠吸收這些反沖電流,如圖1b所示。這就需要高壓擺率和高帶寬放大器,以支持所需的輸入充電/放電電流,并在一個(gè)采樣時(shí)間段內(nèi)建立反沖。這些嚴(yán)格的要求限制了傳統(tǒng)ADC可用于輸入和基準(zhǔn)電壓源路徑的緩沖放大器的選擇。

圖1.(a) 傳統(tǒng)ADC輸入和基準(zhǔn)電壓源上的反沖電流,以及(b)輸入和基準(zhǔn)電壓源上的緩沖器對(duì)反沖電流的隔離。

另一方面,輸入端需要低通抗混疊濾波器,以確保高頻噪聲和干擾源嚴(yán)重衰減,以便當(dāng)它們因采樣到目標(biāo)頻帶而折返時(shí),性能不會(huì)下降。現(xiàn)有ADC信號(hào)鏈設(shè)計(jì)人員面臨的挑戰(zhàn)是微調(diào)混疊抑制和輸出建立的相反要求。DTSD ADC的前端設(shè)計(jì)帶有驅(qū)動(dòng)器和抗混疊濾波器,如圖2所示。

輸入路徑由儀表放大器(儀表放大器)組成,該儀表放大器將傳感器連接到全差分放大器(FDA),最終驅(qū)動(dòng)ADC。儀表放大器將輸入傳感器環(huán)境與ADC電路隔離開(kāi)來(lái)。例如,傳感器的共模(CM)信號(hào)可能非常高,高達(dá)10伏。但大多數(shù)FDA和ADC不支持這種高輸入共模電壓。通用儀表放大器能夠支持寬輸入共模,同時(shí)提供適合FDA和ADC的輸出共模。儀表放大器的另一個(gè)優(yōu)點(diǎn)是它具有高輸入阻抗。這意味著,如果傳感器不能直接驅(qū)動(dòng)FDA的輸入電阻,則可以使用儀表放大器將傳感器與FDA連接。FDA本身需要高帶寬和壓擺率,以實(shí)現(xiàn)更快的輸出建立。干擾源抗擾度所需的有源抗混疊濾波器(AAF)圍繞FDA構(gòu)建。

輸入或基準(zhǔn)電壓源的驅(qū)動(dòng)器具有相互沖突的要求:一方面,建立需要高帶寬,但另一方面,需要低帶寬來(lái)濾除噪聲和干擾源。在基準(zhǔn)路徑上,DTSD ADC信號(hào)鏈的前端設(shè)計(jì)如圖2所示,該基準(zhǔn)電壓源IC連接到驅(qū)動(dòng)ADC基準(zhǔn)負(fù)載的緩沖器。它還包括一個(gè)噪聲濾波器,可將基準(zhǔn)電壓源IC和緩沖器的噪聲切斷到特定頻率以上。此濾波器的設(shè)計(jì)要求將在后面的部分中討論。基準(zhǔn)電壓緩沖器具有高帶寬和壓擺率要求,以便更快地建立采樣事件干擾。

本系列的第1部分證明,使用精密CTSD ADC的新信號(hào)鏈可能比傳統(tǒng)ADC的復(fù)雜信號(hào)鏈小68%。這種尺寸減小降低了BOM,簡(jiǎn)單性有助于信號(hào)鏈設(shè)計(jì)人員加快上市時(shí)間。

CTSD ADC 的優(yōu)勢(shì):阻性輸入和基準(zhǔn)電壓源

在第2部分中,向信號(hào)鏈設(shè)計(jì)人員介紹了CTSD ADC架構(gòu),采用非常規(guī)的反相閉環(huán)放大器方法。如第2部分所述,CTSD ADC可以設(shè)想為具有阻性輸入和基準(zhǔn)負(fù)載的Σ-Δ型ADC。輸入和基準(zhǔn)結(jié)構(gòu)是一個(gè)簡(jiǎn)單的阻性負(fù)載,這意味著沒(méi)有高帶寬或高壓擺率驅(qū)動(dòng)要求。第3部分展示了CTSD的獨(dú)特優(yōu)勢(shì),由于其固有的混疊抑制,CTSD具有抗干擾能力。在傳統(tǒng)的信號(hào)鏈設(shè)計(jì)中,衰減干擾源所需的外部混疊抑制濾波器是一個(gè)額外的挑戰(zhàn),而CTSD ADC不需要外部AAF。由于CTSD ADC固有的混疊抑制特性,調(diào)制器環(huán)路的信號(hào)傳遞函數(shù)相當(dāng)于衰減高頻干擾的抗混疊濾波器。由于采用阻性輸入和固有的AAF,簡(jiǎn)化了輸入網(wǎng)絡(luò),傳感器可以直接連接到ADC。在傳感器可能不具備驅(qū)動(dòng)這種阻性負(fù)載的能力的情況下,可以使用儀表放大器將傳感器連接到ADC。同樣,在基準(zhǔn)電壓源側(cè),由于阻性負(fù)載,CTSD ADC信號(hào)鏈中消除了基準(zhǔn)電壓緩沖器。帶儀表放大器的簡(jiǎn)化原理圖如圖3b所示。

圖2.離散時(shí)間Σ-Δ型ADC的前端設(shè)計(jì)。

圖3.(a) CTSD 架構(gòu)提供阻性輸入和基準(zhǔn)負(fù)載,以及 (b) 直接儀表放大器,基準(zhǔn)電壓源驅(qū)動(dòng) CTSD ADC。

圖4.(a) DTSD ADC 的輸入電流反沖,以及 (b) CTSD ADC 的連續(xù)輸入電流曲線。

圖4顯示了對(duì)CTSD ADC如何幫助簡(jiǎn)化輸入前端設(shè)計(jì)的進(jìn)一步支持。對(duì)于DTSD ADC,當(dāng)輸入采樣開(kāi)關(guān)改變狀態(tài)時(shí),由于反沖而導(dǎo)致的輸入電流不連續(xù)性明顯可見(jiàn)。使用CTSD ADC,觀察到輸入電流是連續(xù)的,從而保持信號(hào)連續(xù)性。

簡(jiǎn)化的輸入驅(qū)動(dòng)設(shè)計(jì)

我們已經(jīng)確定CTSD ADC的輸入驅(qū)動(dòng)是阻性的。本節(jié)將討論輸入阻抗R的值在規(guī)劃ADC的輸入驅(qū)動(dòng)。R在是ADC指定的噪聲性能的函數(shù)。例如,AD4134是一款精密CTSD ADC,動(dòng)態(tài)范圍為108 dB,基準(zhǔn)電壓源為4 V,輸入阻抗為6 kΩ差分。這表明,當(dāng)滿量程8 V p-p差分輸入信號(hào)施加到ADC時(shí),峰值電流要求為1.3 mA p-p。如果傳感器可以支持輸入電流V在/R在,然后可以直接連接到ADC。需要一個(gè)簡(jiǎn)單的放大器來(lái)驅(qū)動(dòng)這種阻性負(fù)載的情況是:

當(dāng)傳感器不具備驅(qū)動(dòng)能力以提供 V 峰值電流時(shí)在/R在.

信號(hào)鏈設(shè)計(jì)要求傳感器輸出需要增益或衰減。

將輸入傳感器環(huán)境與ADC電路隔離。

傳感器具有較大的輸出阻抗。

傳感器遠(yuǎn)離ADC,走線可能會(huì)給輸入增加很大的電阻。

在場(chǎng)景 4 和 5 中,額外的外部電阻 R 兩端會(huì)出現(xiàn)壓降s,表示ADC輸入端的信號(hào)丟失。這會(huì)導(dǎo)致信號(hào)鏈的增益誤差和誤差隨溫度的漂移,從而導(dǎo)致性能下降。溫度增益漂移是由外部電阻和內(nèi)部電阻的不同溫度系數(shù)引起的。這個(gè)問(wèn)題可以通過(guò)一個(gè)簡(jiǎn)單的放大器來(lái)解決,以隔離額外的外部電阻。由于該放大器的驅(qū)動(dòng)負(fù)載是阻性的,因此該放大器的選擇標(biāo)準(zhǔn)為:

輸入阻抗:為避免信號(hào)衰減或丟失,傳感器的阻抗應(yīng)與放大器輸入阻抗相匹配。

輸出阻抗:輸出阻抗應(yīng)足以驅(qū)動(dòng)ADC的阻性輸入負(fù)載。

輸出類型:作為一般信號(hào)鏈設(shè)計(jì)準(zhǔn)則,建議采用差分信號(hào)策略以獲得最佳信號(hào)鏈性能。差分輸出型放大器或單端至差分輸出的設(shè)計(jì)技術(shù)最適合此任務(wù)。此外,為了獲得最佳性能,最好將此差分信號(hào)的共模設(shè)置為 V裁判/2.

可編程增益:輸入信號(hào)通常被增益或衰減,以將其映射到ADC的滿量程范圍。這是因?yàn)楫?dāng)使用ADC的整個(gè)輸入范圍時(shí),可以從ADC信號(hào)鏈獲得最大性能。

根據(jù)應(yīng)用的不同,該放大器可以是儀表放大器或FDA,也可以是構(gòu)成差分輸出放大器的兩個(gè)單端運(yùn)算放大器的組合。由于沒(méi)有高壓擺率或高帶寬的嚴(yán)格要求,ADI的放大器產(chǎn)品組合有多種選擇,可根據(jù)應(yīng)用要求驅(qū)動(dòng)該CTSD ADC。此外,放大器性能參數(shù)通常由阻性負(fù)載指定,這使得選擇更加簡(jiǎn)單。

例如,對(duì)于AD4134,LTC6373是具有可編程增益選項(xiàng)和全差分輸出的性能兼容型儀表放大器的一個(gè)選項(xiàng)。該儀表放大器為輸入源提供高阻抗,可輕松驅(qū)動(dòng)差分6 kΩ阻抗,噪聲和線性度性能與ADC相當(dāng)。憑借其廣泛的輸入共模支持和可編程增益選項(xiàng),任何具有寬信號(hào)幅度范圍的傳感器或輸入信號(hào)都可以與ADC接口。采用這種直接儀表放大器驅(qū)動(dòng)器的輸入前端設(shè)計(jì)示例如圖4所示。

圖5.輸入前端設(shè)計(jì),CTSD ADC 直接連接到儀表放大器。

另一個(gè)例子是采用全差分驅(qū)動(dòng)器放大器(如 LTC6363-0.5 / LTC6363-1 / LTC6363-2)的低電壓簡(jiǎn)單前端設(shè)計(jì),基于所需的增益或衰減,如圖 6 所示。可以使用 FDA 的情況是,傳感器能夠驅(qū)動(dòng) FDA 的阻性負(fù)載,但為單端類型,或者具有 ADC 不支持的共模,或者信號(hào)鏈中的增益/衰減要求很小。

圖6.輸入前端設(shè)計(jì),CTSD ADC直接連接到全差分放大器。

另一個(gè)示例包括一個(gè)低BOM選項(xiàng),用于使用兩個(gè)單端運(yùn)算放大器在ADC上將單端輸入轉(zhuǎn)換為全差分信號(hào),如圖7所示。

圖7.輸入前端設(shè)計(jì),帶有一個(gè)帶有兩個(gè)單端放大器的CTSD ADC。

還有許多其他例子,例如使用單端儀表放大器和單端運(yùn)算放大器的組合來(lái)構(gòu)建差分輸出前端,用于非常高的輸入CM或低驅(qū)動(dòng)強(qiáng)度的單端型傳感器。可以根據(jù)性能、面積和 BOM 要求選擇任何此類組合,以更好地適應(yīng)應(yīng)用。

與AD4134兼容的其他放大器列表包括:

運(yùn)算放大器:ADA4625-2、ADA4610-2、AD8605和ADA4075-2。

全差分放大器:ADA4940-2、LTC6363 和 ADA4945-1。

儀表放大器:AD8421。

ADI公司的放大器選擇指南可用于選擇適合應(yīng)用的最佳放大器。例如,對(duì)于音頻測(cè)試設(shè)備等高線性度應(yīng)用,建議使用ADA4945-1。對(duì)于光電二極管應(yīng)用,最重要的考慮因素是非常高的輸入阻抗,可以使用ADA4610-2等跨阻放大器(TIA)。

CTSD ADC大大簡(jiǎn)化了輸入前端,讓我們來(lái)看看參考驅(qū)動(dòng)器的類似簡(jiǎn)化。

簡(jiǎn)化的參考設(shè)計(jì)

ADC輸出表示其輸入和基準(zhǔn)電壓源,如公式1所示。

其中 V在= 輸入電壓電平,VREF模數(shù)轉(zhuǎn)換器= ADC 的基準(zhǔn)電壓源,N = 位數(shù),D外= ADC 數(shù)字輸出。

公式1表明,為了獲得最佳ADC性能,干凈、無(wú)損壞的基準(zhǔn)電壓源非常重要。受基準(zhǔn)電壓源誤差影響的ADC信號(hào)鏈的三個(gè)主要性能指標(biāo)是:

信噪比:影響SNR的主要噪聲因素是輸入路徑、ADC本身和基準(zhǔn)電壓源。對(duì)于ADC輸出端的目標(biāo)總噪聲(考慮其他噪聲貢獻(xiàn)因素),基準(zhǔn)噪聲的預(yù)算通常為獨(dú)立ADC輸出噪聲的1/3或1/4。基準(zhǔn)電壓源或基準(zhǔn)電壓緩沖器的噪聲通常高于ADC。如果我們查看任何數(shù)據(jù)手冊(cè),了解基準(zhǔn)電壓源或基準(zhǔn)電壓緩沖器IC、頻譜噪聲密度或噪聲密度,是規(guī)范之一。如果我們重新審視噪聲計(jì)算基礎(chǔ)知識(shí),則基準(zhǔn)電壓源或基準(zhǔn)電壓緩沖器輸出端的總噪聲由下式

給出 我們無(wú)法控制噪聲

密度因?yàn)樗鼘?duì)于所選的引用或緩沖區(qū)是固定的。唯一可控的參數(shù)是噪聲帶寬(NBW)。為了達(dá)到低基準(zhǔn)電壓源噪聲,我們降低了基準(zhǔn)電壓源或基準(zhǔn)電壓緩沖器的噪聲帶寬。這通常通過(guò)將一階低通RC濾波器連接到ADC來(lái)完成,如圖8所示。對(duì)于一階RC濾波器,NBW由

ADC基準(zhǔn)電流I

模數(shù)轉(zhuǎn)換器,流過(guò)濾波電阻R會(huì)導(dǎo)致壓降,從而改變ADC的實(shí)際基準(zhǔn)值。因此,建議選擇較小的R值和較大的C值,以滿足NBW對(duì)低參考噪聲的要求。

增益誤差:從公式1中可以明顯看出,VREF是模數(shù)轉(zhuǎn)換器確定輸出到輸入傳遞函數(shù)的斜率,就像在直線方程中一樣,例如 y = mx。該斜率也稱為ADC的增益。因此,如果基準(zhǔn)電壓源發(fā)生變化,ADC的增益也會(huì)發(fā)生變化。

線性:對(duì)于傳統(tǒng)的DTSD ADC和SAR ADC,基準(zhǔn)電流和伴隨的反沖取決于輸入信號(hào)。因此,如果基準(zhǔn)電壓源在下一個(gè)采樣時(shí)鐘邊沿之前沒(méi)有完全建立,則基準(zhǔn)電壓源上的誤差將取決于輸入并導(dǎo)致非線性。在數(shù)學(xué)上,VREF模數(shù)轉(zhuǎn)換器然后表示為

參考公式1,ADC輸出D

外將具有基于ADC輸入的各種高階依賴性,這種依賴性會(huì)導(dǎo)致諧波和積分非線性。因此,對(duì)于傳統(tǒng)ADC,很難要求基準(zhǔn)電壓緩沖器的高壓擺率和帶寬在采樣時(shí)間段內(nèi)建立基準(zhǔn)電壓輸出。

如果我們仔細(xì)分析SNR和線性度,就會(huì)發(fā)現(xiàn)基準(zhǔn)電壓源或基準(zhǔn)電壓源緩沖器需要滿足相當(dāng)相互沖突的要求。噪聲的帶寬要求較低,而建立速度較快的帶寬要求較高。調(diào)整這兩個(gè)要求之間的精細(xì)平衡一直是信號(hào)鏈設(shè)計(jì)人員面臨的一個(gè)由來(lái)已久的挑戰(zhàn)。一些最新的DTSD ADC和SAR ADC片內(nèi)集成了基準(zhǔn)電壓緩沖器,以簡(jiǎn)化信號(hào)鏈設(shè)計(jì)的一個(gè)步驟,但這些解決方案需要額外的功率或會(huì)帶來(lái)一定的性能損失。由于CTSD ADC不需要快速建立緩沖器,并且具有阻性輸入,無(wú)需快速建立驅(qū)動(dòng)器,因此能夠避免這些性能問(wèn)題。

CTSD ADC 通過(guò)以下特性和設(shè)計(jì)改進(jìn)解決了參考驅(qū)動(dòng)器挑戰(zhàn):

當(dāng)阻性負(fù)載在基準(zhǔn)上時(shí),每個(gè)采樣時(shí)鐘邊沿都沒(méi)有建立要求。這允許設(shè)計(jì)人員將基準(zhǔn)電壓源IC直接連接到ADC,而無(wú)需專用基準(zhǔn)電壓緩沖器。

專利設(shè)計(jì)技術(shù)使基準(zhǔn)電流獨(dú)立于輸入,并強(qiáng)制ADC的基準(zhǔn)電流I模數(shù)轉(zhuǎn)換器基本恒定。當(dāng)可能需要RC濾波器來(lái)降低基準(zhǔn)噪聲時(shí),這是有益的,如圖8所示。結(jié)果是電阻兩端的壓降恒定,VREF中沒(méi)有增加輸入相關(guān)項(xiàng)模數(shù)轉(zhuǎn)換器.設(shè)計(jì)用于根據(jù)R值和基準(zhǔn)引腳處測(cè)得的電壓,在系統(tǒng)級(jí)對(duì)增益誤差進(jìn)行數(shù)字校正。因此,這個(gè)簡(jiǎn)單的參考接口不會(huì)有增益或線性誤差。

圖8.阻性基準(zhǔn)負(fù)載,可通過(guò)無(wú)源濾波器直接連接到基準(zhǔn) IC。

盡管已經(jīng)實(shí)施了一項(xiàng)規(guī)定,以數(shù)字方式校正R兩端壓降引起的誤差,但人們可能想知道這是否會(huì)限制CTSD ADC作為實(shí)際基準(zhǔn)電壓源(VREF模數(shù)轉(zhuǎn)換器) 的 ADC 將小于應(yīng)用的 VREF。

例如,如果基準(zhǔn)電壓源IC的VREF經(jīng)過(guò)修整并設(shè)置為4.096 V,ADC基準(zhǔn)電流(I模數(shù)轉(zhuǎn)換器) = 6 mA,則,對(duì)于R = 20 Ω的濾波器電阻,ADC的實(shí)際基準(zhǔn)電壓源(VREF模數(shù)轉(zhuǎn)換器) 為 3.967 V。如公式5所示。在這種情況下,在這種情況下,當(dāng)規(guī)格V p-p(其大于2 × VREF模數(shù)轉(zhuǎn)換器) 施加在 ADC 的輸入端,是否有可能使 ADC 的輸出飽和?答案是否定的。CTSD ADC 設(shè)計(jì)用于支持 ADC 引腳 REFIN 處超出基準(zhǔn)電壓源幾 mV 的輸入幅度。在我們的AD4134示例中,這種擴(kuò)展范圍將電阻值限制為最大值25Ω。然后選擇噪聲濾波器的C值以滿足計(jì)算的噪聲帶寬。

簡(jiǎn)化參考驅(qū)動(dòng)器設(shè)計(jì)

CTSD ADC簡(jiǎn)化了基準(zhǔn)電壓源驅(qū)動(dòng)的設(shè)計(jì),但在為濾波器選擇正確的R,然后對(duì)電阻兩端的壓降進(jìn)行數(shù)字增益誤差校正時(shí),還需要考慮其他因素。數(shù)字增益誤差校正(也稱為校準(zhǔn))是許多ADC的常見(jiàn)特性,它使信號(hào)鏈設(shè)計(jì)人員能夠自由地補(bǔ)償ADC數(shù)字輸出端信號(hào)鏈中的誤差。因此,它可能不需要增加設(shè)計(jì)步驟,而是重復(fù)使用相同的算法,這在許多信號(hào)鏈中很常見(jiàn)。從表面上看,電阻的選擇似乎并不是一個(gè)特別復(fù)雜的設(shè)計(jì)步驟,但有一個(gè)警告:壓降的溫度依賴性。外部濾波電阻和I模數(shù)轉(zhuǎn)換器隨溫度漂移不同,進(jìn)而導(dǎo)致 VREF模數(shù)轉(zhuǎn)換器以及ADC的增益隨溫度漂移。對(duì)于具有嚴(yán)格增益漂移要求的應(yīng)用,粗略的解決方案包括定期校準(zhǔn)信號(hào)鏈。但是,由于CTSD技術(shù),一個(gè)更好和創(chuàng)新的解決方案成為可能。由于ADC基準(zhǔn)負(fù)載電流是片內(nèi)所用電阻材料的常數(shù)和函數(shù),因此可以在片內(nèi)為濾波電阻R提供20 Ω,如圖9所示。

圖9.片內(nèi)基準(zhǔn)噪聲濾波器電阻,簡(jiǎn)化了CTSD ADC的基準(zhǔn)前端設(shè)計(jì)。

在新的前端設(shè)計(jì)中,基準(zhǔn)IC連接在REFIN引腳上,濾波電容連接在REFCAP引腳上,形成基準(zhǔn)IC噪聲的噪聲濾波器。由于片上電阻R和I的電阻模數(shù)轉(zhuǎn)換器兩種功能都是同一電阻材料,REFCAP 上沒(méi)有溫度漂移 (VREF模數(shù)轉(zhuǎn)換器).AD4134還采用獲得專利的片內(nèi)基準(zhǔn)電壓源校正算法,對(duì)片內(nèi)電阻兩端的壓降進(jìn)行數(shù)字自校準(zhǔn)。因此,參考驅(qū)動(dòng)器設(shè)計(jì)現(xiàn)在簡(jiǎn)化為根據(jù)性能要求選擇基準(zhǔn)IC和電容值。

ADR444是低噪聲基準(zhǔn)電壓源IC之一,可用作CTSD ADC的配套產(chǎn)品。AD4134的數(shù)據(jù)手冊(cè)提供了有關(guān)電容值選擇以及內(nèi)部和外部數(shù)字增益校準(zhǔn)的更多詳細(xì)信息。

結(jié)論

CTSD ADC消除了實(shí)現(xiàn)最佳精密性能和簡(jiǎn)化前端設(shè)計(jì)的許多障礙。在接下來(lái)的文章中,我們將介紹如何將CTSD ADC調(diào)制器內(nèi)核的輸出處理成最終的數(shù)字輸出格式,以供外部數(shù)字控制器使用,以實(shí)現(xiàn)最佳處理。根據(jù)本系列中解釋的Σ-Δ基礎(chǔ)知識(shí),我們知道調(diào)制器輸出不能直接處理,因?yàn)樗牟蓸铀俾室叩枚唷P枰獙⒉蓸铀俾式档偷綉?yīng)用所需的輸出數(shù)據(jù)速率(ODR)。接下來(lái),我們將介紹一種新穎的異步采樣速率轉(zhuǎn)換(ASRC)技術(shù),使信號(hào)鏈設(shè)計(jì)人員能夠在任何所需的ODR下調(diào)整最終ADC輸出,并超越將ODR限制為采樣頻率倍數(shù)的古老限制。

審核編輯:郭婷

-

傳感器

+關(guān)注

關(guān)注

2559文章

52048瀏覽量

760710 -

放大器

+關(guān)注

關(guān)注

145文章

13972瀏覽量

215461 -

adc

+關(guān)注

關(guān)注

99文章

6601瀏覽量

547508

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何使用連續(xù)時(shí)間Σ-ΔADC,簡(jiǎn)化信號(hào)鏈來(lái)解決采樣問(wèn)題

CTSD精密ADC—第4部分:輕松驅(qū)動(dòng)ADC輸入和基準(zhǔn)電壓源,簡(jiǎn)化信號(hào)鏈設(shè)計(jì)

轉(zhuǎn)換器簡(jiǎn)化RF信號(hào)鏈-汽車(chē)收音機(jī)的演變歷程

驅(qū)動(dòng)ADC輸入時(shí)簡(jiǎn)化設(shè)計(jì)流程的方法

高速轉(zhuǎn)換器如何簡(jiǎn)化RF信號(hào)鏈?

AD8275 ADC驅(qū)動(dòng)器,具有電平轉(zhuǎn)換功能,可簡(jiǎn)化信號(hào)調(diào)理

簡(jiǎn)化RF組件評(píng)估和信號(hào)鏈設(shè)計(jì)

緩沖的 8 通道 ADC 輸入簡(jiǎn)化了傳感器接口

具 Easy Drive 輸入電流消除功能的 24 位、16 通道增量累加 ADC 簡(jiǎn)化前端信號(hào)調(diào)節(jié)

DN400 - 真正的軌至軌,高輸入阻抗 ADC 簡(jiǎn)化了精準(zhǔn)測(cè)量

固定增益差分放大器簡(jiǎn)化對(duì)高速 ADC 的驅(qū)動(dòng)

LTC2480 - 采用 Easy Drive 輸入電流消除技術(shù)的 16 至 24 位 ?∑ ADC 系列簡(jiǎn)化前端信號(hào)調(diào)節(jié)

帶Sequencer的DN274-12位ADC簡(jiǎn)化了多輸入應(yīng)用

CTSD精密ADC:輕松驅(qū)動(dòng)ADC輸入和基準(zhǔn)電壓源,簡(jiǎn)化信號(hào)鏈設(shè)計(jì)

利用ADS125H02簡(jiǎn)化±10V PLC模擬輸入模塊信號(hào)鏈

評(píng)論