電子發(fā)燒友網(wǎng)報道(文/李寧遠)I2C作為一種簡單的雙向二線制同步串行總線,已經(jīng)為人們所熟知,在信息傳輸領(lǐng)域有著不少應(yīng)用。此前大家對I2C的印象是結(jié)合了SPI和UART的優(yōu)點,但隨著應(yīng)用的發(fā)展,I2C速率低、功耗大的短板日趨明顯,這時就需要新的升級版的總線協(xié)議來接棒。

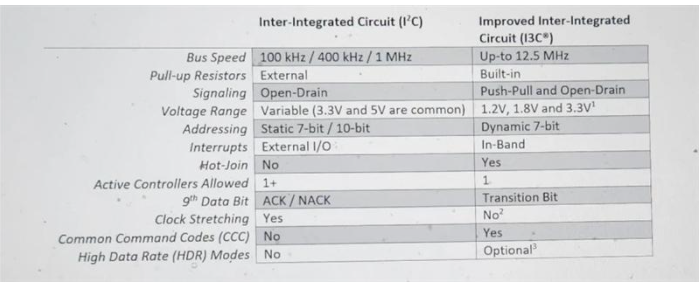

I3C,全稱Improved Inter Integrated Circuit,作為I2C的升級版接過了這個I2C手中的接力棒。I3C整合并統(tǒng)一了I2C和SPI的關(guān)鍵屬性,同時通過全面、可擴展的接口和體系結(jié)構(gòu)改進每種方法的功能和性能。該規(guī)范還預(yù)測了未來移動、移動影響和嵌入式系統(tǒng)行業(yè)所需的傳感器接口架構(gòu)。

I3C,升級版I2C

在過去的幾十年里,I2C的廣泛應(yīng)用可以說是有目共睹,但是其本身也有著兩個避不開的缺點,一是速率受限,二是功耗偏大。此前也有不少SPI代替I2C的做法,但是SPI本身應(yīng)用比較寬泛,最終也沒能替代I2C。隨著移動設(shè)備上傳感器數(shù)量的增加,總線上數(shù)據(jù)量開始膨脹,I2C的瓶頸越來越明顯。為了提升I2C的性能,早在2013年,MIPI聯(lián)盟傳感器接口工作組就啟動了基于I2C的需求升級。

I3C作為I2C的升級版,在使用功率和性能方面有重大改進,同時速率也升級到可以替代SPI的中速,相當(dāng)于SPI 30MHz下的速率。I3C規(guī)范的主要制定者包括NXP,Qualcomm,Intel,還有Invensense,TI,STM,Synopsys,Cadence,Mentor,Sony,Knowles,Lattice這些提供助力的廠商。

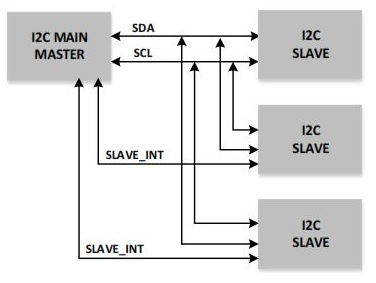

眾所周知I2C是兩根線,但是它的中斷腳、使能腳等等都要通過GPIO連到SoC上,隨著傳感器數(shù)量的增加,使用I2C只能不斷增加GPIO。I3C將這些中斷做成了內(nèi)置,可以幫SoC省去很多GPIO。I3C也是向后兼容I2C,I2C可以平穩(wěn)地過渡到I3C。這一升級有效助力了智能手機、可穿戴設(shè)備、物聯(lián)網(wǎng)設(shè)備、增強現(xiàn)實/虛擬現(xiàn)實和汽車系統(tǒng)實現(xiàn)更多設(shè)計創(chuàng)新。

I3C優(yōu)勢與應(yīng)用場景在哪里

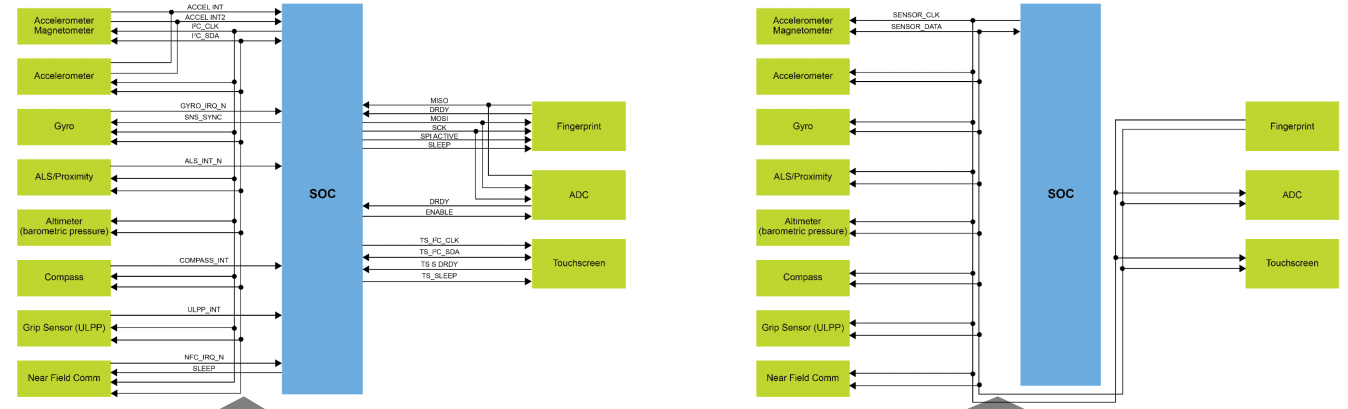

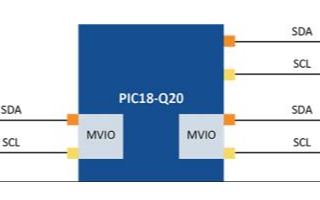

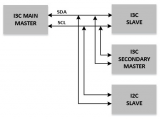

I2C與I3C傳感器接口框圖對比,NXP

從上圖I2C與I3C傳感器接口框圖對比可以很明顯地看到,雖然I2C說是只有時鐘線數(shù)據(jù)線,但是還需要很多額外的從線連到SoC上,GPIO數(shù)量的增加以添加SoC包引腳和PCB層計數(shù)的形式增加了系統(tǒng)成本,相比之下I3C的布線情況就簡潔很多,只需要兩根信號線即可,可以顯著縮小SoC尺寸。

至于功耗,眾所周知I2C的兩根線SCL和SDA都是需要接上拉電阻的,上拉電阻的存在導(dǎo)致了I2C功耗會比較大,I3C的SCL全程采用推挽,SDA大部分時間也在推挽模式下工作,因此功耗會降低很大一部分。

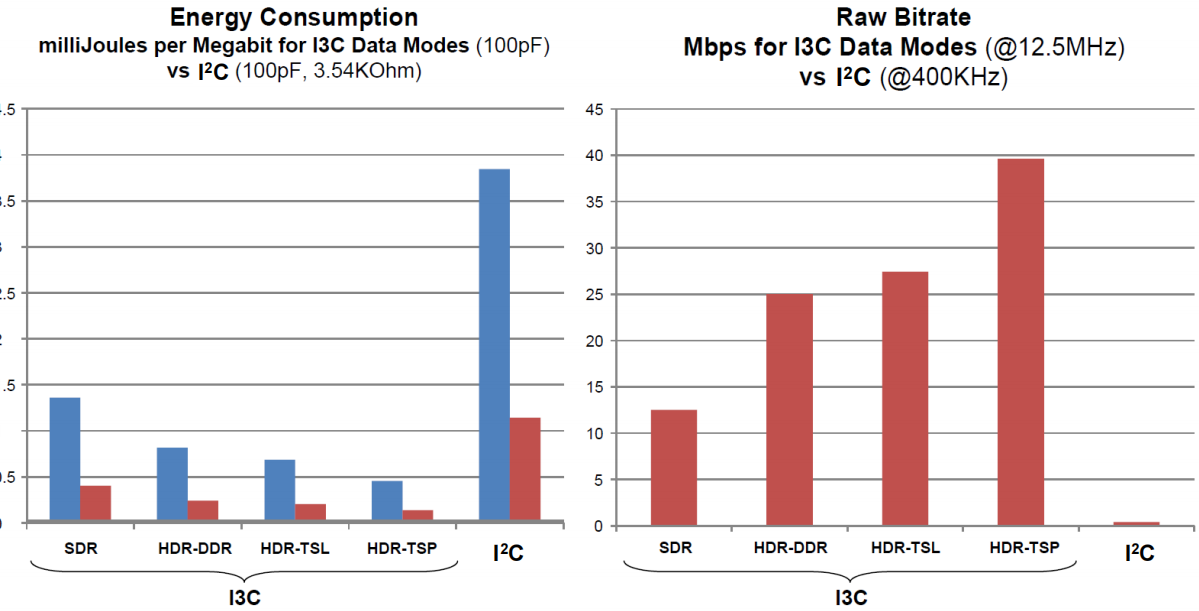

功耗與速率對比,NXP

速率上I2C典型的速率有3 Mbps max at 3.4 MHz (Hs)、0.8 Mbps max at 1 MHz (Fm+)、0.35 Mbps max at 400 KHz (Fm)。I3C典型的數(shù)據(jù)模式SDR是12MHz下的10.6Mbps,最高速率是HDR模式下的三元采樣,達到12.5MHz下的30Mbps。

另外,I2C是沒有命令字的,I3C則有著一整套通用命令字的集合。可以通過這些命令字實現(xiàn)動態(tài)地址分配、檢查當(dāng)前總線狀態(tài)、時間控制、IO擴展等等功能。整個功能比I2C有著全面的提升。

從I3C最典型的SDR信號處理上來看,動態(tài)地址分配后其啟動條件與I2C相同(SCL和SDA從高降到底),但接下來就不同了,I3C SCL可以達到4MHz,并且其高周期<45 ns,比I2C要求的50 ns低得多。接收到ACK之后,主機就會將SDA更改為推挽模式,并將其時鐘增加到12.5 MHz使器件進入SDR模式。

地址仲裁可以說是I3C極為重要的特性。上面提到,I3C將中斷內(nèi)置(IBI)進來了,當(dāng)Slave產(chǎn)生中斷時,IBI就會主動向主機發(fā)送中斷信息,上傳地址與其他信息。多個Slave同時產(chǎn)生中斷,這時候就有多個地址信息,就需要進行地址仲裁判別優(yōu)先級。地址仲裁遵從一個原則,那就是0s優(yōu)先,哪個Slave小哪個優(yōu)先級更高。地址沖裁也對熱插拔、動態(tài)地址分配以及多主機申請判別同樣有效。

I3C規(guī)范的更新

I3C協(xié)議V1.1.1的兩部分(MIPI會員版和基本版)均是在在去年發(fā)布。在最新的V1.1.1版本中,Slave增加了Reset機制,簡單來講就是使用退出HDR模式的方法增強了協(xié)議的故障恢復(fù)能力。

其次,增加了Group的尋址方式,可以對多個Slave進行分組然后進行尋址,類似于PMBus;再者是引入了HDR-BT模式,以12.5MHz提供高達97Mbps的數(shù)據(jù)速率;對于DDR模式則增加了Slave的中止、CRC功能;另外,Device-to-device tunnel機制也加入進來,實現(xiàn)Slave之間的直接通信。

I3C廠商動向

NXP

NXP作為I3C協(xié)議的主要制定者,提供IP與Silvaco合作,提供Free Basic Slave、Standard Slave、Advanced Slave以及主機四種不同包裝的I3C產(chǎn)品,根據(jù)不同具體應(yīng)用的區(qū)別,可以為Slave模塊添加1.5K到2.5K的門,消耗的功率也很小,并支持采用時鐘門控和其他方法來限制功耗。其后端可以在沒有系統(tǒng)時鐘的情況下運行。在NXP的RT系列MCU中,也可以看到I3C的身影。

Synopsys

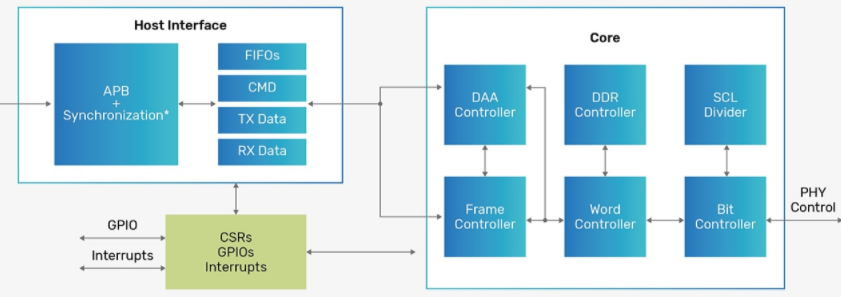

Synopsys也發(fā)布了DesignWare MIPI I3C控制器IP,可以將更多傳感器集成到系統(tǒng)中,同時簡化電路板設(shè)計并降低總體成本和功耗。DesignWare MIPI I3C控制器IP多主機操作和32位ARM AMBA 高級外設(shè)總線(APB)從接口。基于標(biāo)準(zhǔn)的APB接口將IP連接到SoC的其余部分,同時總線連接到寄存器和直接存儲器訪問(DMA)接口,從而實現(xiàn)輕松的IP集成,使設(shè)計人員能夠擁有完整的傳感器接口解決方案。

Cadence

作為聯(lián)盟成員Cadence可以提供MIPI I3C控制器。適用于MIPI I3C的Cadence控制器IP符合MIPI I3C規(guī)范,并與I2C規(guī)范兼容,其設(shè)計可快速輕松地集成到任何移動嵌入式SoC設(shè)備中,并以更好的性能和電源效率擴展傳感器通信能力。MIPI I3C控制器具有成為I3C總線上的啟動器/主機或目標(biāo)的能力。

Cadence

瑞薩電子

今年,瑞薩電子與Intel聯(lián)手推出了面向下一代服務(wù)器主板和其他基礎(chǔ)設(shè)施設(shè)備的I3C智能開關(guān)器件RG3MxxB12系列,為機架內(nèi)的每個子系統(tǒng)帶來先進的平臺管理功能。I3C智能開關(guān)產(chǎn)品家族允許以最大速度將兩個發(fā)起設(shè)備(上行)端口擴展到四個、八個或更多的目標(biāo)端口,是MIPI I3C基礎(chǔ)應(yīng)用很好的用例。

瑞薩電子

TI

隨著系統(tǒng)中目標(biāo)設(shè)備數(shù)量的增加,主機控制器必須考慮減少延遲、實現(xiàn)關(guān)鍵警報功能以及降低通信期間的功耗。TI在今年推出了基于I3C的溫度傳感器TMP139,以解決DDR5 DIMM等復(fù)雜系統(tǒng)中的低延遲熱傳感挑戰(zhàn)。在I3C的助力下,TMP139溫度精度超過了規(guī)范要求,可實現(xiàn)更高性能的DDR5存儲器模塊。

TI

小結(jié)

I3C作為一種可擴展、實用和控制的基于I2C升級而來的總線接口,能更為便捷得將外圍設(shè)備連接到應(yīng)用程序處理器,其簡潔、集成性高、成本效率高的優(yōu)勢非常明顯,給智能手機、可穿戴設(shè)備、汽車系統(tǒng)等任何移動產(chǎn)品提供了創(chuàng)新的設(shè)計思路。假以時日,I3C進一步開放授權(quán)并強化性能,I3C取代傳統(tǒng)的I2C,SPI,UART等接口也不是不可能。

-

i3c

+關(guān)注

關(guān)注

0文章

31瀏覽量

4852

原文標(biāo)題:從I2C升級革新到I3C,I3C能否取代傳統(tǒng)接口?

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【RA-Eco-RA4E2-64PIN開發(fā)板試用】I2C與I3C通信協(xié)議的應(yīng)用

I2C總線與Arduino的接口示例

RA-Eco-RA4E2-64PIN開發(fā)板試用+I2c與I3C通信協(xié)議的應(yīng)用。

優(yōu)秀實踐:I3C共享總線上的I2C器件

適用于I3C應(yīng)用的重要多路復(fù)用器特性

I3C電壓轉(zhuǎn)換器和多路復(fù)用器快速參考

具有 I2C 和 I3C接口的 TMP139 0.5°C 精度 JEDEC DDR5 B級數(shù)字溫度傳感器數(shù)據(jù)表

如何利用I3C提升嵌入式系統(tǒng)性能

使用stm32cubide的cubeMAX,沒有i3c的選項,為什么?

STM32H563的I3C無法正常通信是為什么?

TCA39306-Q1雙路雙向I3C、I2C總線和SMBus電壓電平轉(zhuǎn)換器數(shù)據(jù)表

什么是I3C接口 I3C和SPI接口有什么區(qū)別

什么是I2C接口?什么是I3C接口?I2C與I3C的區(qū)別

從I2C升級革新到I3C,I3C能否取代傳統(tǒng)接口?

從I2C升級革新到I3C,I3C能否取代傳統(tǒng)接口?

評論