在過采樣ADC中,一個很有效的提高SNR的方法為增大采樣速率以提高過采樣率。在其他器件都不改變的前提下,這樣做需要積分器和運放具有更高的帶寬,從而導致更高的功耗。

采用雙采樣技術,可以實現如下效果:

在保持原來OSR的基礎上,可將時鐘頻率縮小為原來的一半,對運放建立要求的時間因此變為原來的兩倍, 運放功耗因此降低 ;

在保持運放和采樣頻率不變的前提下, 有效采樣頻率變為原來的兩倍, OSR翻倍 , 實現更好的噪聲整形效果。

雙采樣積分器原理簡介

常用的運放增益帶寬積GBW可以表示為式(1):

gm和電流的關系可以表示為 式(2):

對普通的開關電容積分器,假如運放輸入對管的寬長比保持不變,提高一倍采樣時鐘頻率需要將GBW翻倍,因此需要將工作電流提高為原來的四倍。

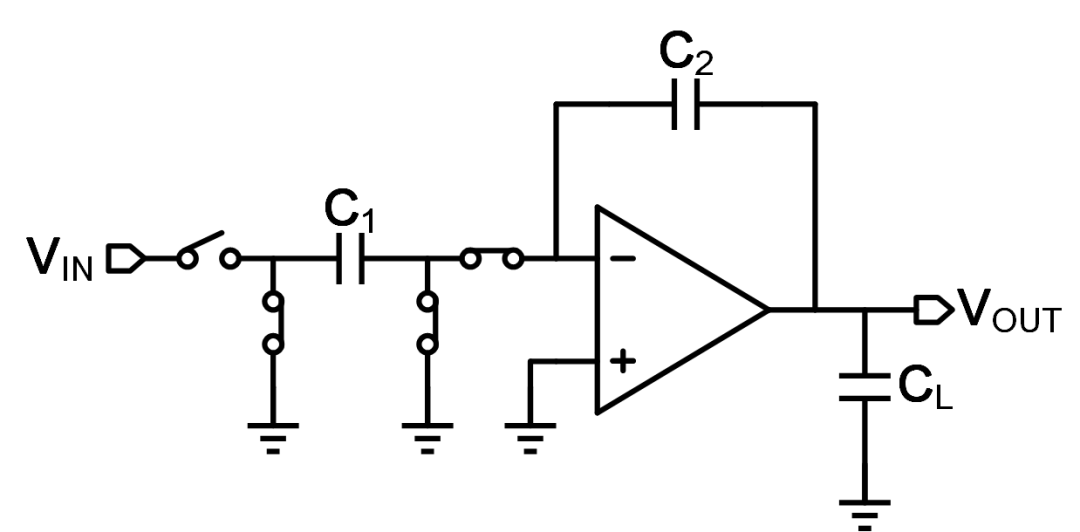

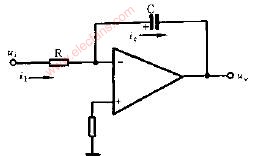

然而,對普通的開關電容積分器而言,當時鐘處在輸入采樣相時,運放處于空閑狀態。如果采用兩個采樣電容工作在交錯的時鐘下,便可以將運放更高效地使用,同時輸入信號采樣頻率也加倍。這就是雙采樣的基本思想。

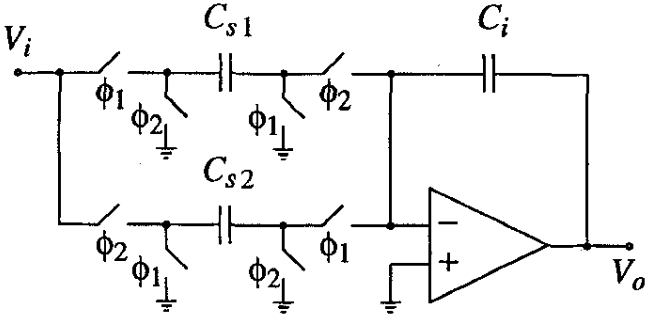

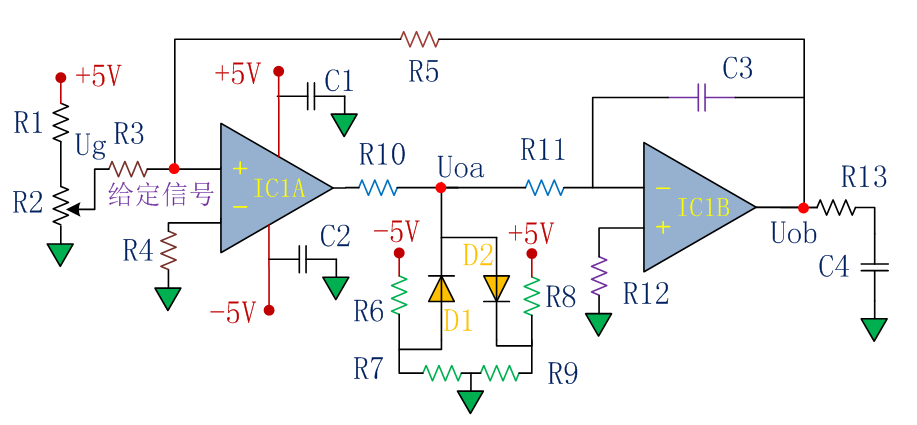

圖1 雙采樣積分器單端實現

圖1給出了雙采樣積分器的單端實現方式。在該電路中,通過兩個不同的電容對輸入信號采樣,電容CS1在Φ1相采樣,在Φ2相進行積分;電容CS2在Φ2相采樣,在Φ1相進行積分,因此,在時鐘的兩個相位都同時存在采樣和積分,有效采樣頻率因此變為原來的二倍。

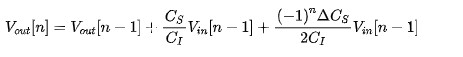

不考慮其他非理想因素,雙采樣積分器的傳遞函數可以表示為式(3):

其中:

n=0出現在Φ2為高時,同時需要注意的是:n代表第n個有效采樣周期,而不是采樣時鐘周期!雙采樣使得每個采樣時鐘周期內有兩個有效采樣周期。

式(3)左邊兩項為一個理想的延遲積分器,但最后一項為輸入信號與(-1)n之積,這表征的是頻率為采樣頻率一半(fs/2,也就是時鐘頻率fc)的余弦信號被采樣后,與輸入信號調制得到的信號,該信號由兩個采樣電容之間的失配造成。

對輸入信號采樣而言,由于輸入信號頻率很低,上述調制信號不會出現在信號帶內,因此不會影響輸入信號。

然而,對調制器的反饋DAC而言,由于DAC的輸出包含高頻量化噪聲,因此失配導致上述的信號調制現象會將量化噪聲折回帶內,因而惡化調制器的SNR。該現象為雙采樣Sigma-Delta調制器的主要缺點!

解決該問題目前常用的幾個辦法包含積分器電路結構設計抵消失配產生的額外電荷轉移;NTF在fs/2處放置零點;DAC采用單電容實現等,感興趣的讀者可以查閱相關文獻。

總結

本文簡單地介紹了雙采樣技術的出發點與基本原理,并介紹了其目前存在的主要缺點。希望讀者多多指正。

-

adc

+關注

關注

99文章

6608瀏覽量

547675 -

運放

+關注

關注

49文章

1186瀏覽量

53864 -

SNR

+關注

關注

3文章

197瀏覽量

24766 -

積分器

+關注

關注

4文章

100瀏覽量

28729

發布評論請先 登錄

相關推薦

積分器:Integrator

羅氏線圈為什么要用積分器?

評論