編者按

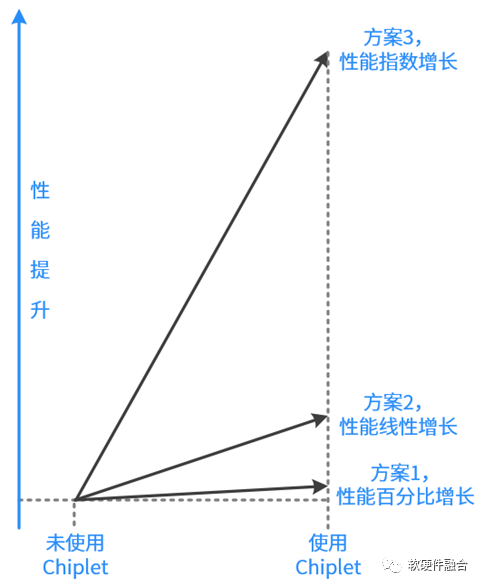

Chiplet標(biāo)準(zhǔn)UCIe已經(jīng)得到很多主流大廠的認可,席卷之勢愈發(fā)明顯。但就Chiplet的價值挖掘,目前可見的,都還停留在如何降成本和簡單地擴大設(shè)計規(guī)模方面。我們覺得,Chiplet的價值還沒有得到充分挖掘。 Chiplet帶來的價值,不應(yīng)該是線性增長,而應(yīng)該是指數(shù)增長:

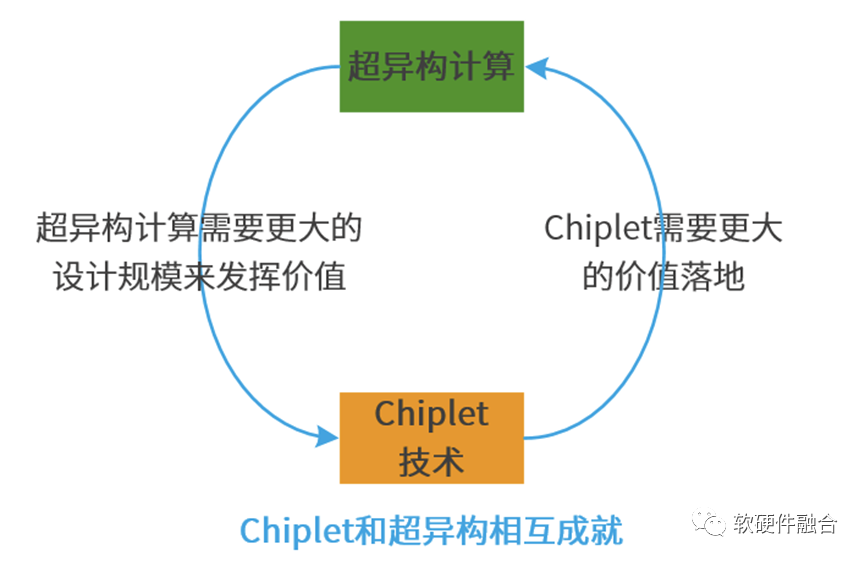

一方面,量變會引起質(zhì)變,Chiplet的流行,快速增加的單芯片設(shè)計規(guī)模,會給系統(tǒng)架構(gòu)創(chuàng)新提供更大的發(fā)揮空間,使得計算的架構(gòu),從異構(gòu)走向超異構(gòu)。

另一方面,超異構(gòu)帶來的算力指數(shù)級提升,使得Chiplet的價值得到更加充分的發(fā)揮,反過來會促進Chiplet的大范圍流行。

1 背景知識

1.1 單DIE性能和成本

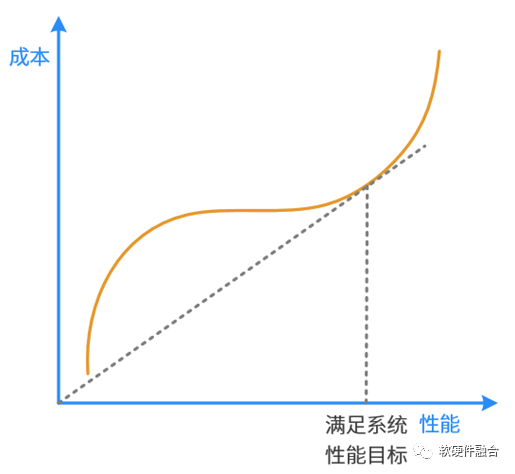

單DIE的性能和成本,是正相關(guān)的關(guān)系。通常的芯片DIE設(shè)計,一定是在保證系統(tǒng)所需性能的條件下,選擇最合適的工藝,達到最合適的面積(成本),達到在性能約束條件下的性能成本比最優(yōu)。或者說:

在系統(tǒng)性能成本最優(yōu)的狀態(tài)下,受邊際效應(yīng)影響,想再想增加單DIE性能,所需要付出的成本代價非常高,會顯著影響性價比。

在系統(tǒng)性能成本最優(yōu)的狀態(tài)下,想要再優(yōu)化單DIE成本,可能會引起性能的大比例下降,反而不是性價比最優(yōu)。

1.2 Chiplet協(xié)議UCIe

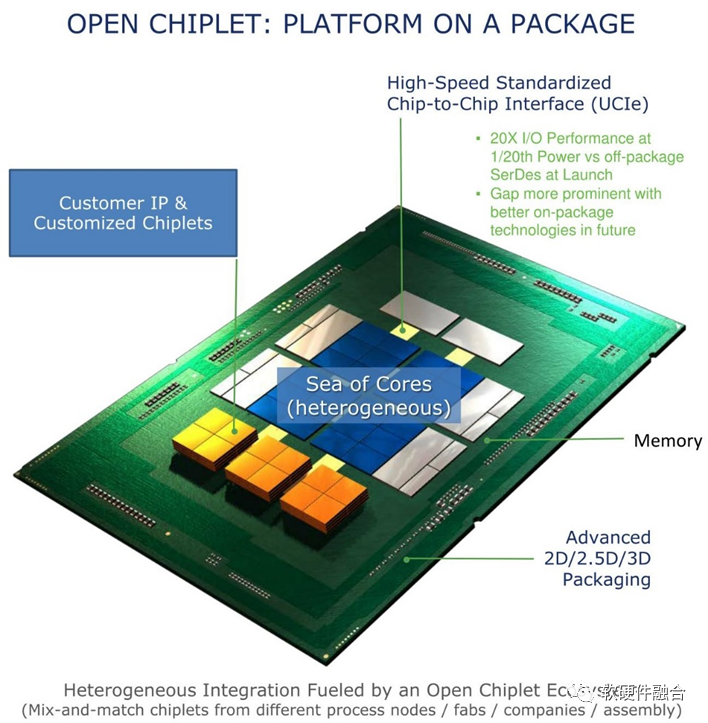

英特爾、AMD、ARM、高通、三星、臺積電、日月光等大廠,以及Google Cloud、Meta、微軟于2022年3月2日宣布了一項新技術(shù)標(biāo)準(zhǔn)UCIe(Universal Chiplet Interconnect Express)。UCIe是一個開放的行業(yè)互連標(biāo)準(zhǔn),可以實現(xiàn)小芯片之間的封裝級互連,具有高帶寬、低延遲、經(jīng)濟節(jié)能的優(yōu)點。 UCIe能夠滿足幾乎所有計算領(lǐng)域,包括云端、邊緣端、企業(yè)、5G、汽車、高性能計算和移動設(shè)備等,對算力、內(nèi)存、存儲和互連不斷增長的需求。UCIe 具有封裝集成不同Die的能力,這些Die可以來自不同的晶圓廠、采用不同的設(shè)計和封裝方式。

UCIe白皮書中給出的Chiplets封裝集成的價值:

首先是面積的影響。為了滿足不斷增長的性能需求,芯片面積增加,有些設(shè)計甚至?xí)鲅谀0婷娣e的限制。即使不超過面積限制,改用多個小芯片也更有利于提升良率。另外,多個相同Die的集成封裝能夠適用于更大規(guī)模的場景。

另一個價值體現(xiàn)在降低成本。例如,處理器核心可以采用先進的工藝,用更高的成本換取極致的性能,而內(nèi)存和I/O控制器則可以復(fù)用非先進工藝。隨著工藝節(jié)點的進步,成本增長非常迅速。若采用多Die集成模式,有些Die的功能不變,我們不必對其采用先進工藝,可在節(jié)省成本的同時快速搶占市場。Chiplet封裝集成模式還可以使用戶能夠自主選擇Die的數(shù)量和類型。例如,用戶可以根據(jù)需求挑選任意數(shù)量的計算、內(nèi)存和I/O Die,并無需進行Die的定制設(shè)計,可降低產(chǎn)品的SKU成本。

允許廠商能夠以快速且經(jīng)濟的方式提供定制解決方案。如圖1所示,不同的應(yīng)用場景可能需要不同的計算加速能力,但可以使用同一種核心、內(nèi)存和I/O。Chiplet方式允許廠商根據(jù)功能需求對不同的功能單元應(yīng)用不同的工藝節(jié)點,并實現(xiàn)共同封裝。相比板級互連,封裝級互連具有線長更短、布線更緊密的優(yōu)點。

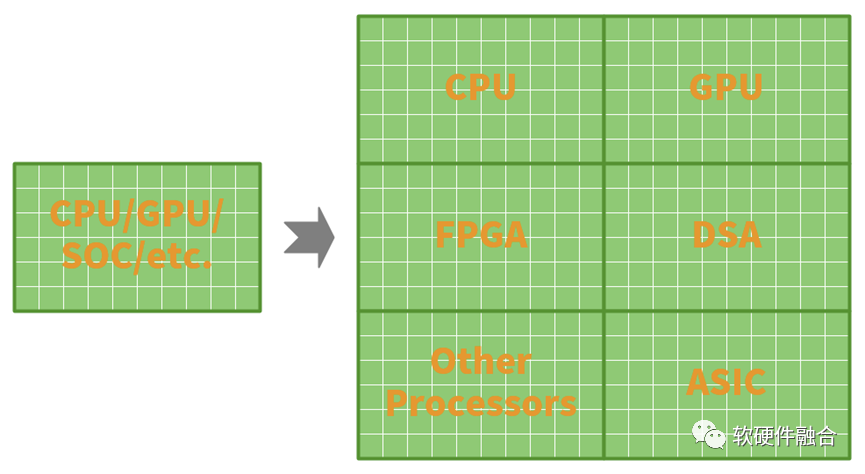

1.3 超異構(gòu)計算

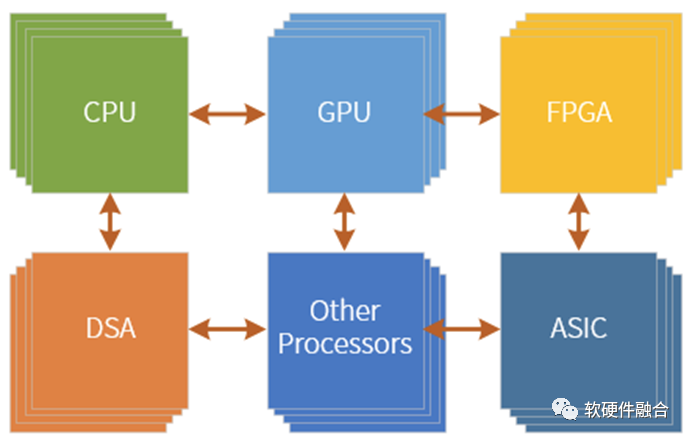

系統(tǒng)變得越來越龐大,系統(tǒng)可以分解成很多個子系統(tǒng),子系統(tǒng)的規(guī)模已經(jīng)達到傳統(tǒng)單系統(tǒng)的規(guī)模。因此,都升級一下:系統(tǒng)變成了宏系統(tǒng),子系統(tǒng)變成了系統(tǒng)。 系統(tǒng)足夠龐大,場景綜合,單類型架構(gòu)無法包打天下:

CPU靈活性最好,但性能較差;

DSA性能很好,但靈活性差;

GPU介于兩者之間,可以說能較好的平衡性能和靈活性,也可以說,性能和靈活性都不夠極致。

規(guī)模龐大的復(fù)雜系統(tǒng)存在很多硬件加速的空間:

復(fù)雜系統(tǒng)最核心的一個特征是二八定律。用戶只關(guān)心自己的應(yīng)用,而應(yīng)用通常只占系統(tǒng)的20%,另外80%用戶不關(guān)心的也相對確定的部分,一般稱為基礎(chǔ)設(shè)施,這些是可以通過硬件加速來優(yōu)化性能的。

系統(tǒng)是逐步發(fā)展和沉淀的。很多原本屬于應(yīng)用層的工作任務(wù),隨著時間推移,越來越成熟,逐漸地沉淀成了基礎(chǔ)設(shè)施。這些沉淀的工作任務(wù)可以通過硬件加速來優(yōu)化性能。最典型的場景是AI推理,現(xiàn)在已經(jīng)成為了基礎(chǔ)的服務(wù),供不同的應(yīng)用調(diào)用。

在云計算、邊緣計算等形式的綜合計算模式下,單個用戶應(yīng)用的規(guī)模可能不大,但因為云計算的超大規(guī)模和多租戶,很多相似的用戶應(yīng)用其總和規(guī)模足夠龐大,因此,也可以通過GPU、FPGA或?qū)S眯酒姆绞竭M行加速優(yōu)化。

那么,要做的就是揚長避短,把不同類型的處理引擎協(xié)作起來,把各種引擎的優(yōu)勢充分利用起來,形成超異構(gòu)計算架構(gòu):

DSA負責(zé)相對確定的大計算量的工作;

GPU負責(zé)應(yīng)用層有一些性能敏感的并且有一定彈性的工作;

CPU啥都能干,負責(zé)兜底。

于是整個系統(tǒng)架構(gòu)就變成了超異構(gòu)架構(gòu)。

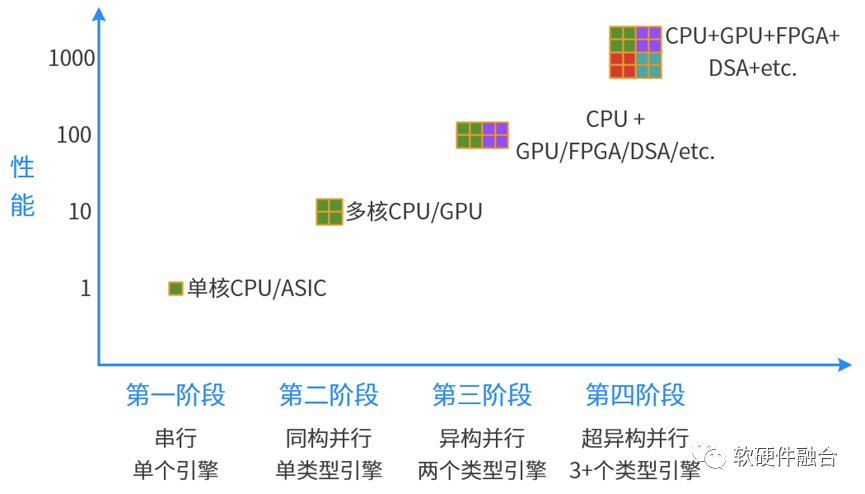

總結(jié)一下計算架構(gòu)發(fā)展的四個階段:

第一階段,單CPU串行計算;

第二極端,多核CPU的并行計算;

第三階段,CPU+xPU的異構(gòu)計算;

第四階段,CPU+GPU+DSA+etc.的超異構(gòu)計算。

2 Chiplet技術(shù)方案

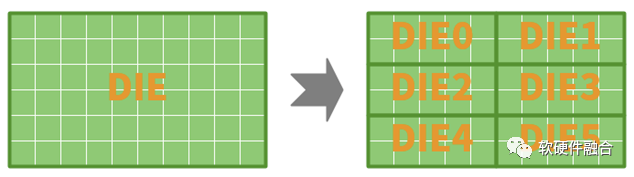

2.1 方案1:設(shè)計規(guī)模不變,優(yōu)化單DIE面積和良率等

一般情況下,在同等工藝同等功耗技術(shù)下,我們可以簡單地認為,面積和成本成正比的。Chiplet實現(xiàn)用面積更小的DIE,實現(xiàn)同等規(guī)模設(shè)計,其優(yōu)勢主要為:

單DIE面積變小,增加芯片良率。而通常,單DIE的面積是已經(jīng)平衡好良率的情況下的,再減小面積優(yōu)化良率,可能效果并不是很明顯。并且,多DIE封裝會帶來額外的良率風(fēng)險。這樣,一里一外的問題,通過多DIE來優(yōu)化良率的效果可能就不會很明顯。

可以讓一些DIE不采用先進工藝,通過較低一些的工藝降低成本。

在不改變性能的條件下,通過Chiplet封裝可以降低成本;也可以反過來說,在同樣成本條件下,通過Chiplet封裝可以提升性能。

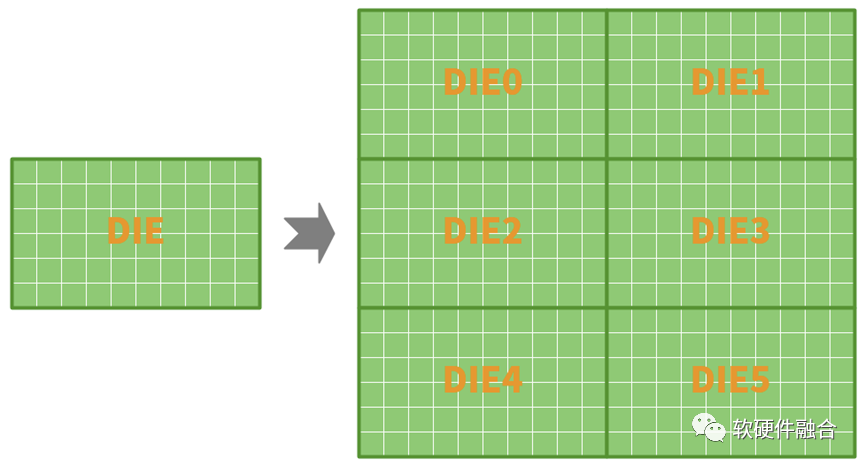

2.2 方案2:單DIE設(shè)計規(guī)模不變,多DIE集成

當(dāng)我們確定好單個DIE的性能和面積(功耗)的時候,這個時候相當(dāng)于是把工藝的價值挖掘到了最優(yōu)。需要Chiplet的價值,也同樣需要工藝的價值,都不能少。 我們要做的是在工藝價值的基礎(chǔ)上,再疊加Chiplet封裝的價值。而不是如方案1一樣,為了Chiplet而Chiplet,反而放棄工藝的價值。 因此,我們可以在原有DIE的基礎(chǔ)上,通過多DIE封裝來立竿見影地提升性能。

2.3 方案3:多DIE集成設(shè)計規(guī)模倍增,并且重構(gòu)系統(tǒng)

通常,CPU組成的芯片,性能不夠;而GPU、DSA組成的芯片無法單獨工作,需要外掛CPU,形成CPU+XPU的異構(gòu)計算架構(gòu);而SOC本質(zhì)上是CPU+xPU的多個異構(gòu)系統(tǒng)的集成。 異構(gòu)計算和SOC,本質(zhì)上都是以CPU為中心的系統(tǒng),XPU是一個個孤島,所有的事情都需要CPU的參與才能把這些處理引串起來。 超異構(gòu)完全打破不同處理引擎之間的界限,CPU和其他XPU同樣的地位,XPU間可以非常充分的交互,達到系統(tǒng)充分的整合。超異構(gòu)計算可以做到:

性能和靈活性兼顧。因為二八定律的緣故,絕大部分計算是在DSA級別的處理引擎中完成,所以性能效率很好。而用戶關(guān)心的應(yīng)用依然是在CPU級別的處理引擎完成,又兼顧了靈活可編程性。

因為超異構(gòu)計算架構(gòu)可以駕馭更大的系統(tǒng),因此,可以做到,在性能效率和DSA同量級的情況下,性能相比DSA再數(shù)量級的提升。

2.4 方案性能提升對比

注意:本節(jié)內(nèi)容是定性分析,還無法做到定量分析。 方案1,可以實現(xiàn)性能的百分比增長。方案1的道理很好理解,本來的目標(biāo)是優(yōu)化成本,在同等性能情況下,能夠百分比地優(yōu)化成本。我們相應(yīng)地折算一下,在同等成本下,方案1可以做到性能的百分比提升。 方案2,可以實現(xiàn)性能的線性增長。方案2也很好理解,通過增加更多數(shù)量的DIE來提升并行度,以此來提升性能。集成多少個DIE,性能就增加到多少倍。 方案3,可以實現(xiàn)性能的指數(shù)增長。方案3通過整個系統(tǒng)重構(gòu),挖掘系統(tǒng)的一些可加速的點,然后再實現(xiàn)整個系統(tǒng)的充分整合重構(gòu)。以此來提升性能。可以達到數(shù)量級的性能增長。

3 總結(jié)

3.1 設(shè)計規(guī)模的量變,引起系統(tǒng)架構(gòu)的質(zhì)變

規(guī)模是一個很重要的因素。 云計算百萬臺的超大規(guī)模,其軟硬件架構(gòu)和運營模式跟傳統(tǒng)的數(shù)百臺的私有機房是完全迥異的。深度神經(jīng)網(wǎng)絡(luò),通過更大量數(shù)據(jù)、更深層次網(wǎng)絡(luò)的量變,成就了AI的“智”變。 芯片也是同樣的道理,隨著規(guī)模的增長,很多設(shè)計方案考慮的問題會跟以前完全不一樣。在小規(guī)模的時候,我們強調(diào)定制,極度優(yōu)化性能和功耗等;但等到超大規(guī)模IC設(shè)計,我們更多關(guān)注的是通用性、可編程性、易用性、生態(tài)等。 Chiplet機制,提供了立竿見影讓芯片設(shè)計規(guī)模數(shù)量級增加的能力。如果我們不在系統(tǒng)架構(gòu)層次創(chuàng)新,充分利用芯片規(guī)模數(shù)量級增加的這個優(yōu)勢,只是簡單的平行擴展,那真是暴殄天物,浪費Chiplet給系統(tǒng)架構(gòu)師們的饋贈。 換個角度,現(xiàn)有的異構(gòu)計算也好,SOC也好,無法駕馭Chiplet提供的超大規(guī)模芯片系統(tǒng)。需要本質(zhì)的、體系性的系統(tǒng)架構(gòu)創(chuàng)新,來更好地駕馭Chiplet的價值。

3.2 超異構(gòu),讓Chiplet價值得到更大的發(fā)揮

超異構(gòu)集成更多的處理引擎,提供更高的并行性,實現(xiàn)更分布式的系統(tǒng),可以更好地駕馭數(shù)量級增加的芯片設(shè)計規(guī)模。 此外,Chiplet更好地容納現(xiàn)有宏系統(tǒng)的承載,通過超異構(gòu),使得很多性能優(yōu)化措施得到落實,從而使得性能指數(shù)級增長(而不是根據(jù)面積的增加,線性增長)。 可以說,超異構(gòu),成就了Chiplet更大的價值,使得Chiplet方案得到更大范圍的落地,促進Chiplet技術(shù)的成熟和市場繁榮。

3.3 Chiplet和超異構(gòu)的關(guān)系:雙劍合璧,相互成就

超異構(gòu)計算和Chiplet技術(shù)是相互協(xié)同、相互成就的關(guān)系:

系統(tǒng)越大,設(shè)計規(guī)模越大,超異構(gòu)的性能優(yōu)勢就越明顯。

超異構(gòu)計算,需要數(shù)量級提升的晶體管資源,而Chiplet可以在芯片層次提供如此規(guī)模的晶體管資源,實現(xiàn)超異構(gòu)計算方案和價值落地。

超異構(gòu)計算的價值得到充分體現(xiàn),超異構(gòu)不斷落地,會帶動Chiplet的價值發(fā)揮、更廣泛的落地以及市場繁榮。

隨著超異構(gòu)的發(fā)展,對Chiplet的要求會不斷提高,需要Chiplet技術(shù)向更高的能力邁進。

審核編輯 :李倩

-

單芯片

+關(guān)注

關(guān)注

3文章

421瀏覽量

34594 -

chiplet

+關(guān)注

關(guān)注

6文章

434瀏覽量

12607 -

UCIe

+關(guān)注

關(guān)注

0文章

47瀏覽量

1636

原文標(biāo)題:超異構(gòu) x Chiplet:雙劍合璧,實現(xiàn)算力指數(shù)級提升

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

超算智算融合 南京信易達發(fā)布全新“智能算力融合平臺”

《算力芯片 高性能 CPU/GPU/NPU 微架構(gòu)分析》第1-4章閱讀心得——算力之巔:從基準(zhǔn)測試到CPU微架構(gòu)的深度探索

安謀科技異構(gòu)算力組合,破局生成式AI算力挑戰(zhàn)

神州鯤泰亮相北京數(shù)字安全大會,以智能算力構(gòu)筑數(shù)據(jù)安全的堅實底座

異構(gòu)混訓(xùn)整合不同架構(gòu)芯片資源,提高算力利用率

商湯科技采購40000顆英偉達芯片,縮小中美算力差距

鯤泰新聞|神州鯤泰創(chuàng)新智算之旅北京站開幕,發(fā)布全新智算架構(gòu)和液冷整機柜產(chǎn)品應(yīng)對 “多云、異構(gòu)、綠色

聚焦全國一體化算力體系構(gòu)建,憶聯(lián)以強大存力“引擎”釋放算力潛能

到底什么是算力?算力的價值在哪里?

智能算力規(guī)模超通用算力,大模型對智能算力提出高要求

超異構(gòu)帶來的算力指數(shù)級提升,使得Chiplet的價值得到更加充分的發(fā)揮

超異構(gòu)帶來的算力指數(shù)級提升,使得Chiplet的價值得到更加充分的發(fā)揮

評論