在談 RISC-V 之前,我們先梳理幾個概念:

1. 芯片

芯片 是所有半導(dǎo)體元器件的統(tǒng)稱,它是把一定數(shù)量的常用電子元件(如電阻,電容,晶體管等),通過半導(dǎo)體工藝集成在一起,具有特定功能的電路。

2. CPU

cpu 是芯片的一種,它里面包含了控制部件和運算部件,即中央處理器。1971 年, Intel 將運算器和控制器集成到一個芯片上,稱為4004 微處理器,這標(biāo)志著CPU 的誕生。

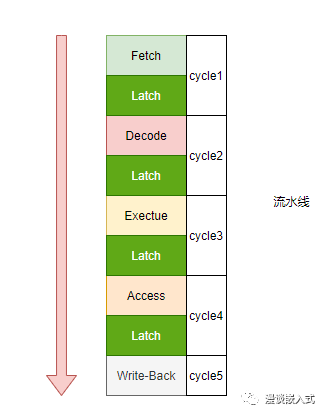

CPU 的工作流程分為以下5個階段:

取指令

指令譯碼

執(zhí)行指令

訪存讀取數(shù)據(jù)

結(jié)果寫回

指令和數(shù)據(jù)統(tǒng)一存儲在內(nèi)存中,數(shù)據(jù)與指令需要從統(tǒng)一的存儲空間存取,經(jīng)由共同的總線傳輸,無法并行讀取數(shù)據(jù)和指令。馮諾依曼結(jié)構(gòu)

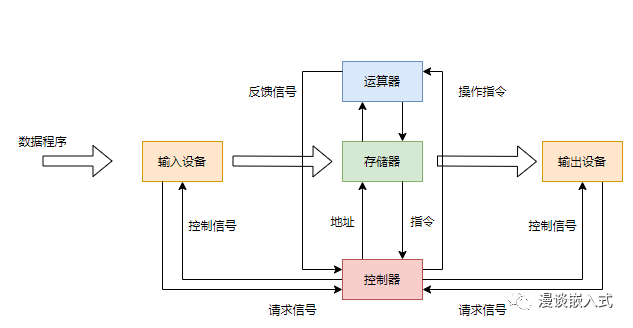

3. 馮諾依曼結(jié)構(gòu)

馮·諾依曼結(jié)構(gòu)也稱普林斯頓結(jié)構(gòu),是一種將程序指令存儲器和數(shù)據(jù)存儲器合并在一起的存儲器結(jié)構(gòu)。

程序指令存儲地址和數(shù)據(jù)存儲地址指向同一個存儲器的不同物理位置,因此程序指令和數(shù)據(jù)的寬度相同,如英特爾公司的8086中央處理器的程序指令和數(shù)據(jù)都是16位寬。

數(shù)學(xué)家馮·諾依曼提出了計算機制造的三個基本原則,即采用二進制邏輯、程序存儲執(zhí)行以及計算機由五個部分組成:

運算器

控制器

存儲器

輸入設(shè)備

輸出設(shè)備

現(xiàn)代計算機發(fā)展所遵循的基本結(jié)構(gòu)形式始終是馮·諾依曼機結(jié)構(gòu)。這種結(jié)構(gòu)特點是“程序存儲,共享數(shù)據(jù),順序執(zhí)行”,需要 CPU 從存儲器取出指令和數(shù)據(jù)進行相應(yīng)的計算

(1)單處理機結(jié)構(gòu),機器以運算器為中心;

(2)采用程序存儲思想;

(3)指令和數(shù)據(jù)一樣可以參與運算;

(4) 數(shù)據(jù)以二進制表示;

(5)將軟件和硬件完全分離;

(6) 指令由操作碼和操作數(shù)組成;

(7)指令順序執(zhí)行。

這套理論被稱為馮·諾依曼體系結(jié)構(gòu)。

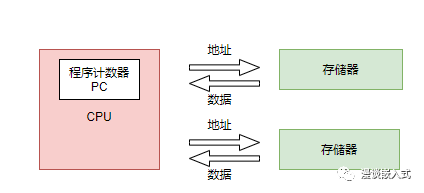

4. 哈佛結(jié)構(gòu)

哈佛結(jié)構(gòu)是一種將程序指令存儲和數(shù)據(jù)存儲分開的存儲器結(jié)構(gòu),如下圖所示。中央處理器首先到程序指令存儲器中讀取程序指令內(nèi)容,解碼后得到數(shù)據(jù)地址,再到相應(yīng)的數(shù)據(jù)存儲器中讀取數(shù)據(jù),并進行下一步的操作(通常是執(zhí)行)。

程序指令存儲和數(shù)據(jù)存儲分開,可以使指令和數(shù)據(jù)有不同的數(shù)據(jù)寬度,如Microchip公司的PIC16芯片的程序指令是14位寬度,而數(shù)據(jù)是8位寬度。

哈佛結(jié)構(gòu)的微處理器通常具有較高的執(zhí)行效率。其程序指令和數(shù)據(jù)指令分開組織和存儲的,執(zhí)行時可以預(yù)先讀取下一條指令。

哈佛結(jié)構(gòu)是指程序和數(shù)據(jù)空間獨立的體系結(jié)構(gòu), 目的是為了減輕程序運行時的訪存瓶頸。

哈佛結(jié)構(gòu)能基本上解決取指和取數(shù)的沖突問題。

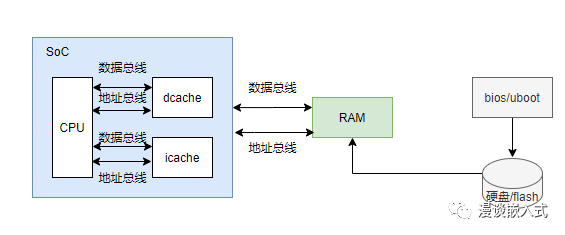

5. 混合式結(jié)構(gòu)

使用兩個獨立的存儲器模塊,分別存儲指令和數(shù)據(jù),每個存儲模塊都不允許指令和數(shù)據(jù)并存;

具有一條獨立的地址總線和一條獨立的數(shù)據(jù)總線,利用公用地址總線訪問兩個存儲模塊(程序存儲模塊和數(shù)據(jù)存儲模塊),公用數(shù)據(jù)總線則被用來完成程序存儲模塊或數(shù)據(jù)存儲模塊與CPU之間的數(shù)據(jù)傳輸;

兩條總線由程序存儲器和數(shù)據(jù)存儲器分時共用。

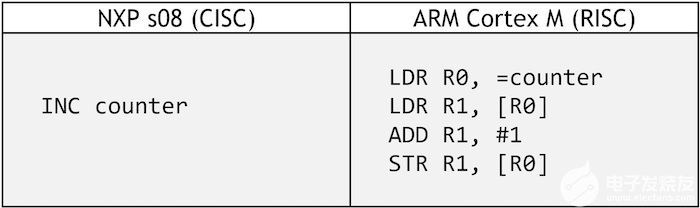

6. CISC

從前面的內(nèi)容中,我們已經(jīng)得知 CPU 就是不斷的執(zhí)行指令,來實現(xiàn)程序的執(zhí)行,最后實現(xiàn)相應(yīng)的功能。但是一顆CPU 能實現(xiàn)多少條指令,每條指令完成多少功能,卻是值得細(xì)細(xì)考量的問題。

CISC的英文全稱為“Complex InstrucTIon Set Computer”,即“復(fù)雜指令系統(tǒng)計算機”,從計算機誕生以來,人們一直沿用CISC指令集方式。早期的桌面軟件是按CISC設(shè)計的,并一直沿續(xù)到現(xiàn)在。目前,桌面計算機流行的x86體系結(jié)構(gòu)即使用CISC。

CISC 的優(yōu)勢在于,用少量的指令就能實現(xiàn)非常多的功能,程序自身大小也會下降,減少內(nèi)存空間占用。

缺點:這些復(fù)雜指令集,包含的指令數(shù)量多且功能復(fù)雜,設(shè)計復(fù)雜。

7. RISC

RISC的英文全稱為“Reduced InstrucTIon Set Computer”,即“精簡指令集計算機”,是一種執(zhí)行較少類型計算機指令的微處理器,起源于80年代的MIPS主機(即RISC機),RISC機中采用的微處理器統(tǒng)稱RISC處理器。

這樣一來,它能夠以更快的速度執(zhí)行操作(每秒執(zhí)行更多百萬條指令,即MIPS)。因為計算機執(zhí)行每個指令類型都需要額外的晶體管和電路元件,計算機指令集越大就會使微處理器更復(fù)雜,執(zhí)行操作也會更慢。

RISC 設(shè)計方案非常簡約,通常有20 多條簡化的指令集。每條指令長度固定,由專用的加載和儲存指令用于訪問內(nèi)存,減少了內(nèi)存的尋址方式,大多數(shù)運算指令只能訪問操作寄存器。

CPU 中配有大量的寄存器,這些指令的選取都是工程中使用頻率最高的指令。由于指令長度一致,功能單一,操作依賴于寄存器,這些特性使得CPU 指令預(yù)取、分支預(yù)測、指令流水線等部件的效能大大發(fā)揮,幾乎一個時鐘周期能執(zhí)行多條指令

RISC 的代表產(chǎn)品是 ARM 和 RISC-V。現(xiàn)在,兩者已經(jīng)沒有明顯的界限了,開始相互融合了

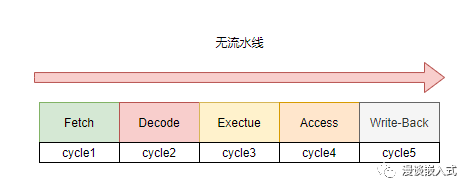

8. 流水線

談到指令并行,就不得不談到CPU 核心的流水線。現(xiàn)代處理器都是流水線結(jié)構(gòu)。

流水線(Pipeline)技術(shù)是指程序在執(zhí)行時候多條指令重疊進行操作的一種準(zhǔn)并行處理實現(xiàn)技術(shù)。通俗的講將一個時序過程,分解成若干個子過程,每個過程都能有效的與其他子過程同時執(zhí)行。這種思想最初是在RISC的架構(gòu)中出現(xiàn)的,旨在提高處理器處理效率,爭取在一個時鐘周期中完成一條指令。

一般常見的5級流水線有:

取指:指令取指(Instruction Fetch)是指將指令從存儲器中讀取出來的過程。

譯碼:指令譯碼(Instruction Decode)是指將存儲器中取出的指令進行翻譯的過程。經(jīng)過譯碼之后得到指令需要的操作數(shù)寄存器索引,可以使用此索引從通用寄存器組(Register File)中將操作數(shù)讀出。

執(zhí)行:指令譯碼之后所需要進行的計算類型都已得知,并且已經(jīng)從通用寄存器組中讀取出了所需的操作數(shù),那么接下來便進行指令執(zhí)行(Instruction Execute)。指令執(zhí)行是指對指令進行真正運算的過程。譬如,如果指令是一條加法運算指令,則對操作數(shù)進行加法操作;如果是減法運算指令,則進行減法操作。在“執(zhí)行”階段的最常見部件為算術(shù)邏輯部件運算器(Arithmetic Logical Unit,ALU),作為實施具體運算的硬件功能單元。

訪存:存儲器訪問指令往往是指令集中最重要的指令類型之一,訪存(Memory Access)是指存儲器訪問指令將數(shù)據(jù)從存儲器中讀出,或者寫入存儲器的過程。

寫回:寫回(Write-Back)是指將指令執(zhí)行的結(jié)果寫回通用寄存器組的過程。如果是普通運算指令,該結(jié)果值來自于“執(zhí)行”階段計算的結(jié)果;如果是存儲器讀指令,該結(jié)果來自于“訪存”階段從存儲器中讀取出來的數(shù)據(jù)。

無流水線:

有流水線:

它增加了四組寄存器,每一個流水線級數(shù)內(nèi)部都有各自的組合邏輯數(shù)據(jù)通路,彼此之間沒有復(fù)用資源,因此,其面積開銷是比較大的,但是由于可以讓不同的流水線級數(shù)同時做不同的事情,而達到流水的效果,提高了性能,優(yōu)化了時序,增加了吞吐率。

9. RISC-V

在了解了 RISC 和 CISC 兩種計算機指令設(shè)計架構(gòu)后。我們來看看 RISC-V。

RISC-V 的 “V”, 有兩層意思,一方面代表第5代 RISC;另一方面, “V”取Variation 之意代表變化。

9.1 RISC-V 是什么?

RISC-V 是一套開放許可證書、免費的、由基金維護的、一個整數(shù)運算指令集外加多個擴展指令集的CPU 結(jié)構(gòu)規(guī)范(ISA)。

整數(shù)運算指令集 + 擴展指令集

任何硬件開發(fā)商或者組織都可以免費使用這套規(guī)范,構(gòu)建CPU 芯片產(chǎn)品。

9.2 指令集命名方式

以RV 為2前綴,然后是位寬,最后代表是指令集的字母集合:

RV[###][abc......xyz]

| 符號 | 說明 |

|---|---|

| RV | RISC-V 縮寫 |

| [###] | 用于標(biāo)識處理器位寬,取值[32, 64,128],也就是處理器的寄存器位寬 |

| [abc...xyz] | 標(biāo)識該處理器支持的指令模塊集合 |

比如:RV64IMAC, 表示64 位 RISC-V, 支持整數(shù)指令、乘除法指令、原子指令和壓縮指令。

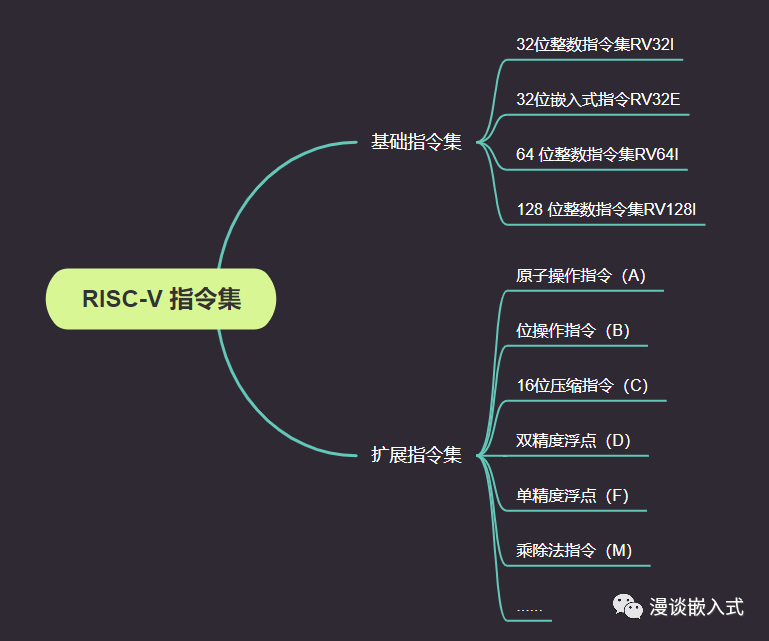

9.3 指令集模塊

指令集模塊是一款CPU架構(gòu)的主要組成部分,是CPU 和 上層軟件交互的核心,也是cpu主要功能體現(xiàn)。

RISC-V 規(guī)范只定義了CPU 需要包含的基礎(chǔ)整型操作指令:

整型的儲存

加載

加減

邏輯

移位

分支

等。

其他指令為可選指令或者用戶擴展指令。比如:

乘

除

取模

單精度浮點

雙精度浮點

壓縮

原子指令

等。

擴展指令是芯片工程師根據(jù)需求自定義。

所以 RISC-V 采用的是模塊化的指令集,易于擴展、組裝。它適用于不同的應(yīng)用場景,可以降低 CPU 實現(xiàn)成本。

9.4 RISC-V 寄存器

指令的操作數(shù)來源于寄存器,精簡指令架構(gòu)的CPU,都會提供大量的寄存器。

RISC-V 的規(guī)范定義了32個通用寄存器以及一個PC寄存器,這對于RV32I、RV64I、RV128I 指令集都是一樣的,只是寄存器的位寬不一樣。

如果要實現(xiàn)支持F/D擴展指令集的CPU,則需要額外支持32個浮點寄存器。而如果實現(xiàn)只支持RV32E指令集的嵌入式CPU,則可以將32個通用寄存器縮減為16個通用寄存器。

| 寄存器 | ABI 名稱 | 說明 |

|---|---|---|

| x0 | zero | 0值寄存器,硬編碼為0,寫入數(shù)據(jù)忽略,讀取數(shù)據(jù)為0 |

| x1 | ra | 用于返回地址(return address) |

| x2 | sp | 用于棧指針(stack pointer) |

| x3 | gp | 用于通用指針 (global pointer) |

| x4 | tp | 用于線程指針 (thread pointer) |

| x5 | t0 | 用于存放臨時數(shù)據(jù)或者備用鏈接寄存器 |

| x6~x7 | t1~t2 | 用于存放臨時數(shù)據(jù)寄存器 |

| x8 | s0/fp | 需要保存的寄存器或者幀指針寄存器 |

| x9 | s1 | 需要保存的寄存器 |

| x10~x11 | a0~a1 | 函數(shù)傳遞參數(shù)寄存器或者函數(shù)返回值寄存器 |

| x12~x17 | a2~a7 | 函數(shù)傳遞參數(shù)寄存器 |

| x18~x27 | s2-s11 | 需要保存的寄存器 |

| x28~x31 | t3~t6 | 用于存放臨時數(shù)據(jù)寄存器 |

ABI: 應(yīng)用程序二進制接口,可以理解為寄存器別名,高級語言在生成匯編會用到。

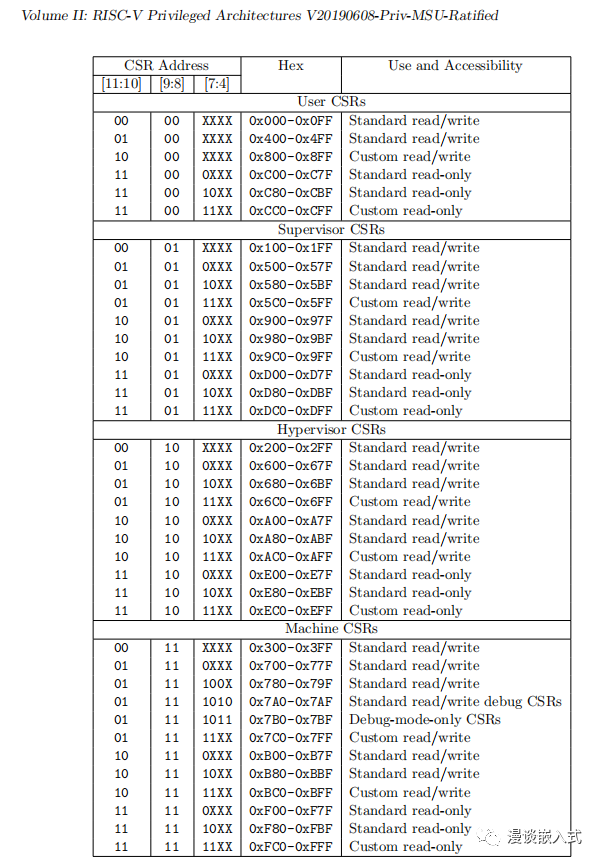

不同的 指令集架構(gòu)都有特權(quán)級的概念,RSIC-V 也不例外,我們來看看RISC-V 的特權(quán)級。

不同的特權(quán)級能訪問的系統(tǒng)資源不同,高特權(quán)級的能訪問低特權(quán)級的資源,反之卻不行。

RISC-V 的規(guī)范文檔定義了四個特權(quán)級別(privilege level),特權(quán)等級由高到低排列,如下表所示。

| 名稱 | 級別 | 縮寫 | 編碼 |

|---|---|---|---|

| 用戶,應(yīng)用程序特權(quán)級 | 0 | U | 00 |

| 管理員特權(quán)級 | 1 | S | 01 |

| 虛擬機監(jiān)視特權(quán)級 | 2 | H | 10 |

| 機器特權(quán)級 | 3 | M | 11 |

一個RISC-V 硬件線程(hart),相當(dāng)于一個CPU 內(nèi)獨立的可執(zhí)行核心,在任意時刻,只能運行在某一個特權(quán)級上,這個特權(quán)級由CSR(控制和狀態(tài)寄存器)指定配置。

具體分級如下:

機器特權(quán)級(M):RISC-V 中 hart 可以執(zhí)行的最高權(quán)限模式。在M 模式下運行的 hart,對內(nèi)存、I/O 和一些必要的底層功能(啟動和系統(tǒng)配置)有著完全的控制權(quán)。它是唯一一個所有標(biāo)準(zhǔn)RISC-V CPU 都必須實現(xiàn)的權(quán)限級。

虛擬機監(jiān)視特權(quán)級(H):為了支持虛擬機監(jiān)視器而定義的特權(quán)級。

管理員特權(quán)級(S):主要用于支持現(xiàn)代操作系統(tǒng),如Linux、FreeBSD和 windows 等

用戶應(yīng)用特權(quán)級(U):用于運行應(yīng)用程序,同樣也適用于嵌入式系統(tǒng)。

特權(quán)級的存在,是給指令加上了權(quán)力,從而去控制指令編寫應(yīng)用程序。應(yīng)用程序只能干應(yīng)用程序該干的事情,不能越權(quán)操作。操作系統(tǒng)則擁有更高的權(quán)力,能對系統(tǒng)資源進行管理。

10. 總結(jié)

本文梳理了 芯片、CPU、流水線,指令與架構(gòu)等基礎(chǔ)概念,引出了RISC-V 基礎(chǔ)介紹,簡單介紹了RISC-V 由來。后續(xù)針對risc-v 會根據(jù)自身學(xué)習(xí)情況做相應(yīng)介紹。

審核編輯:劉清

-

控制器

+關(guān)注

關(guān)注

112文章

16444瀏覽量

179364 -

晶體管

+關(guān)注

關(guān)注

77文章

9744瀏覽量

138847 -

運算器

+關(guān)注

關(guān)注

1文章

164瀏覽量

16593 -

RISC-V

+關(guān)注

關(guān)注

45文章

2322瀏覽量

46552

原文標(biāo)題:適合新手的RISC-V入門基礎(chǔ)知識

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

IC設(shè)計工程師想了解的RISC-V知識點分享

RISC-V入門:模塊化開放式的ISA CISC和RISC代碼區(qū)別

關(guān)于RISC-V學(xué)習(xí)路線圖推薦

RISC-V單片機快速入門01-開發(fā)環(huán)境搭建 相關(guān)資料下載

如何入門RISC-V嵌入式

RISC-V基礎(chǔ)知識:模塊化開放式的ISA CISC和RISC代碼區(qū)別

適合新手的RISC-V入門基礎(chǔ)知識

初探RISC-V—《RISC-V體系結(jié)構(gòu)編程與實踐》

適合C語言小白看的基礎(chǔ)知識梳理總結(jié)

RISC-V如何填補CPU知識空白

關(guān)于risc-v啟動部分的思考

從零開始寫RISC-V處理器

RISC-V 簡介——理解 RISC 的開放式 ISA

RISC-V入門基礎(chǔ)知識梳理

RISC-V入門基礎(chǔ)知識梳理

評論