【摘要】

在某單板開發(fā)工作中,高速信號線非常多,為了保證單板的EMI性能,在PCB布線中,盡可能保證信號線走內(nèi)部信號層,防止因為過多表層高速信號線產(chǎn)生的EMC問題無法定位。但是該方案帶來的直接問題是高速信號線躍層過多,過孔較多,極大的增加了信號線的插入損耗,影響了信號完整性。在本單板設(shè)計中,為了兼顧性能和EMC,采取了反焊盤、電容下方挖地走線等方案改進了性能。

一、問題提出

該單板存在多組高速信號線:16路GE,4對5Gbps的QSGMII Serdes,4對2.5Gbps的Flexlink Serdes以及5對125MHZ的差分時鐘線,25MHZ,48MHZ,125MHZ單端時鐘各一組等,另外還包括16-54路左右的POE供電網(wǎng)絡(luò)等。考慮到后續(xù)的EMC情況,不可控因素非常多,所以為了保險起見,在PCB設(shè)計中嚴格遵照EMC要求來布局布線,并盡可能將高速信號線以距離管腳盡可能短的位置走過孔到內(nèi)部信號層。這樣導致的直接后果是高速信號線經(jīng)過的過孔較多,插入損耗較大,對于性能方面的影響是顯而易見的。 為兼顧EMC性能,高速信號線的過孔較多,尤其是5Gbps的SERDES信號對,一般都經(jīng)過了4個過孔,根據(jù)仿真結(jié)果,插入損耗理想情況下最大值達到了-10.4dB,而廠家給的插入損耗閾值僅有-12.5dB,已經(jīng)非常接近閾值,對于高速信號的數(shù)據(jù)傳送性能造成了極大的隱患。 通過EDA仿真,以及查閱相關(guān)資料,目前的優(yōu)化方案主要有以下三種: ?反焊盤 ?Stub 長度優(yōu)化 ?電容下方挖地

二、優(yōu)化方案

1. 反焊盤

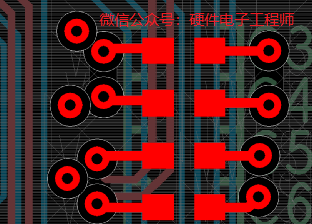

反焊盤指的是負片中銅皮與焊盤的距離。在高速PCB設(shè)計中,較大的反焊盤尺寸和較低的介電常數(shù)材料可以減少電容負載,從而可以降低過孔阻抗,減小傳輸延時。在該單板中,主要針對5Gbps的QSGMII SERDES差分對采用反焊盤處理。本單板使用的反焊盤示例如圖2-1所示,

圖2-1 反焊盤示例

通過對本板的仿真,采用反焊盤技術(shù)效果極為明顯,仿真數(shù)據(jù)如表2-1所示。

表2-1 反焊盤插入損耗仿真數(shù)據(jù)

Via typeUndo VIARound Anti-Pad

Frequency5GHz5GHz

Insertion Loss(dB)-1.4050-0.9430

2.STUB長度優(yōu)化

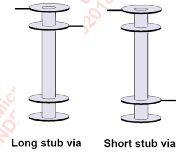

STUB指殘端效應(yīng)。在PCB設(shè)計中,往往為了降低成本,過孔都做成了通孔形式。在此情況下,從信號通過過孔到另一個信號層,往往信號在過孔的中間,過孔還殘余一部分,這一部分殘端即為STUB。STUB形成了一個天然的天線,它既可以發(fā)射信號,也可以接收干擾信號,造成對信號完整性的危害。STUB還會給PCB走線增加特性阻抗,并且減少走線的自身阻抗,對于高速信號線存在任何的stub都是不完美的。如果一個open stub是1/2波長,則其就等效于走線上的一個對地電容;而如果short stub是1/2波長,其相對于在一個走線上加上一個電感。STUB如圖2-2所示

圖2-2 STUB對比

在實際應(yīng)用中,尤其是高速信號線的過孔,一般會采用埋孔來消除STUB影響,也有會通過鉆孔處理,在單板完成后,將STUB部分挖除。 在本板中,考慮到成本及工藝方法,使用的過孔完全是通孔,所以STUB的問題無法規(guī)避,只能在每對差分對的過孔處添加GND孔,降低回流阻抗。

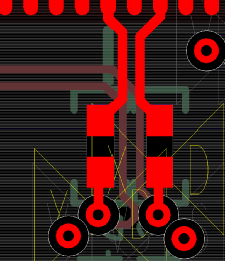

3.電容下方挖空處理

電容下方地平面挖空處理也是一種非常有效的方法,電容挖空主要解決的是電容不連續(xù)問題。在高速差分串行布線中,電容不連續(xù)是最常見的問題,主要問題是由于PAD和參考平面之間形成的寄生電容。而電容不連續(xù)極易產(chǎn)生插入損耗。 減小寄生電容的最常見方式是挖空PAD下方的參考平面,尤其是對于差分對中的AC耦合電容,效果尤其明顯。在本次單板的PCB設(shè)計中,對于仿真結(jié)果最差的差分線執(zhí)行了電容下方挖空處理。如圖2-3所示:

圖2-3 電容下方挖空處理

而通過對本單板進行仿真,得到的仿真結(jié)果如表2-3所示:

表2-3 電容下方挖空仿真結(jié)果

Via type未掏空掏空

Frequency5GHz5GHz

Insertion Loss(dB)-1.2467-0.8363

三、仿真結(jié)果對比

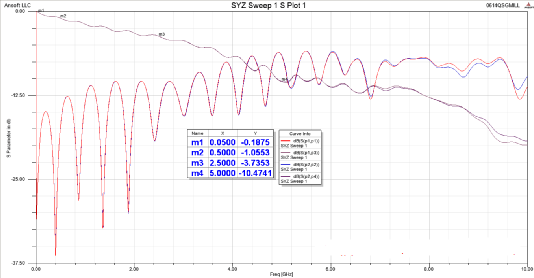

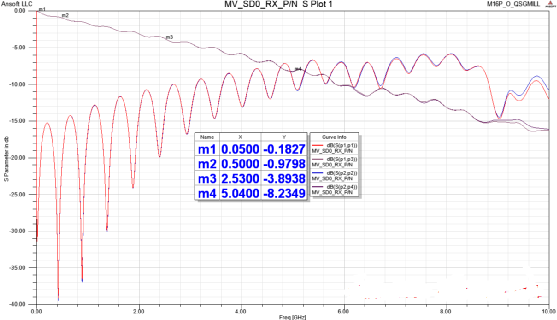

如前所述,考慮到QSGMII接口速率較高,達到了5Gbps,同時有的差分對達到了4個過孔,并且最長走線達到了5000mil,很難保證最終的性能。所以為了保證插入損耗優(yōu)化,綜合采用了反焊盤及電容下挖空處理方案。如圖3-1所示,為原始未作任何處理情況下的仿真結(jié)果,該仿真對象為走線最差的MV_SD0_RX_P/N差分對,由下圖可見,隨著頻率增加,插入損耗越大,在5GHZ情況下,插入損耗達到了最差的-10.4741dB,與官方提供的閾值-12.5dB已經(jīng)非常接近了。

圖3-1 原始最差路徑

插入損耗在綜合采用了反焊盤,電容下挖空處理以及過孔處打地孔形成回流路徑等手段后,得到的仿真結(jié)果如圖3-2所示:

圖3-2 處理后仿真結(jié)果

由上圖可見,經(jīng)過處理的走線插入損耗降低到了-8.2349dB,相對處理前降低了2.2392dB,插入損耗降額效果還是比較理想的。

四、總結(jié)

隨著通信系統(tǒng)的越來越復雜,速率越來越高,高速信號的各種性能要求會越來越高,遇到的問題也會越來越復雜。本次單板開發(fā)中,針對高速信號的插入損耗問題,在PCB布局和布線中,應(yīng)用反焊盤,電容下方挖空,回流地孔等各種綜合解決方案較有效的提高了插入損耗問題。本次實踐是對于插入損耗問題的一次有效嘗試,對于后續(xù)的開發(fā)具有一定的實踐和借鑒意義。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4323文章

23128瀏覽量

398729 -

emc

+關(guān)注

關(guān)注

170文章

3936瀏覽量

183442 -

高速信號

+關(guān)注

關(guān)注

1文章

230瀏覽量

17722

發(fā)布評論請先 登錄

相關(guān)推薦

插入損耗如何能影響差分對的信號質(zhì)量

高速PCB設(shè)計之一 何為高速PCB設(shè)計

插入損耗對差分對的信號質(zhì)量影響

EMI電源濾波器的插入損耗分析

【高速PCB設(shè)計】高速信號插入損耗性能優(yōu)化分析

【高速PCB設(shè)計】高速信號插入損耗性能優(yōu)化分析

評論