首先看下下面的這個(gè)示例:

module PU;

int A[2:0][3:0][4:0], B[2:0][3:0][4:0], C[5:0][4:0];

initial

begin

A[0][2][4] = 1024; //row 0, column 2, element #4

//display index #4 (i.e., 5th element)

$display("A[0][2][4]=",A[0][2][4]);

//display 5 elements of row 0, column 2

$display("A[0][2]=",A[0][2]);

//display row 0 (4 columns; 5 elements each)

$display("A[0]=",A[0]);

//display 3 rows * 4 columns of 5 elements each

$display("A=",A);

$display("

");

B[1][1][1]=512; //row 1; column 1; element #1

// assign a subarray composed of fve ints

A[2][3] = B[1][1];

//display 5 elements of row 2, column 3

$display("A[2][3]=",A[2][3]);

B[0][0][0]=128; //Assign only to the last unpacked element

A[1] = B[0];

$display("

");

$display("A[1]=",A[1]); //display row 1 (4 columns; 5

elements each)

C[5][4]=64;

A[0][1] = C[5];

$display("

");

$display("C[5]=",C[5]);

$display("A[0][1]=",A[0][1]);

end

endmodule

仿真log:

A[0][2][4]= 1024 //index #4 (i.e., 5th element)

A[0][2]='{1024, 0, 0, 0, 0} //5 elements of row 0, column 2

A[0]='{'{0, 0, 0, 0, 0}, '{1024, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}

//4 columns of row 0 with value assigned to column 2, element #4 (5th position)

A='{'{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0,

0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0, 0}, '{1024, 0, 0,

0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}}

//Entire 3 rows*4 columns (12 entries – 5 elements each with value assigned to

column 2, element #5)

A[2][3]='{0, 0, 0, 512, 0} // display 5 elements of row 2, column 3

A[1]='{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 128}}

// display row 1 (4 columns; 5 elements each)

C[5]='{64, 0, 0, 0, 0} //Row 5, 5 elements with index 4 assigned

A[0][1]='{64, 0, 0, 0, 0} //Row 0, column 1 of 5 elements

V C S S i m u l a t i o n R e p o r t

Packed和Unpacked數(shù)組作為子程序的參數(shù)

數(shù)組可以作為參數(shù)傳遞給子程序,當(dāng)數(shù)組作為值傳遞給子程序時(shí),會(huì)將這個(gè)數(shù)組復(fù)制一份傳遞給子程序。

task trial (int a[3:1][3:1]); //’a’ is a two-dimensional array

//(2-D unpacked)

上面是一個(gè)SystemVerilog task聲明的示例,該task會(huì)將一個(gè)2維unpacked數(shù)組作為參數(shù)值傳遞。

int b[3:1][3:1]; // OK: same type, dimension, and size

int b[1:3][0:2]; // OK: same type, dimension, & size

// (different ranges)

logic b[3:1][3:1]; // ERROR: incompatible element type

// (logic vs. int)

event b[3:1][3:1]; // ERROR: incompatible type (event

vs. int)

int b[3:1]; // ERROR: incompatible number of dimensions

int b[3:1][4:1]; // ERROR: incompatible size (3 vs. 4)

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110154 -

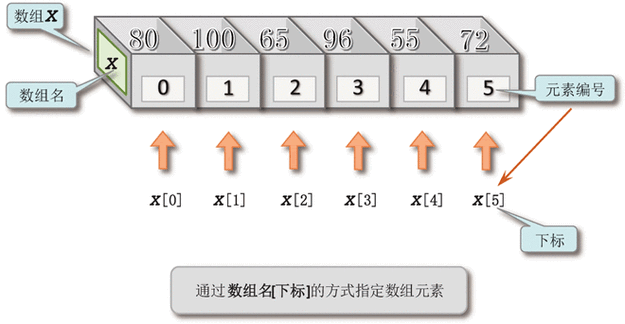

數(shù)組

+關(guān)注

關(guān)注

1文章

417瀏覽量

25978

原文標(biāo)題:SystemVerilog中數(shù)組的賦值、索引和切片

文章出處:【微信號(hào):芯片驗(yàn)證工程師,微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Labivew 實(shí)現(xiàn)鼠標(biāo)在數(shù)組中選中元素時(shí),精準(zhǔn)的顯示所在位置的行、列值方法

數(shù)組名之間可以直接賦值嗎

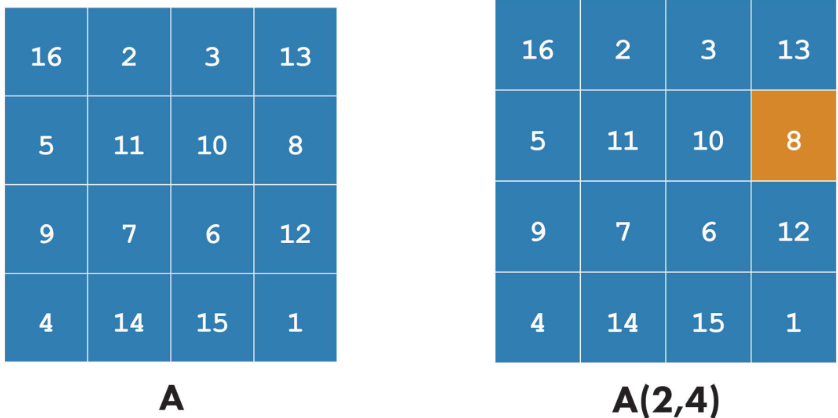

MATLAB中的矩陣索引

labview字符串數(shù)組轉(zhuǎn)化為數(shù)值數(shù)組

一文了解MySQL索引機(jī)制

嵌入式中零長(zhǎng)度數(shù)組基本操作方法

深入探索KUKA KRL中的數(shù)組應(yīng)用

隨機(jī)抽取SV數(shù)組中的一個(gè)元素方法實(shí)現(xiàn)

在Vivado Synthesis中怎么使用SystemVerilog接口連接邏輯呢?

SystemVerilog中數(shù)組的賦值、索引和切片

SystemVerilog中數(shù)組的賦值、索引和切片

評(píng)論