timing check

描述設計時序時,所有的時序檢查都有一個參考事件(reference event)和一個數據事件(data event),數據事件常常是數據信號,而參考事件常常是時鐘信號,它們通過一個布爾表達式相聯接,還包括一個可選的notifier寄存器選項,這個寄存器用來打印錯誤信息或者傳播X態。

檢查時序窗口的穩定性,包括:setup、hold、setuphold、recovery、removal和recrem。

$setuphold

$setuphold(reference_event, data_event, setup_limit,hold_limit, notifier, [timestamp_cond, timecheck_cond,delayed_reference_signal, delayed_data_signal]);

其中setup limit 和hold limit 的數值是從SDF 文件取出反標到網表上的。

$setup (data_event, reference_event, limit, notifier);

當reference_event time - limit < data_event time < reference_event time時,就會報告setup time violations。

$hold (reference_event, data_event, limit, notifier);

當reference_event time < data_event time < reference_event time + limit時,就會報告hold time violations。

$setuphold (reference_event, data_event, setup_limit, hold_limit, notifier);

setup和$hold 兩者的聯合。

例如:

setup (negedge d, posedge clk, 2, notifier); 和 $hold (posedge clk, negedge d, 1, notifier);

setup和hold都為正值:

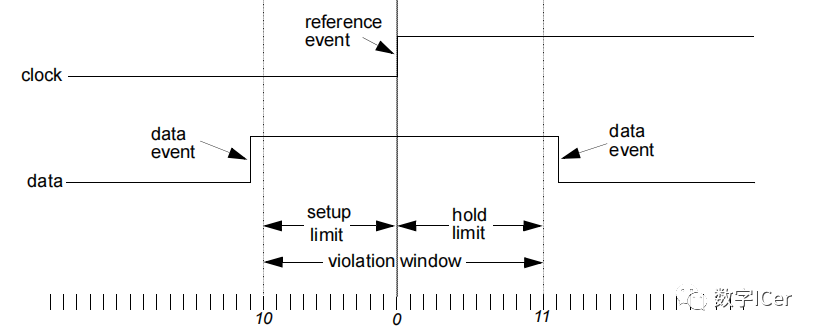

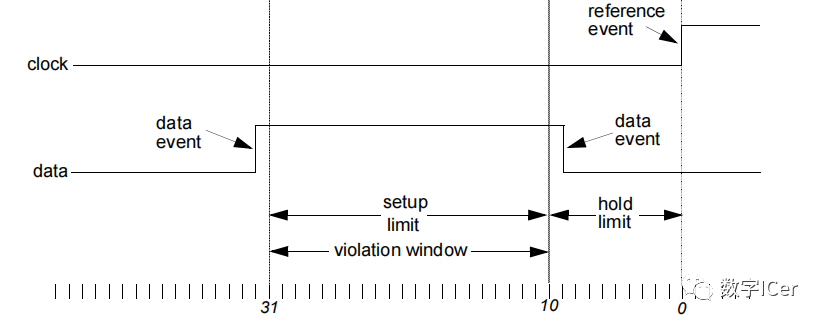

如下面例子 setup limit 和 hold limit 都為正值:

$setuphold (posedge clock, data, 10, 11, notifyreg);

其中,data要在時鐘上升沿10ns保持穩定(假設時間單位是ns),在clk上升沿之后11ns內保持穩定;如果在時鐘clk上升沿到來之前,data小于10ns或時鐘clk上升沿到來之之后小于11ns,則為時序違例;

Positive Setup and Hold Limits

上圖中,可見,

對于setup檢查Data Event 要早于 Clock Event;

對于hold 檢查Data Event 要晚于 Clock Event;

符合這種情況的時序,setup limit 和 hold limit 用正值來表示。

setup為負值,hold都為正值:

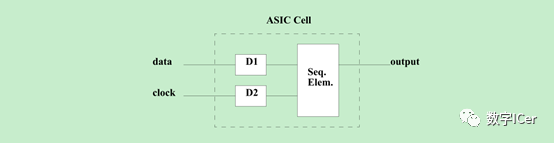

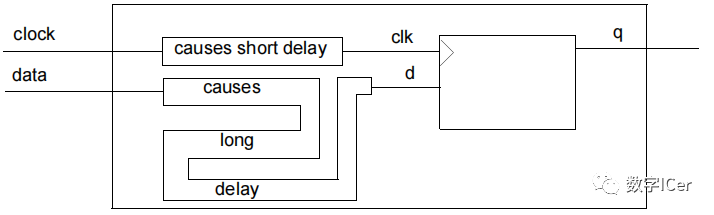

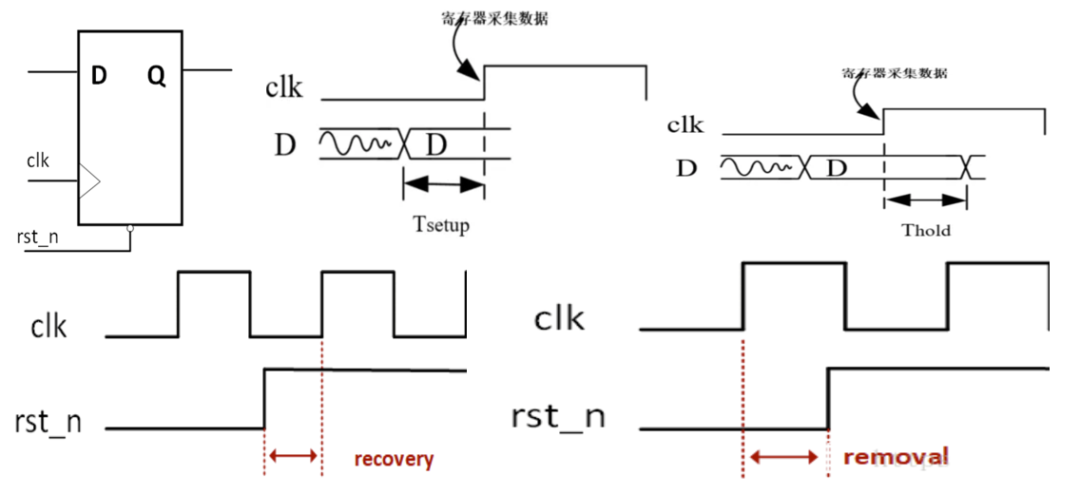

在討論這個問題之前需要弄明白,我們現在所說的setup hold timing check是針對std cell的,在實際的std cell中不僅僅有DFF還有一些buffer之類的cell。

一個典型的std cell的簡化結構如上圖所示,D1和D2表示兩個delay cell。而實際上我們要保證的是DFF的setup 和hold timing check是正值,由于D1和D2兩個cell的delay不同就導致了在對std cell做timing check時出現了負值的timing check。再次強調,這里的負值的timing check是針對std cell的并不是針對DFF的。

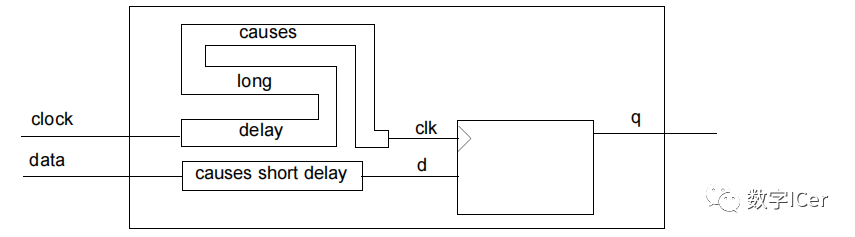

當標準單元內部clk上有較長的延遲時,對于setup檢查Data Event就可以晚一些來,如果晚于Clock Event(時刻為 0),用負值來表示。

$setuphold (posedge clock, data, -10, 31, notifyreg);

Negative Setup Limit

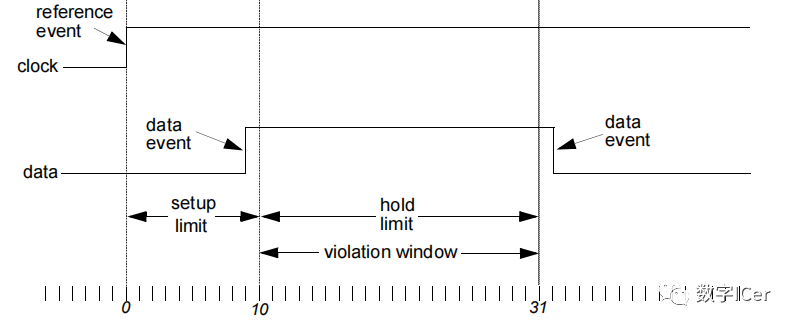

setup為正值,hold都為負值:

當標準單元內部data上有較長的延遲時,對于hold檢查Data Event就需要早一些來,如果早于Clock Event(時刻為 0),用負值來表示。$setuphold (posedge clock, data, 31, -10, notifyreg);

Negative Hold Limit

需要注意的是不論setup 或者hold出現負值,但setup和hold的和必須是正值。這是因為setup必然要發生在hold的前面。

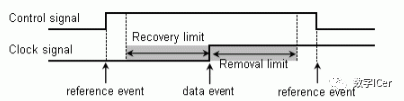

$recrem

復位信號的恢復時間檢查:

$recovery (reference_event, data_event, limit, notifier);

當data_event time - limit < reference_event time < data_event time時,就會報告recovery time violations。

復位信號的移除時間檢查

$removal (reference_event, data_event, limit, notifier);

當data_event time < reference_event time < data_event time + limit時,就會報告removal time violations。

復位信號的恢復/移除時間檢查:

$recrem (reference_event, data_event, recovery_limit, removal_limit, notifier);

$recrem是$recovery和$removal兩者的聯合。

recovery (posedge clr, posedge clk, 2, notifier); 和 $removal (posedge clr, posedge clk, 3, notifier);

數據事件常常是時鐘信號,而參考事件常常是控制信號,比如清除信號或者置位信號,如下圖:

啟用負時序檢查

當時序存在負值時,必須要用 recrem 來表示;而不能用單獨的 hold,removal;

同時使用負時序檢查,必須在編譯設計時包含+neg_tchk和-negdelay選項。如果省略此選項,VCS將將所有負限制更改為0。

如果在+neg_tchk選項中包含 +no_notifier選項,則表示notifer寄存器不進行翻轉,X態不會傳播,但是vcs還是會報告timing violation;

相反,如果在+neg_tchk選項中包含+no_tchk_msg選項,則vcs不報告timing violation。但VCS仍然會創建時鐘和數據信號的延遲,并在存在時序違例時翻轉notifer寄存器。

+notimingcheck 表示在vcs編譯過程中不進行 setuphold,recrem 等函數的編譯,vcs產生delayed_reference_signal 和delayed_reference_data但是不會去標記這些delay的值,從而不進行任何的timing檢查。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5357瀏覽量

120675 -

VCS

+關注

關注

0文章

80瀏覽量

9625 -

時鐘信號

+關注

關注

4文章

449瀏覽量

28590 -

dff

+關注

關注

0文章

26瀏覽量

3424

原文標題:負時序檢查 Negative Timing Checks

文章出處:【微信號:數字ICer,微信公眾號:數字ICer】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

UltraFast設計方法時序收斂快捷參考指南

什么是時序分析?教你掌握FPGA時序約束

無法檢查啟用中斷

時序約束的步驟分析

VIVADO中時序報告中WNS、WHS、TNS、THS有什么含義

啟用負時序檢查的步驟

啟用負時序檢查的步驟

評論