副標(biāo)題-FPGA高層次綜合HLS(二)-Vitis HLS知識庫

高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動轉(zhuǎn)換成低抽象級語言描述的電路模型的過程。

對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

官方指南:

https://docs.xilinx.com/r/_lSn47LKK31fyYQ_PRDoIQ/root

重要術(shù)語

LUT 或 SICE

LUT 或 SICE是構(gòu)成了 FPGA 的區(qū)域。它的數(shù)量有限,當(dāng)它用完時,意味著您的設(shè)計太大了!

BRAM 或 Block RAM

FPGA中的內(nèi)存。在 Z-7010 FPGA上,有 120 個,每個都是 2KiB(實(shí)際上是 18 kb)。

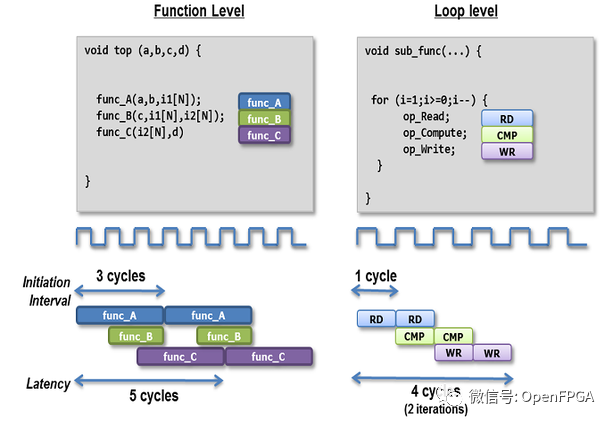

Latency延遲

設(shè)計產(chǎn)生結(jié)果所需的時鐘周期數(shù)。

循環(huán)的延遲是一次迭代所需的時鐘周期數(shù)。

Initiation Interval (or II, or Interval間隔)

在接受新數(shù)據(jù)之前必須執(zhí)行的時鐘周期數(shù)。

這與延遲不同!如果函數(shù)是流水線的,許多數(shù)據(jù)項(xiàng)會同時流過它。延遲是一個數(shù)據(jù)項(xiàng)被推入后彈出的時間,而時間間隔決定了數(shù)據(jù)可以被推入的速率。

循環(huán)的間隔是可以開始循環(huán)迭代的最大速率,以時鐘周期為單位。

上圖中,左邊是函數(shù)右邊是循環(huán),左邊的時間間隔(接收新數(shù)據(jù)之前)是3個時鐘周期,右邊循環(huán)的間隔則是一個時鐘周期;對于左邊的延遲是這個函數(shù)產(chǎn)生結(jié)果的時鐘周期數(shù),是func_C運(yùn)行完畢產(chǎn)生的周期數(shù),為5個時鐘周期,右邊循環(huán)的延遲是一次迭代所需的時鐘數(shù),是4個時鐘周期。

上面的概念非常重要,要不然下面的一些指令作用也看不懂~

重要的指令

這是在實(shí)際使用過程中重要的指令列表(不是全部)。

Functions-函數(shù)

loops-循環(huán)

Various-所有都適合

Arrays-數(shù)組

| 指令 | 適用范圍 | 描述 |

|---|---|---|

| PIPELINE 流水線指令 | Functions, loops | 簡單解釋就是使輸入更頻繁地傳遞給函數(shù)或循環(huán)。流水線后的函數(shù)或循環(huán)可以每 N 個時鐘周期處理一次新輸入,其中 N 是啟動間隔(Initiation Interval)。'II' 默認(rèn)為 1,是 HLS 應(yīng)針對的啟動間隔(即嘗試將新數(shù)據(jù)項(xiàng)輸入管道的速度應(yīng)該多快)。 |

| UNROLL | loops | 創(chuàng)建循環(huán)的因子副本,讓其并行執(zhí)行(如果滿足數(shù)據(jù)流依賴性)。但是會浪費(fèi)資源(以資源換取速度)。盡可能將程序展開以提高速度。 |

| ALLOCATION | Various | 限制某事物的實(shí)例數(shù)。例如,如果只想在另一個函數(shù)toplevel中獲得函數(shù)foo的三個副本,請使用位置toplevel、限制設(shè)置為3、實(shí)例設(shè)置為foo、類型設(shè)置為“function”的分配。這也適用于特定的運(yùn)算。 |

| ARRAY_MAP | Arrays | 將多個較小的陣列映射成一個較大的陣列,以犧牲訪問時間為代價來節(jié)省訪問邏輯或 BRAM。'instance' 可以設(shè)置為任何未使用的名稱。ARRAY_MAP 對同一個實(shí)例使用多個 來告訴 HLS 創(chuàng)建一個名為“instance”的新數(shù)組,其中包含所有較小的數(shù)組。保留“偏移”未設(shè)置。請注意,有些人在將三個或更多初始化數(shù)組映射到單個 RAM 時遇到了此指令引起的錯誤。如果在仿真和實(shí)現(xiàn)的設(shè)計之間遇到行為差異,請嘗試刪除此指令。 |

| ARRAY_PARTITION | Arrays | 將一個大數(shù)組拆分為多個較小的數(shù)組(與ARRAY_MAP相反)。這對于增加并行訪問的可能性很有用。如果“type”是“block”,則源數(shù)組將分成block。如果它是“cyclic”,那么元素將被交錯到目標(biāo)數(shù)組中。在這兩種情況下,“factor因子”都是要創(chuàng)建的較小數(shù)組的數(shù)量。如果 'type' 是 'complete' 則忽略 'factor' 并且陣列被完全分割成組件寄存器,因此不使用任何 Block RAM。 |

| DATAFLOW | Functions | 見下文 |

| INLINE | Functions | 該指令不是將函數(shù)視為單個硬件單元,而是在每次調(diào)用 HLS 時將函數(shù)內(nèi)聯(lián)。這是以硬件為代價增加了潛在的并行性。如果 'recursive' 為真,則內(nèi)聯(lián)函數(shù)調(diào)用的所有函數(shù)也被視為標(biāo)有 INLINE。 |

| INTERFACE | Function,parameters | 告訴 HLS 如何在函數(shù)之間傳遞參數(shù)。這在頂層函數(shù)中至關(guān)重要,因?yàn)樗x了設(shè)計的引腳排列。在 EMBS 中,我們有一個應(yīng)該堅(jiān)持使用的模板(上圖)。 |

| LATENCY | Functions, loops | HLS 通常會嘗試在綜合時實(shí)現(xiàn)最小延遲。如果使用此指令指定更大的最小延遲,HLS 將“pad out”函數(shù)或循環(huán)并減慢一切。這有助于資源共享(減少資源),并且對于創(chuàng)建延遲很有用。如果 HLS 無法達(dá)到要求的延遲,它將發(fā)出警告。 |

| LOOP_FLATTEN | loops | 將嵌套循環(huán)展平為單個循環(huán)。應(yīng)用于 最里面的 循環(huán)。如果成功,將生成更快的硬件代碼。 |

| LOOP_TRIPCOUNT | loops | 如果循環(huán)具有可變的循環(huán)邊界,HLS 將不知道它需要多少次迭代。這意味著它無法為設(shè)計延遲提供明確的值。這允許我們?yōu)樵O(shè)計指定循環(huán)的最小、平均和最大行程計數(shù)(迭代次數(shù))。這只會影響報告,不會影響硬件代碼生成。 |

| RESOURCE | Various | 這用于指定應(yīng)使用特定硬件資源來實(shí)現(xiàn)源代碼元素。指定是否應(yīng)使用 BRAM 或 LUT 實(shí)現(xiàn)ARRAY。見下文詳解。 |

任意精度類型

可以在 HLS 中使用普通的 C 類型(int、 char等)變量。但是,設(shè)計中的常用的寄存器并不完全需要 4、8 或 16 位寬,那么可以使用任意精度類型來準(zhǔn)確定義需要多寬的數(shù)據(jù)類型,而不是接受這種低效率的通用定義。

下面展示了如何使用 C 和 C++ 風(fēng)格的任意精度類型。我們建議使用 C++,除非有特定的理由不這樣做。

在 C 中:

包含

| uint5 x | 無符號整數(shù),5 位寬 |

|---|---|

| int19 x | 有符號整數(shù),19 位寬 |

在 C++ 中:

包含

| ap_uint<5> x | 無符號整數(shù),5 位寬 |

|---|---|

| ap_int<19> x | 有符號整數(shù),19 位寬 |

按照上面的設(shè)置應(yīng)該能夠正常打印任意精度類型,但是如果在調(diào)試過程中得到奇怪的值,請先使用printf調(diào)用to_int():

ap_uint<23>myAP;

printf("%d

",myAP.to_int());

復(fù)位行為

在 HLS 中,所有靜態(tài)和全局變量都被初始化為零(如果給定了初始化值,則初始化為其他值)。這包括 RAM,其中每個元素都被清除為零。然而,這種初始化只發(fā)生在 FPGA 首次編程時。任何后續(xù)處理器復(fù)位都不會觸發(fā)初始化過程。

如果需要清除設(shè)備的內(nèi)部狀態(tài),那么應(yīng)該包含某種復(fù)位協(xié)議(根據(jù)復(fù)位狀態(tài)處理所需要的程序)。

AXI 從接口和 AXI 主接口

可以在 HLS 組件中使用兩個接口,即 AXI Slave 和 AXI Master。

AXI Slave:ARM 內(nèi)核使用此接口來啟動和停止 HLS 組件。他們還可以使用此接口來讀取和寫入相對少量的用戶定義值。

AXI Master:如果需要更大量的共享數(shù)據(jù),HLS 組件可以使用 AXI Master 接口啟動事務(wù)以從主系統(tǒng)內(nèi)存讀取和寫入數(shù)據(jù)。

可以通過toplevel在 HLS 組件中為函數(shù)指定參數(shù)并將指令附加到這些參數(shù)來定義所需的接口。下面顯示了一個只有從接口的組件:

帶有AXI Slave的 HLS 組件

uint32toplevel(uint32*arg1,uint32*arg2,uint32*arg3,uint32*arg4){

#pragmaHLSINTERFACEs_axiliteport=arg1bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg2bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg3bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg4bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=returnbundle=AXILiteSregister

}

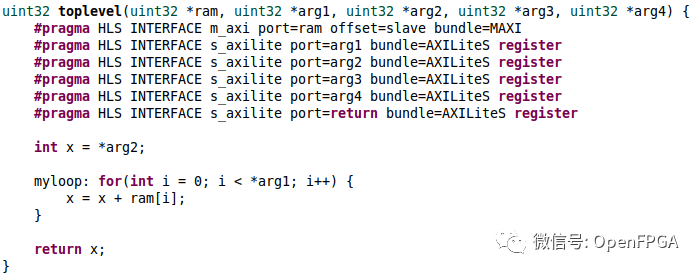

而下面是一個同時具有從接口和主接口的組件:

具有從屬和主接口的 HLS 組件

uint32toplevel(uint32*ram,uint32*arg1,uint32*arg2,uint32*arg3,uint32*arg4){

#pragmaHLSINTERFACEm_axiport=ramoffset=slavebundle=MAXI

#pragmaHLSINTERFACEs_axiliteport=arg1bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg2bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg3bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=arg4bundle=AXILiteSregister

#pragmaHLSINTERFACEs_axiliteport=returnbundle=AXILiteSregister

}

請注意,可以為從接口添加和刪除參數(shù),并更改它們的數(shù)據(jù)類型,只需記住也要更新關(guān)聯(lián)#pragmaS。HLS 將相應(yīng)地更新組件的驅(qū)動程序。

PS:主數(shù)據(jù)類型:由于 AXI 主接口會連接到 32 位寬的 RAM,因此在指定 AXI 主接口時應(yīng)始終使用 32 位數(shù)據(jù)類型。

一旦決定了的接口,應(yīng)該能夠依靠 Vivado 自動化連線來連接一切。

請注意,返回端口的 pragma 很重要!

#pragmaHLSINTERFACEs_axiliteport=returnbundle=AXILiteSregister //端口=返回包=AXILiteS寄存器

即使不使用函數(shù)的返回值,此 pragma 也會告訴 HLS 將 start、stop、done 和 reset 信號捆綁到 AXI Slave 接口中的控制寄存器中。因此,這將生成相應(yīng)的驅(qū)動程序函數(shù)來啟動和停止生成的 IP 內(nèi)核。如果不包含此 pragma,則 HLS 將為這些信號生成簡單的連線,并且 IP 內(nèi)核將無法直接被 ARM 內(nèi)核控制。

多種類型的 AXI Master

Vitis HLS在從同一主AXI端口復(fù)制值并將其解釋為不同類型時非常挑剔。

例如,以下 memcpy 可能會導(dǎo)致“Stored value type does not match pointer operand type! (存儲值類型與指針操作數(shù)類型不匹配!)” ,嘗試將 RAM 視為uint32 和float類型時,綜合過程中將會產(chǎn)生 LLVM 錯誤:

voidtoplevel(uint32*ram){ #pragmaHLSINTERFACEm_axiport=ramoffset=slavebundle=MAXI uint32u_values[10]; floatf_values[10]; memcpy(u_values,ram,40); memcpy(f_values,ram+10,40); }

為了正確強(qiáng)制從 RAM 中復(fù)制數(shù)據(jù)的類型信息,可以使用union,如下所示:

typedefunion{

uint32u;

floatf;

}ram_t;

voidtoplevel(ram_t*ram){

#pragmaHLSINTERFACEm_axiport=ramoffset=slavebundle=MAXI

uint32u_values[10];

floatf_values[10];

for(inti=0;i

此外,只要循環(huán)邊界從零開始(并且是固定的),HLS應(yīng)該足夠聰明,將其視為類似于memcpy的突發(fā)傳輸-在綜合過程中查找“推斷MAXI端口上長度為X的總線突發(fā)讀取”來證實(shí)這一點(diǎn)。

強(qiáng)制和阻止使用 Block RAM

HLS 會自動將大部分ARRAY轉(zhuǎn)換為 BRAM。這通常很有用,因?yàn)榧拇嫫鰽RRAY在 LUT(FPGA 空間)方面非常昂貴。但是,F(xiàn)PGA 的 BRAM 數(shù)量有限。BRAM 也只有 2 個訪問端口。這意味著在任何時候最多有兩個并行進(jìn)程可以訪問 RAM。這可能會限制設(shè)計的并行性潛力。

如果HLS使用的是不希望使用的BRAM,則將類型設(shè)置為COMPLETE且維度設(shè)置為1的指令array_PARTITION應(yīng)用于數(shù)組。這將迫使它從寄存器中生成數(shù)組。這會占用大量的FPGA空間(LUT),所以要節(jié)約!

要強(qiáng)制 HLS 使用 BRAM,請將指令BIND_STORAGE集應(yīng)用到 RAM_2P。(添加時按下幫助按鈕可查看所有各種選項(xiàng)的說明)。

該 ARRAY_MAP 指令(見上文)可以通過自動將多個較小的數(shù)組放入一個較大的數(shù)組來幫助節(jié)省 Block RAM。

當(dāng)更改 HLS 時

當(dāng)更改 HLS 代碼時,請執(zhí)行以下步驟以確保bitfile已更新,方便進(jìn)行正確地測試。

1、重新運(yùn)行綜合。

2、重新導(dǎo)出 IP 核。

3、在 Vivado 中,它應(yīng)該已經(jīng)注意到了變化,并且會出現(xiàn)一條消息說“IP Catalog is out-of-date”。a、如果沒有,請單擊 IP Status,然后單擊重新運(yùn)行報告

b、單擊刷新 IP 目錄

c、在 IP Status面板中,應(yīng)選擇 toplevel IP。單擊 Upgrade 選項(xiàng)。

4、在“Generate Output Products”對話框中,單擊“Generate”。

5、單擊生成比特流。

6、導(dǎo)出硬件到 Vitis。

7、在 Vitis 中重新編程 FPGA 并運(yùn)行軟件。

現(xiàn)在應(yīng)該明白了為什么測試和仿真如此重要了!

循環(huán)優(yōu)化

在 HLS 中,可以將指令應(yīng)用于循環(huán)以指示它展開或流水線。考慮以下循環(huán):

myloop:for(inti=0;i

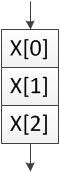

默認(rèn)情況下,HLS 將按順序執(zhí)行循環(huán)的每次迭代。它的執(zhí)行將如下所示:

如果循環(huán)的每次迭代需要 10 個時鐘周期,那么循環(huán)總共需要 30 個周期才能完成。

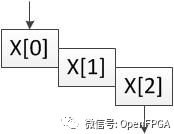

如果我們給這個循環(huán) PIPELINE 指令,那么 HLS 將嘗試在元素 0 完成之前開始計算元素 1,從而創(chuàng)建一個PIPELINE。這意味著循環(huán)的整體執(zhí)行時間會更短,但代價是更復(fù)雜的控制邏輯和更多的寄存器來存儲中間數(shù)據(jù)。循環(huán)如下所示:

只有在沒有阻止此優(yōu)化的依賴項(xiàng)時,它才能執(zhí)行此操作。考慮以下代碼:

intlastVal;

for(inti=0;i

在此示例中,循環(huán)被迫按順序執(zhí)行,因?yàn)樵谙乱淮窝h(huán)迭代開始時需要在循環(huán)體末尾使用計算出的值。PIPELINE 仍然會試圖加快速度,但不會大幅加快。

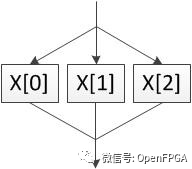

最后,如果我們給循環(huán) UNROLL 指令,那么 HLS 將嘗試并行執(zhí)行循環(huán)的迭代。這需要更多的硬件,但速度非常快。在我們的示例中,整個循環(huán)只需要 10 個周期。

這要求循環(huán)的元素之間沒有數(shù)據(jù)依賴關(guān)系。例如,如果 doSomething() 保留一個執(zhí)行次數(shù)的全局計數(shù)器,則此依賴項(xiàng)將阻止 UNROLL 指令工作。

請注意,UNROLL默認(rèn)情況下會嘗試展開循環(huán)的所有迭代。這可能會導(dǎo)致非常大的設(shè)計!為了使事情更合理,可以設(shè)置UNROLL的FACTOR參數(shù)來告訴工具要創(chuàng)建多少副本。

應(yīng)用UNROLL后,最好在分析視圖中查看它是否實(shí)際應(yīng)用。成功展開的設(shè)計在分析視圖中將非常“垂直”,表示同一列中的操作同時發(fā)生。如果視圖仍然非常“水平”且有很多列,那么很可能是數(shù)據(jù)依賴項(xiàng)阻止了展開。可以嘗試通過單擊操作來確定是什么阻止了展開。該工具將繪制箭頭以顯示輸入的內(nèi)容和輸出的內(nèi)容。請記住,BlockRAM 一次只能進(jìn)行兩次訪問,因此,如果有一個大型ARRAY,而這些工具是從 BlockRAM 制作的,則展開或流水線操作最多只能創(chuàng)建 2 個副本。可以告訴工具不要使用帶有ARRAY_PARTITION指令的塊RAM。這可以快得多,但要使用更多的硬件資源。

數(shù)據(jù)流優(yōu)化

如果沒有使用限制資源的指令(例如 ALLOCATION 指令),HLS 會尋求最小化延遲并提高并發(fā)性。但是數(shù)據(jù)依賴性可以限制這一點(diǎn)。例如,訪問數(shù)組的函數(shù)或循環(huán)必須在完成之前完成對數(shù)組的所有讀/寫訪問,這就阻止了下一個消耗數(shù)據(jù)的函數(shù)或循環(huán)啟動。

函數(shù)或循環(huán)中的操作可能會 在前一個函數(shù)或循環(huán)完成其所有操作之前開始操作。

HLS指定數(shù)據(jù)流優(yōu)化時:

分析順序函數(shù)或循環(huán)之間的數(shù)據(jù)流。

這允許函數(shù)或循環(huán)并行運(yùn)行,從而減少延遲并提高 RTL 設(shè)計的吞吐量,但以增加硬件資源為代價。嘗試一下DATAFLOW ,看看它是否對設(shè)計有幫助。

找不到 'crt1.o' 錯誤

當(dāng)試圖在實(shí)驗(yàn)室硬件以外的機(jī)器上運(yùn)行測試時,可能會收到一個錯誤,抱怨它找不到“crt1.o”。如果是這樣,就需要為項(xiàng)目設(shè)置自定義鏈接器標(biāo)志。

單擊頂部菜單中的“Project”,然后單擊Project Settings。在此框中,單擊左側(cè)的“Simulation”,然后將以下內(nèi)容粘貼到“Linker Flags”框中:

-B"/usr/lib/x86_64-linux-gnu/"

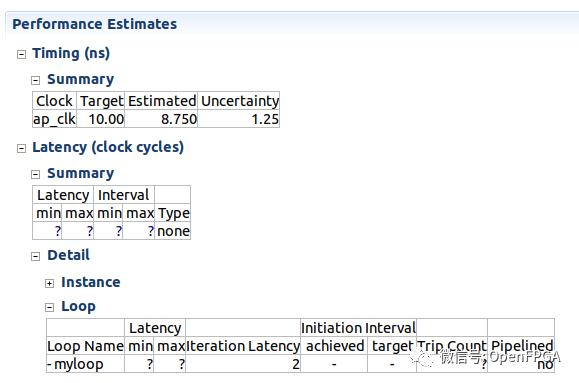

我的循環(huán)有???latency估計!

有時,HLS 綜合報告將包含?而不是給出最小和最大延遲的值。這是因?yàn)樵O(shè)計中至少有一個循環(huán)是數(shù)據(jù)相關(guān)的,即它循環(huán)的次數(shù)取決于 HLS 無法知道的數(shù)據(jù)值。

例如,下面的代碼:

當(dāng)綜合在綜合報告中給出以下內(nèi)容:

如果我們檢查代碼,它將來自ram的元素相加,但要相加的元素的確切數(shù)量來自用戶,作為arg1參數(shù)輸入。因此,HLS無法提前知道該硬件執(zhí)行需要多長時間,因?yàn)槊看芜\(yùn)行時它都是可變的。這就是上面我們說的運(yùn)行時依賴于數(shù)據(jù)。生成的硬件將正常工作,我們只是無法預(yù)測運(yùn)行需要多長時間。查看循環(huán)的細(xì)節(jié),HLS仍然可以告訴我們循環(huán)的延遲是2,換句話說,它不知道它將迭代多少次,但每次迭代將花費(fèi)2個時鐘周期。

一般來說,應(yīng)該盡量避免這種情況。如果 HLS 無法預(yù)測最壞的情況,那么它會過于“謹(jǐn)慎”,并且它可能會制造比我們需要的更大的硬件。此外,不能展開具有可變循環(huán)邊界的循環(huán)。

一些算法從根本上是依賴于數(shù)據(jù)的,如果這種情況無法避免,那么可以通過將LOOP_TRIPCOUNT指令添加到循環(huán)中來告訴 HLS ,假設(shè)循環(huán)將進(jìn)行給定次數(shù)的迭代,但這僅用于報告目的。生成的硬件將完全相同,但HLS將在循環(huán)迭代該次數(shù)的假設(shè)下生成延遲數(shù)。這意味著延遲數(shù)字不“正確”,但這仍然有助于了解其他優(yōu)化是否具有總體積極效果。

定點(diǎn)類型

當(dāng)需要使用小數(shù)運(yùn)算但又不想支付使用浮點(diǎn)的大量硬件成本時,定點(diǎn)類型很有用。Vitis HLS 用戶指南(https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_2/ug1399-vitis-hls.pdf)中詳細(xì)描述了定點(diǎn)類型,下面是一個簡短示例:

定點(diǎn)示例

#include

#include

ap_fixed<15,?5>a=3.45;

ap_fixed<15,?5>b=9.645;

ap_fixed<20,?6>c=a/b*2;

std::cout<

C標(biāo)準(zhǔn)數(shù)學(xué)函數(shù)(在math.h中)僅針對浮點(diǎn)實(shí)現(xiàn),但Xilinx在hls_math.h中提供了某些函數(shù)的定點(diǎn)實(shí)現(xiàn)。在hls::命名空間下;例如:hls::sqrt()、hls::cos()和hls::sin()。

此外,以下賽靈思示例代碼顯示了另一種定點(diǎn)平方根實(shí)現(xiàn),在某些情況下可能更有效。

fxp_sqrt.h

#ifndef__FXP_SQRT_H__

#define__FXP_SQRT_H__

#include

#include

usingnamespacestd;

/*

*Providesafixedpointimplementationofsqrt()

*Mustbecalledwithunsignedfixedpointnumberssoconvertbeforecalling,follows:

*ap_ufixed<32,?20>in=input_number;

*ap_ufixed<32,?20>out;

*fxp_sqrt(out,in);

*/

template

voidfxp_sqrt(ap_ufixed&result,ap_ufixed&in_val)

{

enum{QW=(IW1+1)/2+(W2-IW2)+1};//derivemaxrootwidth

enum{SCALE=(W2-W1)-(IW2-(IW1+1)/2)};//scale(shift)toadjinitialremainervalue

enum{ROOT_PREC=QW-(IW1%2)};

assert((IW1+1)/2<=?IW2);?//?Check?that?output?format?can?accommodate?full?result

???ap_uintq=0;//partialsqrt

ap_uintq_star=0;//diminishedpartialsqrt

ap_ints;//scaledremainderinitializedtoextractedinputbits

if(SCALE>=0)

s=in_val.range(W1-1,0)<>(0-(SCALE+1)))+1)>>1;

//Non-restoringsquare-rootalgorithm

for(inti=0;i<=?ROOT_PREC;?i++)?{

??????if?(s?>=0){

s=2*s-(((ap_int(q)<(q_star)<0)

q=q+1;

//Truncateexcessbitandassigntooutputformat

result.range(W2-1,0)=ap_uint(q>>1);

}

#endif

總結(jié)

這是《FPGA高層次綜合HLS》系列教程第二篇,后面會按照專題繼續(xù)更新,文章有什么問題,歡迎大家批評指正~感謝大家支持。

審核編輯:彭靜

-

Xilinx

+關(guān)注

關(guān)注

71文章

2167瀏覽量

121481 -

電路模型

+關(guān)注

關(guān)注

1文章

43瀏覽量

9566 -

Vitis

+關(guān)注

關(guān)注

0文章

146瀏覽量

7439

原文標(biāo)題:總結(jié)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA高層次綜合HLS之Vitis HLS知識庫簡析

使用Vitis HLS創(chuàng)建屬于自己的IP相關(guān)資料分享

基于知識庫的智能策略翻譯技術(shù)

領(lǐng)域知識庫的研究與設(shè)計

本體知識庫的模塊與保守擴(kuò)充

虛擬儀器知識庫文件的結(jié)構(gòu)組成和知識庫文件自動生成器的設(shè)計與應(yīng)用

復(fù)雜知識庫問答任務(wù)的典型挑戰(zhàn)和解決方案

基于Vitis HLS的加速圖像處理

Vitis HLS工具簡介及設(shè)計流程

Vitis HLS如何添加HLS導(dǎo)出的.xo文件

Vitis HLS知識庫總結(jié)

Vitis HLS知識庫總結(jié)

評論