隨著數(shù)據(jù)傳輸速率越來越高,現(xiàn)在計(jì)算機(jī)系統(tǒng)中的數(shù)據(jù)傳輸接口基本上都串行化了,像USB、PCIe、SATA、DP等等外部總線將并行總線擠壓到只剩下內(nèi)存總線這個(gè)最后的堡壘。當(dāng)然,就算是并行傳輸總線最后的倔強(qiáng)DDR也在不斷吸收SERDES上的技術(shù)來提升自己,尤其是均衡器(Equalization,EQ)技術(shù),在DDR5標(biāo)準(zhǔn)中,DRAM將被指定涵蓋DFE(判決反饋均衡)能力。

隨著信號(hào)速率的提高,在系統(tǒng)同步接口方式中,有幾個(gè)因素限制了有效數(shù)據(jù)窗口寬度的繼續(xù)增加。

時(shí)鐘到達(dá)兩個(gè)芯片的傳播延時(shí)不相等(clock skew)

并行數(shù)據(jù)各個(gè)bit 的傳播延時(shí)不相等(data skew)

時(shí)鐘的傳播延時(shí)和數(shù)據(jù)的傳播延時(shí)不一致(skew between data and clock)

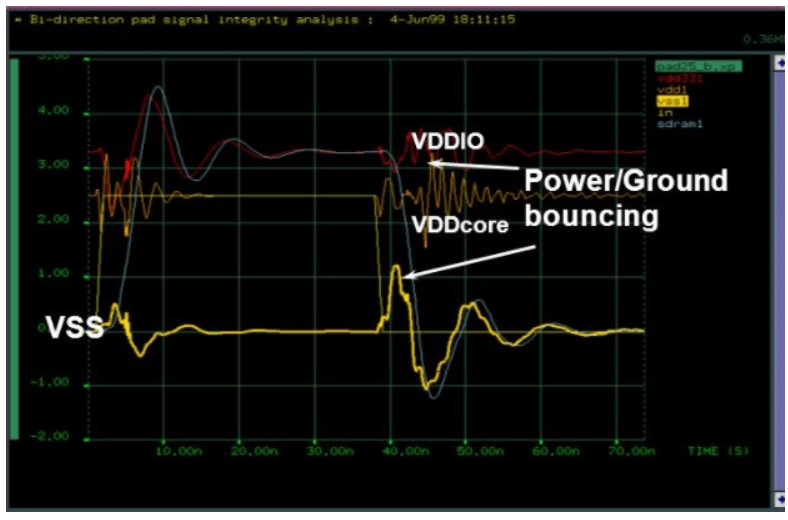

要提高接口的傳輸帶寬有兩種方式,一種是提高時(shí)鐘頻率,一種是加大數(shù)據(jù)位寬。那么是不是可以無限制的增加數(shù)據(jù)的位寬呢?這就要牽涉到另外一個(gè)非常重要的問題–同步開關(guān)噪聲(SSN),數(shù)據(jù)位寬的增加,SSN 成為提高傳輸帶寬的主要瓶頸。

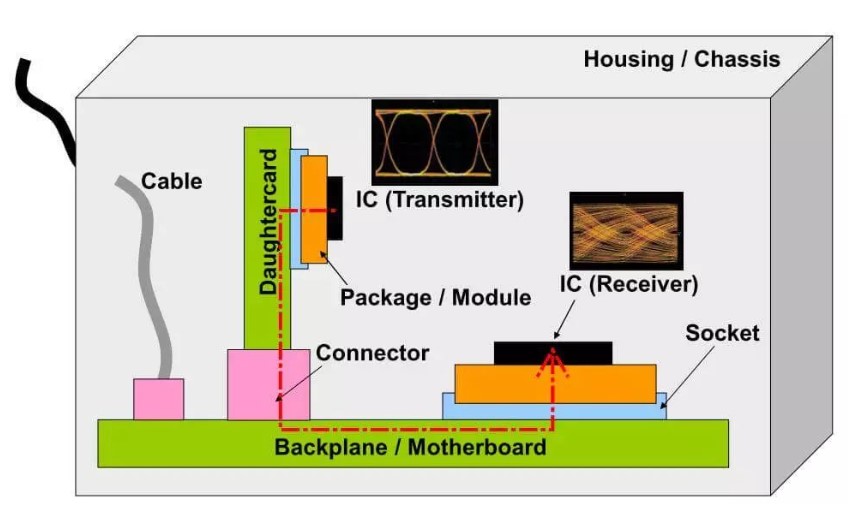

由于信道的非理想特性,信號(hào)從Tx通過FR4 PCB板傳輸?shù)絉x,這中間會(huì)有信號(hào)插損、回?fù)p、近/遠(yuǎn)端串?dāng)_,再繼續(xù)提高頻率,信號(hào)會(huì)嚴(yán)重失真,這就需要采用均衡和數(shù)據(jù)時(shí)鐘相位檢測(cè)等技術(shù),這也就是SerDes所采用的技術(shù)。

單端信號(hào)和差分信號(hào)之間的差異

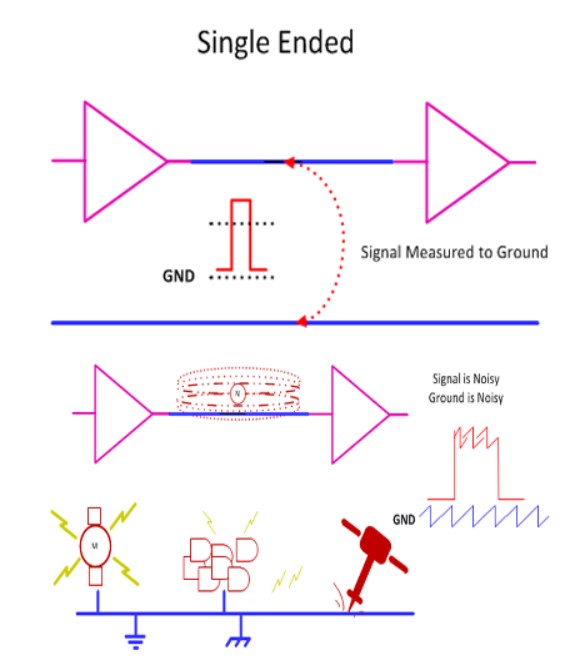

單端信號(hào)即用一根走線來傳輸信號(hào),信號(hào)由相對(duì)于地參考平面(0V GND)的電平來確定邏輯“ L”和邏輯“ H”,例如TTL接口或CMOS接口,是單端信號(hào)。

隨著速率的提高,單端信號(hào)的上升/下級(jí)沿也變得陡峭,因此,輸出開關(guān)噪聲會(huì)導(dǎo)致信號(hào)產(chǎn)生過沖和下沖,并且當(dāng)多位信號(hào)同時(shí)轉(zhuǎn)換時(shí),還要考慮地彈(ground bounce)問題,同時(shí),單端信號(hào)以參考地平面作為信號(hào)回流路徑,這也為L(zhǎng)ayout帶來了挑戰(zhàn),由傳輸線阻抗不匹配引起的反射效應(yīng)會(huì)變得非常嚴(yán)重。

差分信號(hào)

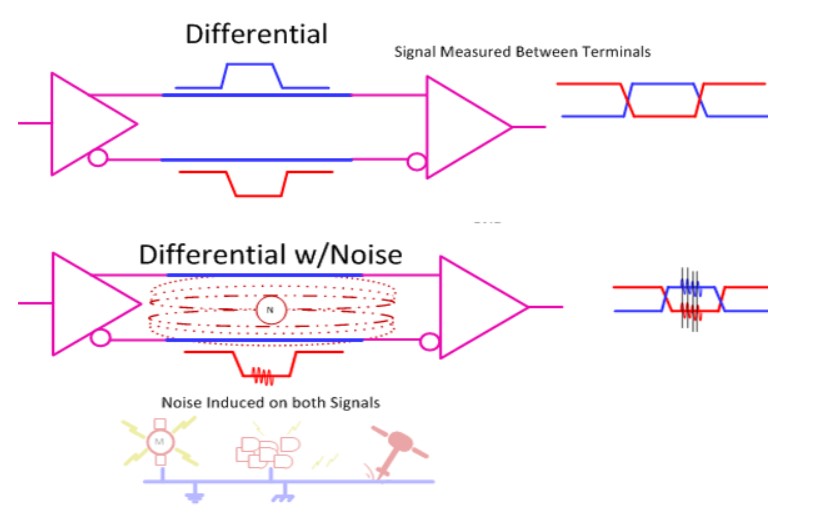

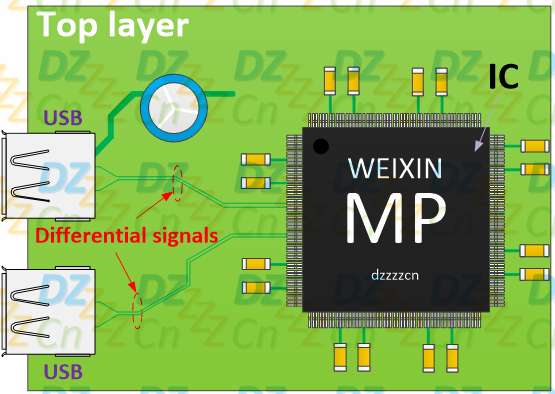

差分信號(hào)有別于單端信號(hào)一根信號(hào)線傳輸信號(hào)然后參考GND作為高(H)、低(L)邏輯電平的參考并作為鏡像流量路徑的做法,差分傳輸在兩根傳輸線上都傳輸信號(hào),這兩個(gè)信號(hào)的振幅相等,相位相差180度,極性相反,互為耦合。

差分信號(hào)的優(yōu)點(diǎn)

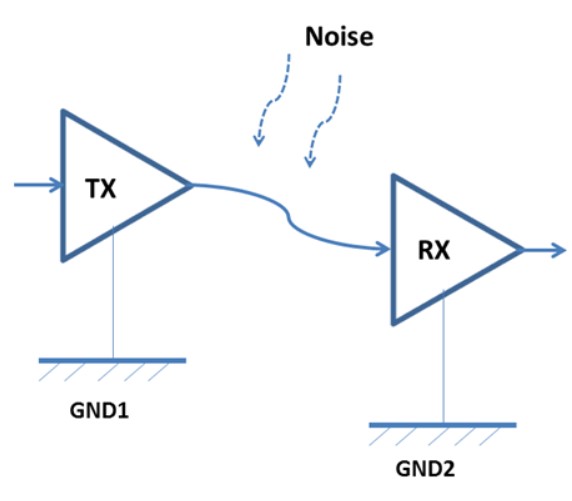

差分信號(hào)的第一個(gè)好處是,因?yàn)槟阍诳刂啤富鶞?zhǔn)」電壓,所以能夠很容易地識(shí)別小信號(hào)。在一個(gè)參考地做「0 V」基準(zhǔn)的單端信號(hào)傳輸系統(tǒng)里,測(cè)量信號(hào)的精確值依賴系統(tǒng)內(nèi)「0 V」的一致性。信號(hào)源和信號(hào)接收器距離越遠(yuǎn),他們局部地的電壓值之間有差異的可能性就越大。從差分信號(hào)恢復(fù)的信號(hào)值在很大程度上與「地」的精確值無關(guān),而在某一范圍內(nèi)便可。

差分信號(hào)的第二個(gè)主要好處是,它對(duì)外部電磁干擾(EMI)是高度免疫的。一個(gè)干擾源幾乎相同程度地影響差分信號(hào)對(duì)的每一端。既然電壓差異決定信號(hào)值,這樣將忽視在兩個(gè)導(dǎo)體上出現(xiàn)的任何同樣干擾。除了對(duì)干擾不大靈敏外,差分信號(hào)比單端信號(hào)生成的EMI還要少。

差分信號(hào)提供的第三個(gè)好處是,在一個(gè)單電源系統(tǒng),能夠從容精確地處理「雙極信號(hào)」。為了處理單端,單電源系統(tǒng)的雙極信號(hào),我們必須在地和電源干線之間某任意電壓處(通常是中點(diǎn))建立一個(gè)虛地。用高于虛地的電壓來表示正極信號(hào),低于虛地的電壓來表示負(fù)極信號(hào)。接下來,必須把虛地正確地分布到整個(gè)系統(tǒng)里。而對(duì)于差分信號(hào),不需要這樣一個(gè)虛地,這就使我們處理和傳播雙極信號(hào)有一個(gè)高真度,而無須依賴虛地的穩(wěn)定性。

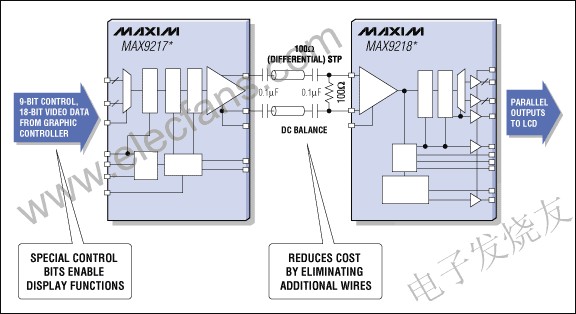

隨著集成電路的發(fā)展和對(duì)更高數(shù)據(jù)速率的要求,低壓供電成為急需。降低供電電壓不僅減少了高密度集成電路的功率消耗,而且減少了芯片內(nèi)部的散熱,有助于提高集成度。減少供電電壓和邏輯電壓擺幅的一個(gè)極好例子是低壓差分信號(hào)(LowVoltageDifferentialSignalingLVDS)。

低電壓差分信號(hào)(LVDS)是一種高速點(diǎn)到點(diǎn)應(yīng)用通信標(biāo)準(zhǔn)。多點(diǎn)LVDS (M-LVDS)則是一種面向多點(diǎn)應(yīng)用的類似標(biāo)準(zhǔn)。LVDS和M-LVDS均使用差分信號(hào),通過這種雙線式通信方法,接收器將根據(jù)兩個(gè)互補(bǔ)電信號(hào)之間的電壓差檢測(cè)數(shù)據(jù)。這樣能夠極大地改善噪聲抗擾度,并將噪聲輻射降至最低。

LVDS是一種用于替代發(fā)射極耦合邏輯(ECL)或正發(fā)射極耦合邏輯(PECL)的低功 耗邏輯 。LVDS的主要標(biāo)準(zhǔn)是TIA/EIA-644。有時(shí)也會(huì)對(duì)LVDS使用另一種標(biāo)準(zhǔn),即IEEE 1596.3—SCI(可擴(kuò)展一致性接口)。LVDS廣泛用于高速背板、電纜和板到板數(shù)據(jù)傳輸與時(shí)鐘分配,以及單個(gè)PCB內(nèi)的通信鏈路。

LVDS的優(yōu)勢(shì)包括

通信速度高達(dá)1 Gbps或以上

電磁輻射更低

抗擾度更高

低功耗工作

共模范圍允許高達(dá)±1的接地失調(diào)差額

M-LVDS

面向多點(diǎn)低電壓差分信號(hào)(M-LVDS)的標(biāo)準(zhǔn)TIA/EIA-899將LVDS延伸到用于解決多點(diǎn)應(yīng)用中的問題。相對(duì)于TIA/EIA-485 (RS-485)或控制器局域網(wǎng)(CAN),M-LVDS能夠以更低的功耗實(shí)現(xiàn)更高速度的通信鏈路。

M-LVDS相對(duì)于LVDS的額外特性包括

驅(qū)動(dòng)器輸出強(qiáng)度更高

躍遷時(shí)間可控

共模范圍更廣

面向總線空閑條件提供故障安全接收器選項(xiàng)

為什么使用LVDS或M-LVDS?

圖1中將LVDS和M-LVDS與其他多點(diǎn)和點(diǎn)到點(diǎn)協(xié)議進(jìn)行了比較。兩種標(biāo)準(zhǔn)都有低功耗要求。LVDS和M-LVDS的特征是在差分電壓擺幅較低的情況下實(shí)現(xiàn)差分信號(hào)。相對(duì)于LVDS,M-LVDS指定了更高的差分輸出電壓,以便允許來自多點(diǎn)總線的更高負(fù)載。

兩種協(xié)議都是面向高速通信設(shè)計(jì)的。典型應(yīng)用環(huán)境下會(huì)采用PCB走線或較短的有線/背板鏈路。LVDS的共模范圍就是針對(duì)這些應(yīng)用而設(shè)計(jì)。相對(duì)于LVDS,M-LVDS擴(kuò)展了其共模范圍,允許多點(diǎn)拓?fù)浣Y(jié)構(gòu)中具有額外噪聲。

LVDS/M-LVDS應(yīng)用考慮

總線類型和拓?fù)浣Y(jié)構(gòu)

時(shí)鐘分配應(yīng)用

LVDS/M-LVDS信號(hào)的特性

端接和PCB布局

抖動(dòng)和偏斜

數(shù)據(jù)編碼和同步

隔離

審核編輯:劉清

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

1923瀏覽量

64685 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65861 -

DRAM芯片

+關(guān)注

關(guān)注

1文章

84瀏覽量

18036 -

低壓差分信號(hào)

+關(guān)注

關(guān)注

0文章

11瀏覽量

9607

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LVDS低電壓差分信號(hào)

差分信號(hào)的優(yōu)勢(shì)和影響

差分信號(hào)的優(yōu)勢(shì)

什么是lvds信號(hào)

通過低電壓差分信號(hào)(LVDS)傳輸高速信號(hào)

通過低電壓差分信號(hào)(LVDS)傳輸高速信號(hào)

低電壓差分信號(hào)傳輸(LVDS)在汽車電子中的應(yīng)用

未使用端接的低電壓差分信號(hào)總線輸入方案

ADI推出多點(diǎn)低電壓差分信號(hào)收發(fā)器ADN469xE

LVDS低電壓差分信號(hào)的優(yōu)點(diǎn)及布板注意事項(xiàng)

一文詳解LVDS低電壓差分信號(hào)

LVDS振幅差分信號(hào)技術(shù)的優(yōu)勢(shì)和劣勢(shì)

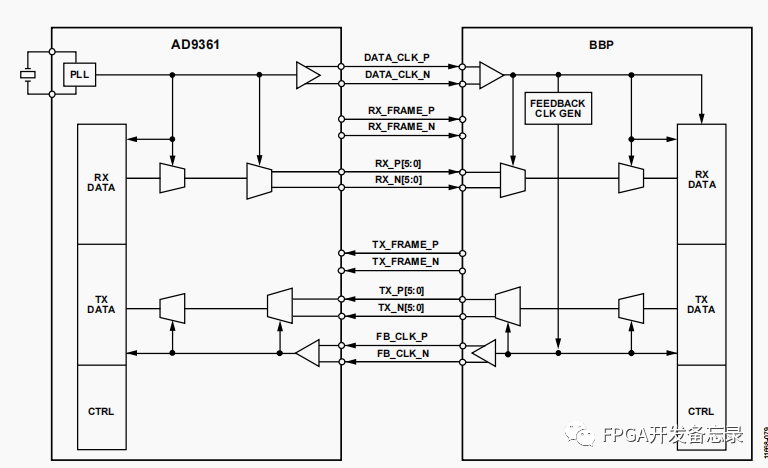

AD9361數(shù)據(jù)路徑在低電壓差分信號(hào)(LVDS)模式下運(yùn)行

低電壓差分信號(hào)(LVDS)接口浪涌靜電放電防護(hù)電路圖

低電壓差分信號(hào)(LVDS)是什么?有哪些優(yōu)勢(shì)

低電壓差分信號(hào)(LVDS)是什么?有哪些優(yōu)勢(shì)

評(píng)論