如需了解升級后需用戶干預的更改的相關信息,請參閱以下“升級至 CIPS 3.x”部分。

解決方案

升級至 CIPS 3.X

升級至 CIPS 3.x 及更高版本的過程是依據《Vivado Design Suite 用戶指南:采用 IP integrator 設計 IP 子系統》(UG994) 中的“第 11 章:為新版本更新設計”中記錄的典型 IP integrator 升級流程來執行的。

本節詳述了升級期間的必要注意事項。

確定設計流程

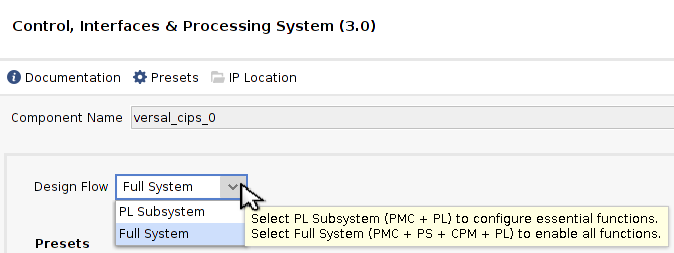

現已提供“設計流程 (Design Flow)”設置以簡化流程復雜性。

“PL 子系統 (PL Subsystem)”可隱藏所有設置(使用僅限 PL 設計時必要的設置除外),包括 CPM 模塊。

“完整系統 (Full System)”可使所有設置可見

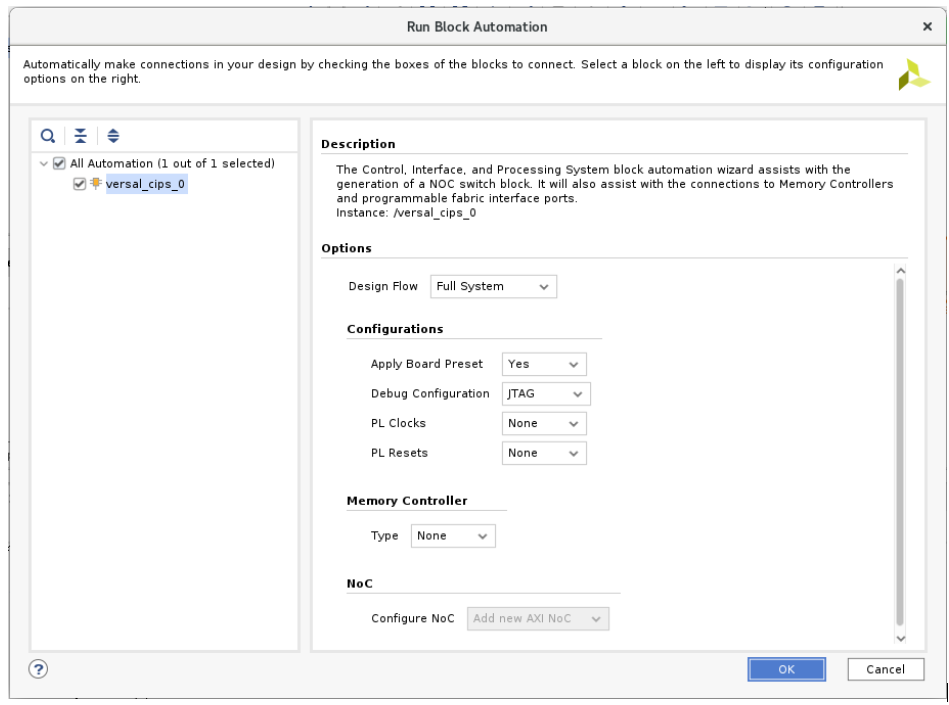

1. 打開 CIPS IP,并選擇相關的設計流程:

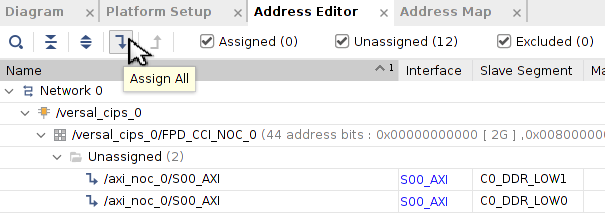

地址分配已清除

地址范圍已重新組織。原先版本中的“地址編輯器 (Address Editor)”中已選中的地址范圍分配現在將變為未分配狀態。

使用“Address Editor”中的“全部分配 (Assign All)”按鈕或者使用 assign_bd_address Tcl 命令即可自動選擇地址分配。定制地址范圍的已分配或未分配設置必須重新輸入。

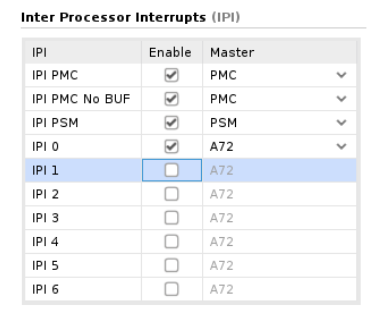

處理器間中斷 (Inter Processor Interrupt) 要求

要為 APU 上運行的 2021.1 及更高版本的軟件庫添加增強功能,需要啟用從 PMC 到 APU 的處理器間中斷 (Interprocessor Interrupt)。

否則可能發生以下啟動錯誤:

XPlmi_IpiDispatchHandler: Error: Unhandled IPI received

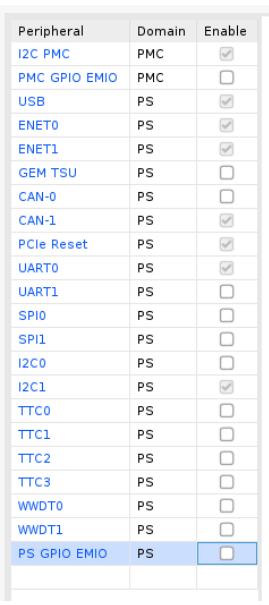

在“Design Flow”中:選中“Full System”,確認“PS PMC--》Interrupts--》 Inter Processor Interrupts (IPI) --》 IPI 0”是否已啟用且設為 A72

注:此條目在 CIPS 升級期間未設置。

注:此條目通常將由 VCK190/VMK180 評估板預置及其它賽靈思提供的示例進行設置。

基于腳本的設計移植流程

如果用戶使用 Tcl 腳本來維護模塊框圖,那么通常應通過 Vivado GUI 來為此版本完成移植。用戶維護腳本的流程如下:

1. 在原先使用該模塊框圖的 Vivado 版本中將其打開。通常方法是使用 source 命令從 Vivado 中找到 Tcl 腳本。

2. 在新版本的 Vivado 中打開此設計,并遵循上述基于工程的移植流程進行操作,例如重新分配地址范圍

3. 使用 write_bd_tcl 命令重新導出模塊框圖 Tcl

CIPS IP 參數格式變更:

針對每個主要的 CIPS 模塊(例如,PS/PLM 和 CPM),CIPS IP 設置已從個別參數組合為單一 TCL 列表。

2020.3 及更低版本:

CONFIG.PMC_QSPI_PERIPHERAL_ENABLE {1} \

CONFIG.PMC_SD0_PERIPHERAL_ENABLE {1} \

2021.1 及更高版本:

CONFIG.PS_PMC_CONFIG {PMC_QSPI_PERIPHERAL_ENABLE 1 PMC_SD0_PERIPHERAL {{ENABLE 1} }

新增功能特性/功能特性更新

模塊

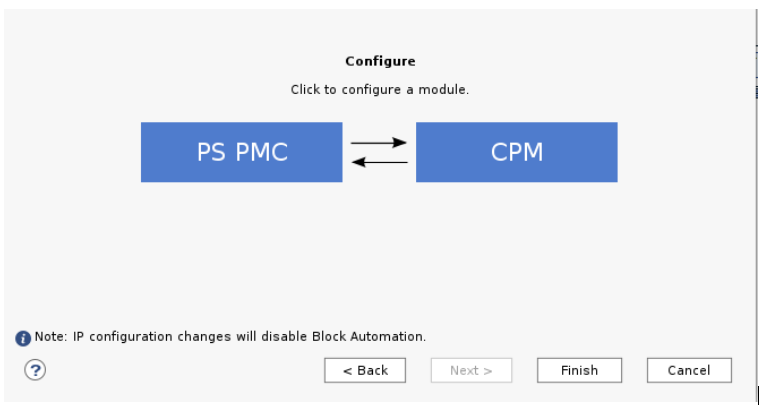

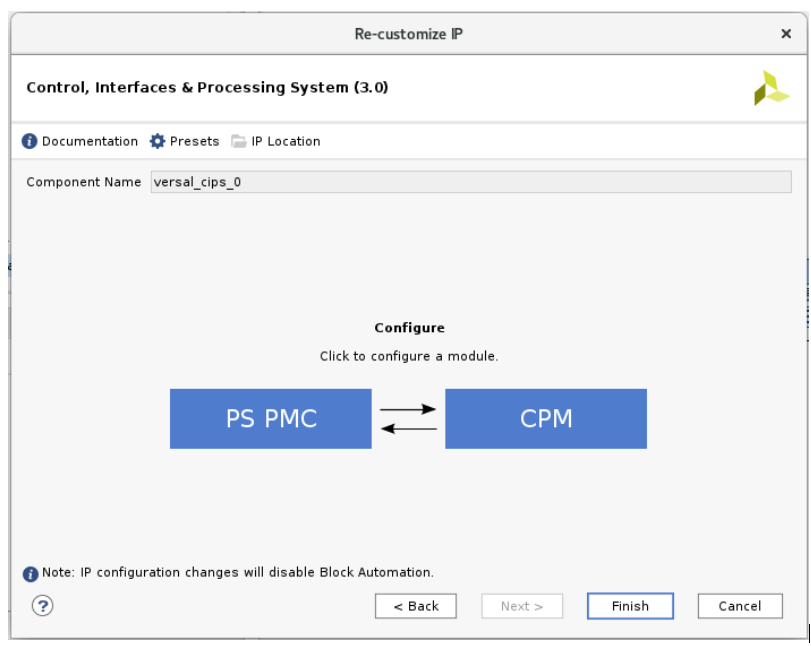

CPM 和 PS PMC 設置已拆分為獨立模塊。單擊“PS PMC”或“CPM”塊即可訪問各項設置。

塊自動化設置功能

在塊自動化設置中,現已支持 LPDDR4。

CPM 自動化設置已被暫時移除。

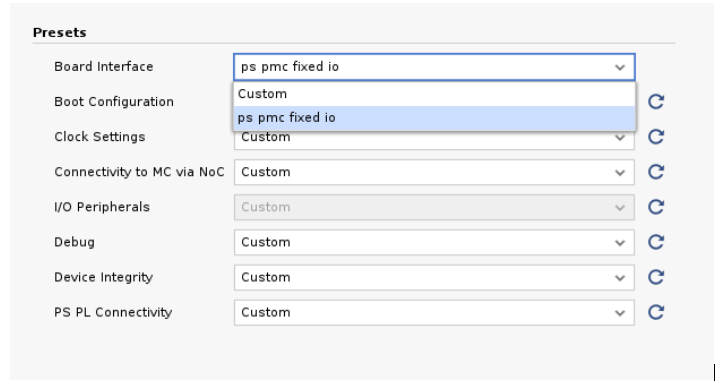

預置

“預置 (Presets)”字段允許選擇預配置的設置。

預置中的“開發板接口 (Board Interface)”設置可用于從選定的開發板文件導入 IP 設置并防止對其進行修改:

要修改評估板設置,請將預置的“Board Interface”設置還原為“Custom”。

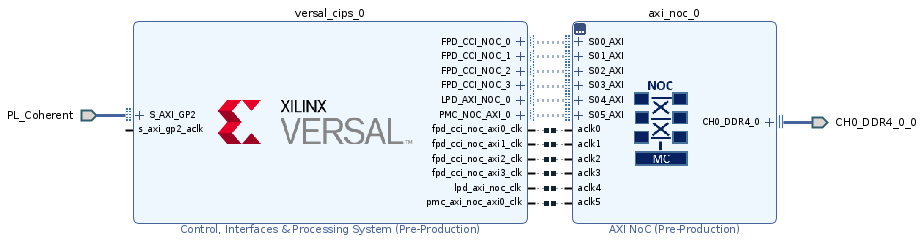

AXI 接口橋接

接口橋接現已支持 AXI 地址路徑通過 CIPS 塊進行傳輸。默認禁用接口路徑通過 CIPS 進行傳輸。對于互連拓撲結構(例如,從 AXI 從接口通過 CIPS CCI-500 到 DRAM 的 PL 高速緩存一致性),則需要使用接口橋接,如以下 AXI 接口拓撲結構中所示:

IP 默認設置

有多項參數默認設置已發生更改。

系統監控器電壓篡改響應

“系統監控器電壓篡改響應 (Sysmon Voltage Tamper Response)”已被暫時移除,計劃將在 Vivado 2021.2 中重新啟用。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19349瀏覽量

230278 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131340

發布評論請先 登錄

相關推薦

中科曙光南京研究院方案入選江蘇省信息技術創新優秀解決方案

中科曙光入選2024年江蘇省信息技術應用創新優秀解決方案名單

玩轉Nginx日志管理:高效排查問題的終極指南

日志篇:模組日志總體介紹

穩定性建設之變更管理

梯度科技入選2023年信息技術應用創新解決方案名單

兆芯金融方案入選工信部2023年信息技術應用創新典型解決方案

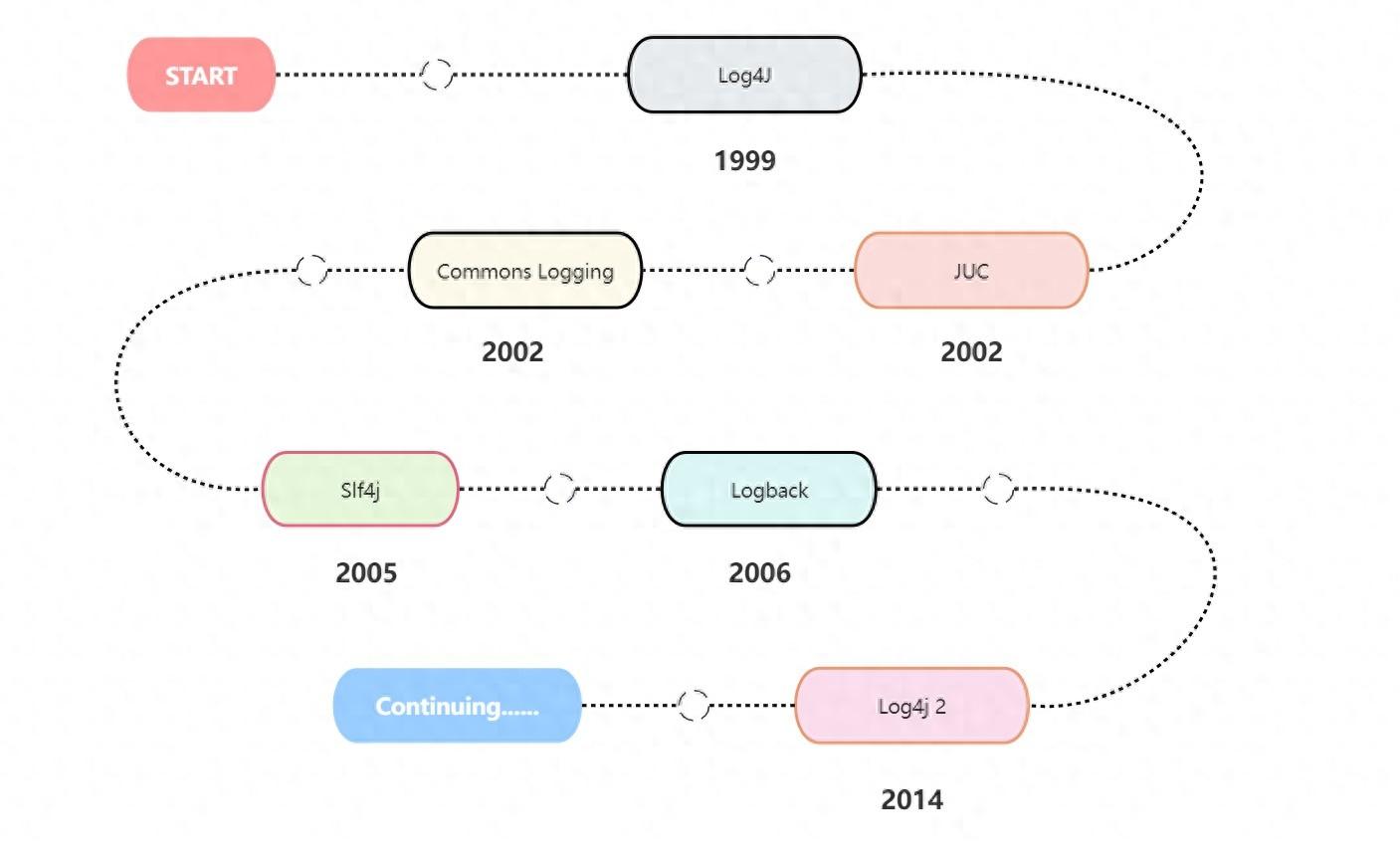

日志框架簡介-Slf4j+Logback入門實踐

奇怪!應用的日志呢??

翼輝信息入選2023年信息技術應用創新解決方案名單

【嵌入式SD NAND】基于FATFS/Littlefs文件系統的日志框架實現

CIPS 3.0變更日志和移植信息解決方案

CIPS 3.0變更日志和移植信息解決方案

評論