雖然滿足所有功能規(guī)范的工作設(shè)備是芯片設(shè)計項目組的首要目標(biāo),但許多設(shè)計人員醒來時滿頭大汗,擔(dān)心芯片到貨時會死機(jī)。無論使用多少覆蓋率或使用多少驗證工具,一個或多個錯誤都可能漏網(wǎng)。

這種高壓、苛刻的工程環(huán)境需要三個獨立的基于技術(shù)的功能級驗證工具,以保證芯片功能無缺陷且高度可靠。驗證和測試覆蓋率的重疊似乎過多。許多睡眠不足的設(shè)計師認(rèn)為額外的努力是值得的。

三個功能級驗證步驟——功能驗證、功能測試和內(nèi)置自測 (BIST)——每一個都提供了對芯片設(shè)計的信心。將它們結(jié)合起來可以使芯片按照預(yù)期的功能規(guī)格工作的信心增加三倍。

功能驗證是最耗費資源的步驟,因為它使用了大量可用的 EDA 工具和大量預(yù)算用于驗證的時間。功能驗證必須包括功能覆蓋和代碼覆蓋。兩者處理驗證問題的方式不同,對于確保全面驗證是必要的。

功能覆蓋回答了這個問題:設(shè)計的功能行為是否符合芯片應(yīng)該做的規(guī)范?有必要根據(jù)規(guī)范測試設(shè)備的行為。還不夠,因為預(yù)期的功能行為幾乎不能說明遇到意外狀態(tài)或輸入時會發(fā)生什么。

這是代碼覆蓋關(guān)注設(shè)計結(jié)構(gòu)(代碼)而不是設(shè)計規(guī)范的地方,并且可以發(fā)現(xiàn)功能規(guī)范中未考慮的行為。例如,可能存在在正常操作中從未預(yù)期存在的狀態(tài)或輸入。如果確實發(fā)生了這種意想不到的狀態(tài)或輸入,會發(fā)生什么?芯片如何響應(yīng)?芯片可能會表現(xiàn)出從未預(yù)料到的行為。

通過相互補(bǔ)充,功能覆蓋率和代碼覆蓋率量化了功能驗證,并有助于將設(shè)計帶到下一個綜合、流片和最終硅片的連續(xù)步驟。實現(xiàn)功能和代碼覆蓋閉合的功能驗證會清除設(shè)計的大部分或所有功能錯誤。當(dāng)然,最終目標(biāo)不是設(shè)計,而是基于設(shè)計制造的芯片。

芯片制造完成后,功能測試和 BIST 用于清除由于制造缺陷或制造過程中其他問題引起的任何錯誤。根據(jù)每個測試設(shè)計實施的內(nèi)容,BIST 計劃確定測試與執(zhí)行功能測試的任何重疊,以確保所有制造的晶體管和導(dǎo)線無缺陷。包括 BIST 在內(nèi)的深思熟慮的測試策略可以減少測試儀的時間,降低制造測試的時間和成本,并測試使用外部測試方法難以設(shè)置的芯片關(guān)鍵內(nèi)部區(qū)域。BIST 的第二個主要優(yōu)點是它可以在設(shè)備的生命周期內(nèi)隨時部署使用,這是某些應(yīng)用程序的必要策略。

使用嵌入式 FPGA 可以簡化功能設(shè)備測試,因為 FPGA 是一個預(yù)先驗證的組件,可以保證按照編程的方式運行,從而最大限度地減少測試。雖然 FPGA 中的 BIST 實施會帶來面積和性能開銷,但使用它具有很大的好處,包括更好的測試以及一旦將設(shè)備安裝到系統(tǒng)中就可以對其進(jìn)行測試。

需要一種將功能設(shè)計驗證與綜合功能測試策略相結(jié)合的包容性驗證策略,以降低設(shè)備到達(dá)時死機(jī)的可能性。

-

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1023瀏覽量

54937 -

eda

+關(guān)注

關(guān)注

71文章

2769瀏覽量

173444 -

代碼

+關(guān)注

關(guān)注

30文章

4803瀏覽量

68756

發(fā)布評論請先 登錄

相關(guān)推薦

芯片設(shè)計復(fù)雜度劇增,紫光芯片云 3.0 助力企業(yè)搭建專業(yè)設(shè)計環(huán)境

英諾達(dá)發(fā)布全新靜態(tài)驗證產(chǎn)品,提升芯片設(shè)計效率

手持 / 便攜多普勒流速流量計:無懼復(fù)雜環(huán)境的強(qiáng)大測流工具

復(fù)雜環(huán)境下多無人智能車輛協(xié)同調(diào)控

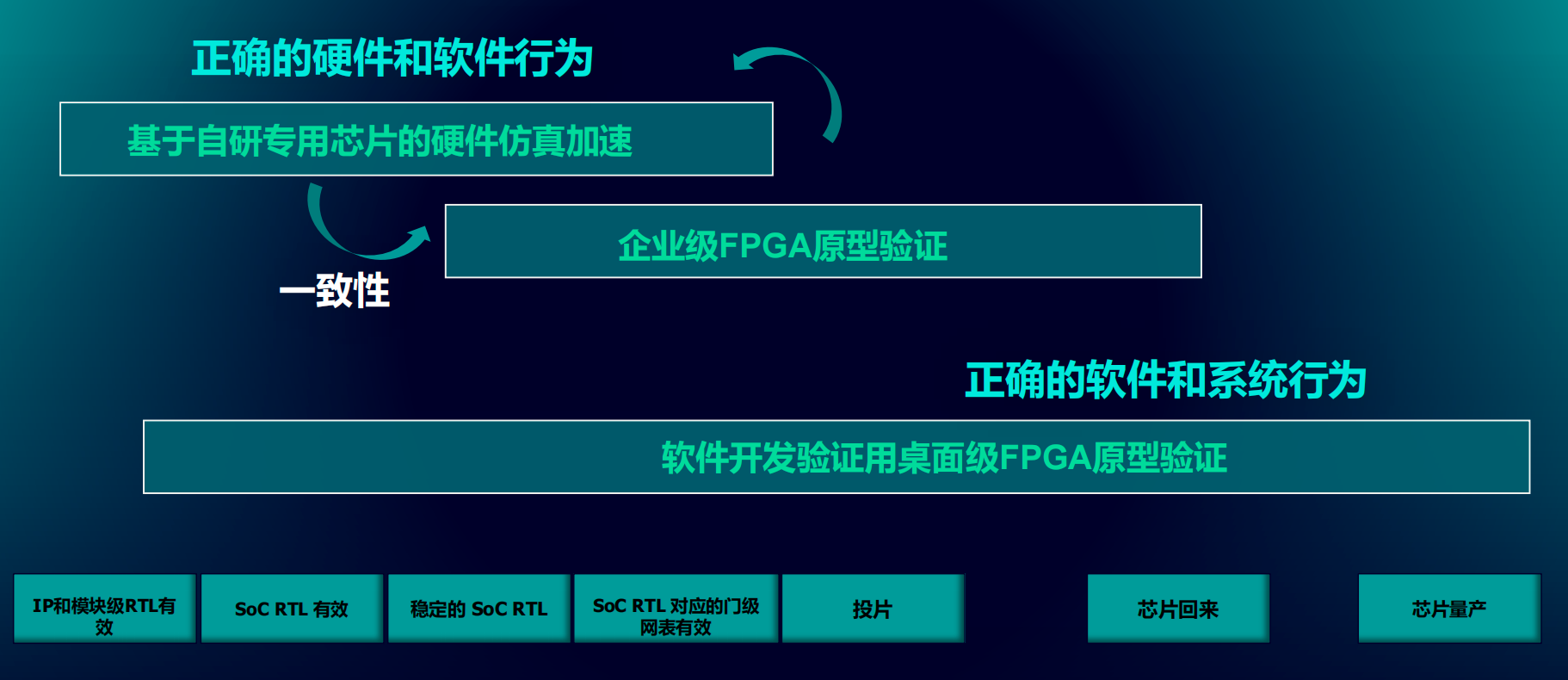

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗證之路

芯啟源助力復(fù)雜數(shù)字芯片設(shè)計與驗證

芯片設(shè)計流片、驗證、成本的那些事

復(fù)雜電磁環(huán)境模擬系統(tǒng)設(shè)計方案

芯片測試和芯片驗證的區(qū)別

工業(yè)級路由器:讓你輕松應(yīng)對復(fù)雜網(wǎng)絡(luò)環(huán)境!

基于自研芯片+頂級AMD FPGA,西門子EDA發(fā)布“快而全”的Veloce CS

復(fù)雜的芯片設(shè)計驗證環(huán)境

復(fù)雜的芯片設(shè)計驗證環(huán)境

評論