隨著半導(dǎo)體設(shè)計(jì)團(tuán)隊(duì)競(jìng)相利用“超越摩爾”,新的架構(gòu)選擇和挑戰(zhàn)層出不窮。以超大規(guī)模硬件為例,其中一系列工作負(fù)載——數(shù)據(jù)庫(kù)分析、人工智能、微服務(wù)、視頻編碼和高復(fù)雜性計(jì)算算法——需要一系列處理器解決方案。性能、功耗和成本仍然至關(guān)重要,但現(xiàn)在架構(gòu)師自己交付。沒(méi)有一種“最好”的架構(gòu);處理器必須設(shè)計(jì)為最好地服務(wù)于特定類別的工作負(fù)載和價(jià)格/性能配置文件。

多核架構(gòu)挑戰(zhàn)

AWS Graviton2 有 64 個(gè) Arm Neoverse N1 內(nèi)核,它們平鋪在單個(gè)芯片上的連貫網(wǎng)狀網(wǎng)絡(luò)中。其他設(shè)計(jì)已經(jīng)擴(kuò)展到多芯片,芯片之間具有緩存一致的連接。多芯片實(shí)現(xiàn)為進(jìn)一步增長(zhǎng)和降低不太先進(jìn)工藝成本的潛力開(kāi)辟了空間。雖然這些新架構(gòu)選項(xiàng)擴(kuò)展了可能性,但它們也帶來(lái)了新的設(shè)計(jì)挑戰(zhàn)。在眾多選擇中,哪些架構(gòu)真正能夠以合適的價(jià)格為合適的工作負(fù)載提供更高的吞吐量?

這里的一個(gè)問(wèn)題是,應(yīng)如何針對(duì)目標(biāo)類應(yīng)用程序的物理內(nèi)存對(duì)相干網(wǎng)狀網(wǎng)絡(luò)中的分布式系統(tǒng)緩存進(jìn)行分區(qū)。優(yōu)化這些選擇,甚至優(yōu)化哪些 CPU 內(nèi)核最能滿足需求,都需要以周期級(jí)精度運(yùn)行實(shí)際工作負(fù)載。高級(jí)模型根本不足以達(dá)到此目的。

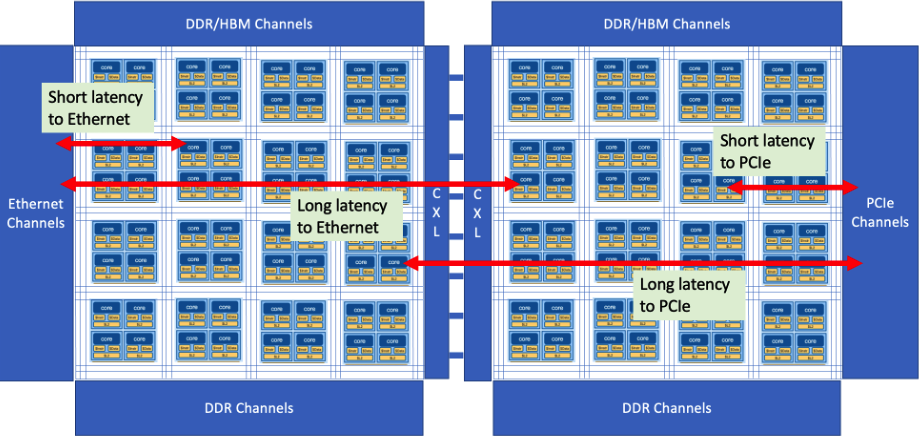

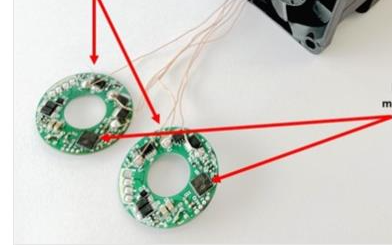

圖:多芯片實(shí)現(xiàn)中不同的 I/O 延遲。(來(lái)源:Cadence)

連貫網(wǎng)格中的處理器陣列之間的通信延遲在單個(gè)裸片內(nèi)將相對(duì)一致,但在多裸片實(shí)現(xiàn)中裸片之間的延遲可能會(huì)有很大差異(見(jiàn)圖)。因此,設(shè)計(jì)發(fā)展出多種架構(gòu),可在未來(lái)使用——全連接網(wǎng)格、集線器和輻條內(nèi)存系統(tǒng)或其他 2D 和 3D 結(jié)構(gòu),其中一個(gè)小芯片提供大系統(tǒng)緩存和主內(nèi)存訪問(wèn)。此外,堆棧中的其他小芯片相互通信,并通過(guò)集線器與主存儲(chǔ)器通信。

有效探索所有這些選項(xiàng)在很大程度上取決于針對(duì)實(shí)際工作負(fù)載準(zhǔn)確建模性能。建模和分析只能在 RTL 域中使用仿真和原型進(jìn)行探索。

SystemReady 合規(guī)性

服務(wù)器架構(gòu)師面臨的另一種問(wèn)題是操作系統(tǒng)兼容性。您可以直接在大多數(shù)筆記本電腦上啟動(dòng)任何 Linux 發(fā)行版、虛擬機(jī)管理程序或 Windows。要在基于 Arm 的服務(wù)器上啟動(dòng),此責(zé)任由服務(wù)器制造商和 Arm 分擔(dān)。

Arm 開(kāi)發(fā)了一個(gè)名為 SystemReady 的合規(guī)套件,以標(biāo)準(zhǔn)化一組最低要求,以解決這個(gè)問(wèn)題和其他合規(guī)問(wèn)題。PCIe 合規(guī)性是一個(gè)特別重要的組件,因?yàn)樗苯訛樵S多服務(wù)器接口協(xié)議提供或作為主要 I/O 的基礎(chǔ),以實(shí)現(xiàn)快速存儲(chǔ)、快速網(wǎng)絡(luò)和芯片外連貫接口。這里特別重要的是通過(guò) PCIe 進(jìn)行遠(yuǎn)程服務(wù)器引導(dǎo)。Arm 將此合規(guī)套件作為在 UEFI (BIOS) 層上運(yùn)行的軟件提供。Cadence 與 Arm 合作了幾年,旨在將測(cè)試縮減為具有 PCIe 流量生成庫(kù)的最小裸機(jī)測(cè)試套件,該庫(kù)的仿真速度比 UEFI 測(cè)試套件更快,可以快速調(diào)整硬件調(diào)試。

服務(wù)器開(kāi)發(fā)人員面臨的另一個(gè)挑戰(zhàn)是 PCIe 使用強(qiáng)排序的內(nèi)存模型。Arm 支持標(biāo)準(zhǔn)允許的松散排序的內(nèi)存模型。但只有強(qiáng)排序才能保證沒(méi)有死鎖。在松散訂購(gòu)下,硬件/固件開(kāi)發(fā)人員必須提供該保證。不幸的是,這無(wú)法通過(guò)合規(guī)性檢查。集成商必須再次在仿真器或原型系統(tǒng)上通過(guò)廣泛的用例測(cè)試證明設(shè)計(jì)是死鎖安全的。

使用 Cadence System 驗(yàn)證 IP 的方法使工程師能夠在半天內(nèi)啟動(dòng)并運(yùn)行系統(tǒng)級(jí)測(cè)試套件,該套件可以根據(jù) SystemReady 要求驗(yàn)證 PCIe 集成。此方法還可用于演示從連接到 PCIe 的閃存設(shè)備模型引導(dǎo) SUSE Linux 和 Windows,這引起了高級(jí)服務(wù)器社區(qū)的極大興趣。

不僅適用于服務(wù)器

Arm Neoverse 平臺(tái)不僅是為高端服務(wù)器設(shè)計(jì)的。該家族已經(jīng)開(kāi)始進(jìn)入其他云應(yīng)用程序和通信基礎(chǔ)設(shè)施,一直到邊緣。在其中一些應(yīng)用程序中,多核架構(gòu)已經(jīng)很重要。在大多數(shù)此類應(yīng)用程序(例如汽車)中,對(duì)一系列開(kāi)放和商業(yè)操作系統(tǒng)的開(kāi)箱即用支持是必不可少的。

我相信用于自動(dòng)生成系統(tǒng)級(jí)內(nèi)容和驗(yàn)證系統(tǒng)級(jí)目標(biāo)合規(guī)性的工具將在許多市場(chǎng)中具有廣泛的適用性。EDA 行業(yè)需要超越傳統(tǒng)的單接口單協(xié)議驗(yàn)證 IP (VIP) 范圍,走向多接口多協(xié)議系統(tǒng)級(jí) VIP 的新時(shí)代。

-

處理器

+關(guān)注

關(guān)注

68文章

19349瀏覽量

230325 -

ARM

+關(guān)注

關(guān)注

134文章

9111瀏覽量

368072 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9239瀏覽量

85679 -

HPC

+關(guān)注

關(guān)注

0文章

318瀏覽量

23813

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

QorIQ?T1042多核處理器

云計(jì)算HPC軟件關(guān)鍵技術(shù)

旋智多核心處理器助力電機(jī)控制應(yīng)用

對(duì)稱多處理器和非對(duì)稱多處理器的區(qū)別

多核RISC-V處理器供應(yīng)商超睿科技全力支持RT-Thread Smart,共同賦能“大芯片”生態(tài)

簡(jiǎn)述微處理器的指令集架構(gòu)

ARM處理器和CISC處理器的區(qū)別

微處理器的指令集架構(gòu)介紹

TMS320C6474多核數(shù)字信號(hào)處理器數(shù)據(jù)表

嵌入式微處理器的分類 嵌入式微處理器的種類和型號(hào)

嵌入式微處理器架構(gòu)可分為

嵌入式微處理器的基礎(chǔ)是什么

多核架構(gòu)高性能電機(jī)控制芯片

用于多核處理器的可配置多軌PMU TPS650860數(shù)據(jù)表

HPC處理器的多核架構(gòu)挑戰(zhàn)

HPC處理器的多核架構(gòu)挑戰(zhàn)

評(píng)論