FPGA各位和數(shù)字IC設(shè)計(jì)崗位面試時(shí)常常會(huì)問(wèn)下verilog的一些基本概念,做了下整理,面試時(shí)一定用得上!

1,reg與wire的區(qū)別:

相同點(diǎn):

都能表示一種類型類型。

不同點(diǎn):

wire

連線型數(shù)據(jù),線網(wǎng)類型;

表示元件間的物理連線,不能保存數(shù)據(jù);

線網(wǎng)是被驅(qū)動(dòng)的,可以用連續(xù)賦值語(yǔ)句或把元件的輸出連接到線網(wǎng)等方式進(jìn)行驅(qū)動(dòng);

給線網(wǎng)提供驅(qū)動(dòng)的賦值元件就是“驅(qū)動(dòng)源”,線網(wǎng)的值由驅(qū)動(dòng)源來(lái)決定;

如果線網(wǎng)沒(méi)有連接到驅(qū)動(dòng)源,線網(wǎng)的缺省值為“Z”。

reg:

寄存器型數(shù)據(jù)類型,通常用于對(duì)存儲(chǔ)單元進(jìn)行描述;

這種變量可以保持它們自身的數(shù)值,直到該變量被指定了新的值為止 ;在過(guò)程被賦值的變量必須定義為reg型;

只能存放無(wú)符號(hào)數(shù);

有符號(hào)數(shù)寄存器變量:integer 。

2,$stop:

表示停止命令,常用格式為,位于initial語(yǔ)句中:

#時(shí)間(N) $stop;

表示在(N)個(gè)時(shí)間單位后,停止仿真。

在程序中需要多次使用同一個(gè)數(shù)字時(shí),可以考慮采用參數(shù)來(lái)提高代碼的簡(jiǎn)潔度,降低代碼的設(shè)計(jì)量。

參數(shù)一經(jīng)聲明,就視其為一個(gè)常量,在整個(gè)過(guò)程中值不在改變。

其定義方式如下:

《變量名》=《變量定義》;

例如:

parameter SET_TIME_1S=27‘b50_000_000;

//把常量50000000用標(biāo)識(shí)符SET_TIME_1S來(lái)代替。

用同一個(gè) parameter 同時(shí)定義多個(gè)參數(shù)時(shí),各個(gè)參數(shù)之間用“ , ”來(lái)隔開(kāi)。

使用參數(shù)可以提高代碼的可讀性,也便于修改。

4,仿真時(shí)的端口定義

與模塊輸入端口相連的信號(hào)端口是產(chǎn)生仿真信號(hào)的端口,需定義為reg類型;

與模塊輸出端口相連的信號(hào)端口是被輸出信號(hào)所驅(qū)動(dòng)的端口,需要定義為wire類型;

5,阻塞與非阻塞賦值語(yǔ)句

(1),非阻塞賦值語(yǔ)句

用操作符“《=”來(lái)標(biāo)識(shí)“非阻塞賦值語(yǔ)句”;

在begin-end串行語(yǔ)句中,一條非阻塞賦值語(yǔ)句的執(zhí)行不會(huì)阻塞下一條語(yǔ)句額執(zhí)行,也就是說(shuō),在本條非阻塞型過(guò)程賦值語(yǔ)句對(duì)應(yīng)的賦值操作執(zhí)行完之前,下一條語(yǔ)句也可以開(kāi)始執(zhí)行。

仿真過(guò)程在遇到非阻塞型過(guò)程賦值語(yǔ)句后,首先計(jì)算其右端賦值表達(dá)式的值,然后等到仿真時(shí)間結(jié)束時(shí)將該計(jì)算結(jié)果賦值變量。也就是說(shuō),這種情況下的賦值操作是在同一時(shí)刻上的其他普通操作結(jié)束后才得以執(zhí)行。

(2),阻塞賦值語(yǔ)句

用操作符“=”來(lái)標(biāo)識(shí)“阻塞賦值語(yǔ)句”;

在begin-end串行語(yǔ)句中的各條阻塞型過(guò)程賦值語(yǔ)句將它們?cè)陧樞蚩熘械呐帕写涡蛞来蔚靡詧?zhí)行。

阻塞型賦值過(guò)程賦值語(yǔ)句的執(zhí)行過(guò)程:首先計(jì)算右端賦值表達(dá)式的值,然后立即將計(jì)算結(jié)果賦值給“=”左端的被賦值變量。

原文標(biāo)題:verilog的一些技巧,就靠他拿offer了!

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603598 -

寄存器

+關(guān)注

關(guān)注

31文章

5343瀏覽量

120424 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7048瀏覽量

89070 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110122

原文標(biāo)題:verilog的一些技巧,就靠他拿offer了!

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

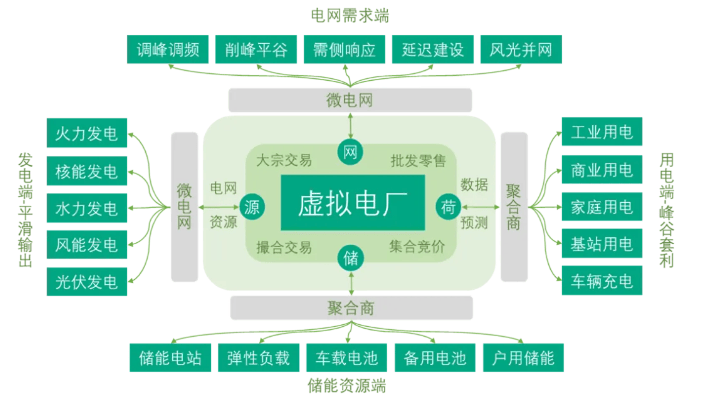

了解虛擬電廠的基本概念

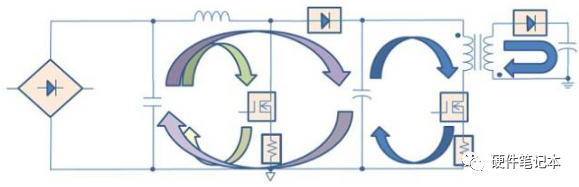

分享一些常見(jiàn)的電路

Linux應(yīng)用編程的基本概念

X電容和Y電容的基本概念

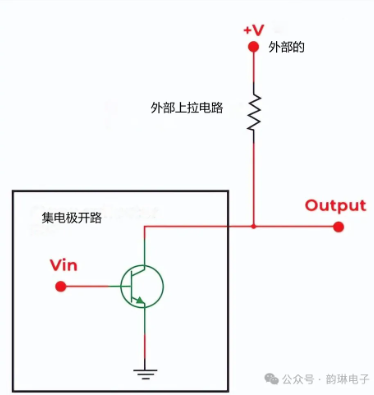

集電極開(kāi)路的基本概念與原理

DDR4的基本概念和特性

伺服系統(tǒng)基本概念和與變頻的關(guān)系

socket的基本概念和原理

BP網(wǎng)絡(luò)的基本概念和訓(xùn)練原理

卷積神經(jīng)網(wǎng)絡(luò)的基本概念、原理及特點(diǎn)

循環(huán)神經(jīng)網(wǎng)絡(luò)的基本概念

組合邏輯控制器的基本概念、實(shí)現(xiàn)原理及設(shè)計(jì)方法

關(guān)于Verilog的一些基本語(yǔ)法

電源路徑的基本概念

verilog的一些基本概念

verilog的一些基本概念

評(píng)論