KIA MOS管

使用C-V曲線查Case

隨著半導體制程越來越復雜,我們最關鍵的參數Vt的控制越來越重要,有的時候我們的Vt如果單純是襯底濃度影響我們自然可以通過長溝和短溝以及NMOS和PMOS是否同時變動來確定是否是GOX還是Vt_IMP的問題,其實這也是一種correlation它其實是一種邏輯思考方式,只是他是基于理論的。

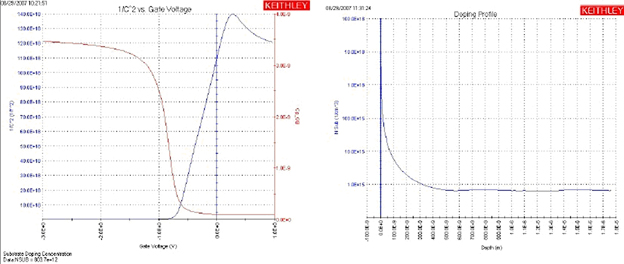

本文來討論下MOS的C-V曲線與襯底濃度以及GOX特性的關系,這樣大家既可以用它來評估GOX特性,也可以用C-V曲線來判定Vt 的Case是由于什么造成的,其實同時也是為了介紹這個MOS晶體管的柵極結構的C-V特性,既有助于我們理解這個理論,又可以用實際案例來驗證。

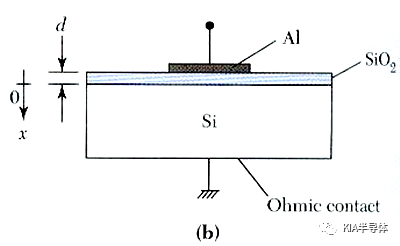

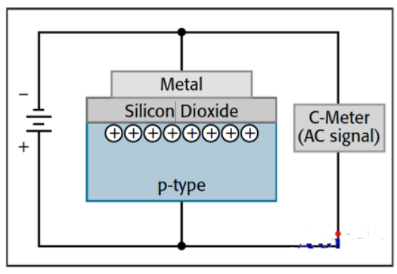

講到MOS電容,他的結構就是Gate-Oxide-Semiconductor的夾心電容結構,其實就是高中物理講的平板電容結構。而我們實際的平板電容的C-V特性下的電容式恒定值,因為電容公式高速我們電容只和介電常數以及厚度和面積相關,所以和電壓無關。不過MOS結構的電容會隨著電壓的變化而變化。

MOS-Cap的電容結構很簡單,忽略源漏極就只剩下Gate-Oxide-Semiconductor(Well)了。所以叫MOS,也叫MIS(Metal-Insulator-Semiconductor)。

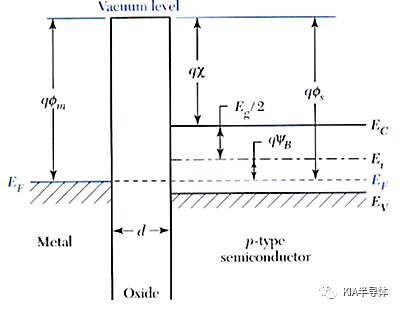

介紹這樣的MOS-C的結構之前,先介紹一個概念平帶電壓(Vfb, Flat-Band Voltage)。當柵極無偏壓時候,理想情況下金屬功函數qΦm與半導體功函數qΦs的能量差應該為零,也就是金屬和半導體的功函數差qΦms等于零。也就是說零偏壓下,能帶是平的所以叫做平帶。而在柵極接正電壓或負電壓,則半導體一邊的能帶會受到下拉或上移影響而彎曲。

下面我們以PWELL (NMOS-C)為例,先討論這樣的MIS結構下的三種特性:

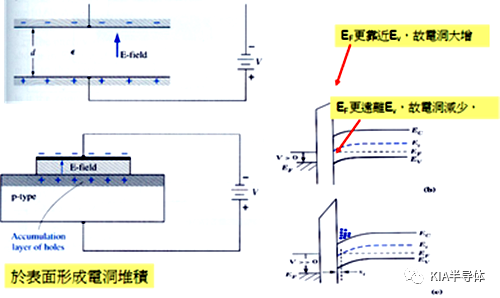

1)當柵極偏壓(Vg)小于0V時候,此時溝道由于電場感應出多子空穴堆積在表面,故稱之為積累區(Accumulation)。

2)當Vg>0時,此時溝道開始感生出電子,先消耗掉原來Pwell的空穴,所以稱之為耗盡區(Depletion)。

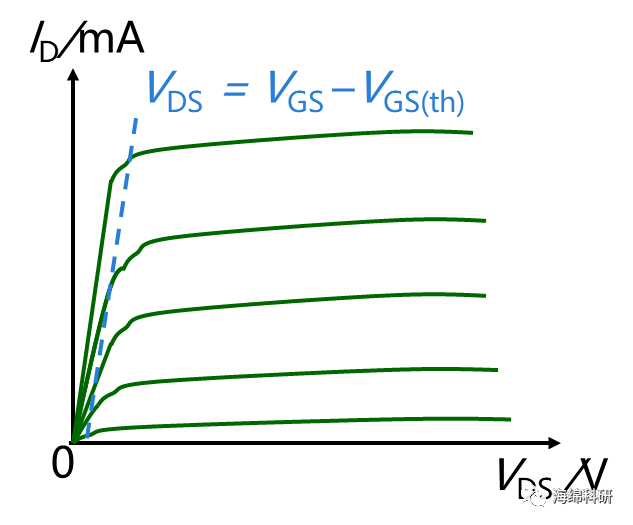

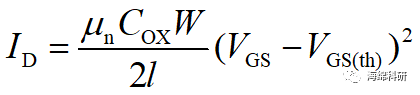

3)當Vg進一步增大, Vg>>0V時,溝道已經產生過量的電子反型出N型。此時為反型區(Inversion),而溝道深度就是我們的反型區寬度。

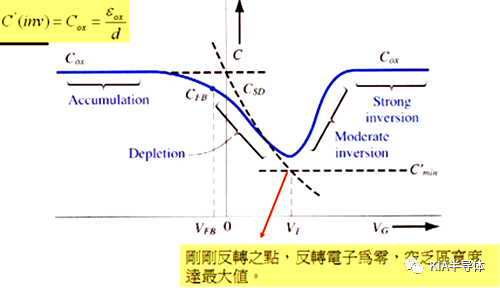

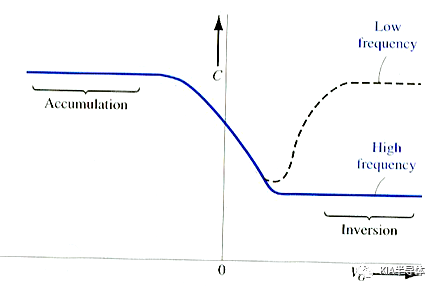

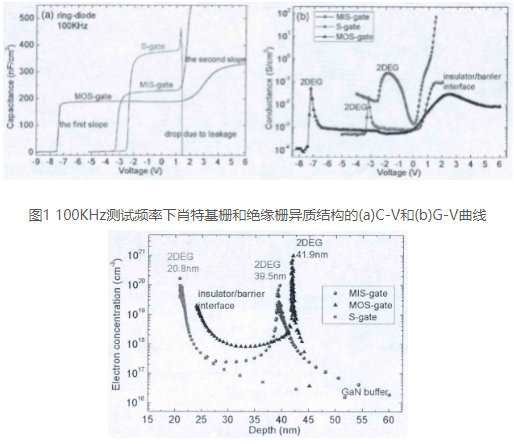

所以根據上面的介紹,我們介紹各自的電容特性,并且畫出Poly-Oxide-PWELL (NMOS-C)的電容-電壓(C-V)特性曲線如下圖:

1)在積累區,由于襯底是PWELL,而積累的也是P-type,所以下電極只是導電特性變好,所以所有的柵極電壓全部加在GOX上,所以此時電容最大。

2)在耗盡區,隨著柵極電壓從積累區逐漸開始增大,溝道逐漸開始產生耗盡區,所以此時電壓是加在GOX和耗盡區連個串聯的電容上面,所以電容逐漸開始減小。

3)在反型區,也就是Vg大于開啟電壓時,此時耗盡區寬度達到最大值,所以進入強反型,這個時候的電容達到最小值。

當然還有個不容忽略的問題是我們的測試電壓的頻率,當頻率較低時,載流子的速度可以跟的上電壓頻率的變化,所以此時的反型區是被充電的最終還是達到GOX的厚度。

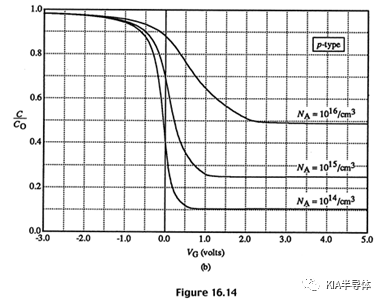

而如果是高頻,載流子速度根本趕不上反型區充電速度,所以只能保持在低電容狀態。而實際上這個反型區寬度與襯底濃度是有很大關系的(這個可能用Vt與襯底濃度的關系來理解,所以完全可以通過反型區高頻電容特性來判斷襯底濃度的變化~)

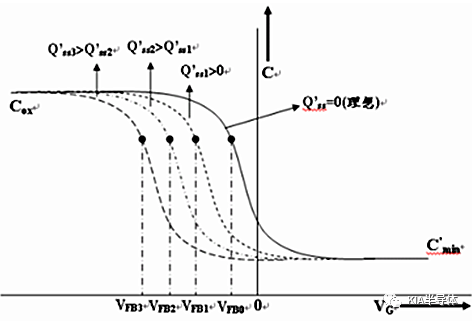

當然,上面講的都是理論情況,也就是平帶為零的情況。而實際上平帶不可能為零,因為我們的金屬與半導體功函數是有差的,而且氧化層本身也會有電荷。

所以實際下半導體的能帶是默認已經彎曲的,所以我們一直有個平帶電壓測試就是使得金屬與半導體的能帶由彎曲還原到平帶狀態下的電壓就叫做平帶電壓(Vfb),也是我們評估柵極氧化層的重要指標。

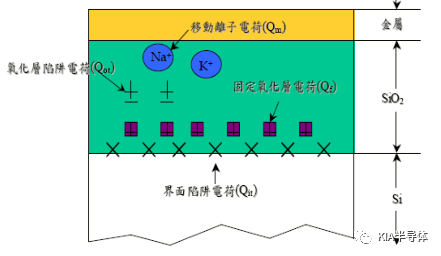

通常柵氧中,氧化層缺陷是影響它電性的主要因素,而這些缺陷主要來自以下四種:

1) 界面陷阱電荷(Qit: Interface Trapped Charge),它主要位于Si與SiO的界面處,主要由于氧化過程中未找到氧鍵的Si的懸掛鍵,它可以俘獲電子或空洞,所以可以帶正電或負電。

可以通過適當的回火(Anneal)或者Alloy來降低硅懸掛鍵的濃度,或者選用<100>晶向的硅片(知道為啥CMOS用<100>的了吧)。

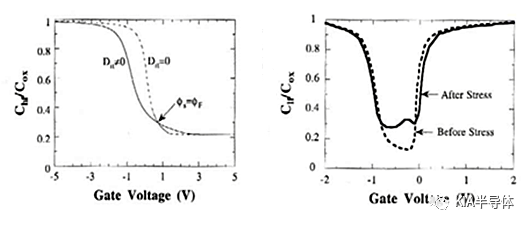

在C-V特性曲線上,高頻電容與施加電壓有關,Qit對高頻信號不做回應所以不會改變,它只會對多余電荷的補充和消耗做出響應(dVg/dt),所以在耗盡區扭曲。

2) 氧化層固定電荷(Fixed Oxide Charge, Qf)。主要分布在距離Si/SiO2界面約2nm內,主要由于氧化過程或結束后回火條件不合理導致部分硅沒有完全氧化產生硅正離子,由于這樣的正離子電荷存在,所以會導致C-V曲線里面平帶電壓的位移。

3) 氧化層陷阱電荷(Oxide Trapped Charge, Qot)。它主要是由于離子輻射、FN隧穿、或者熱載流子效應造成的缺陷捕獲電子或空穴,故氧化層陷阱電荷既可以是正的也可以是負的還可以是電中性的。

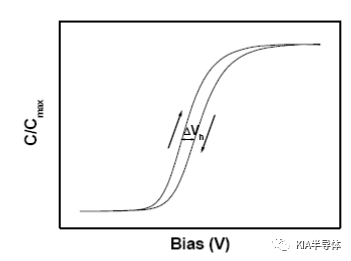

主要與氧化層品質有關,通常可以通過回火來消除俘獲電荷使其變成電中性(Neutual Trap)。由于捕獲電荷會由于初始加的電壓為正或為負導致不同,所以可以根據高頻C-V曲線的正向掃描以及反向掃描的C-V的曲線來看是否含有Qot。

這種由于初始電壓不同造成的俘獲載流子的不同回路稱之為遲滯現象(Hysteresis Effect)。我們可以據此來判斷氧化層捕獲的電荷型態以及數量。

4) 可移動離子電荷(Qm, Mobile ionic Charge)。主要來自人體或純水中的堿金屬離子(Na+, K+),或者濕氧水汽里面的H+進入氧化層,或者是氧化層中缺少氧而造成O++氧空位。這個東西主要是影響平帶電壓(Vfb)。

以上講的是GOX的電荷對C-V曲線的影響,當然影響C-V曲線的因素還有以下方面。

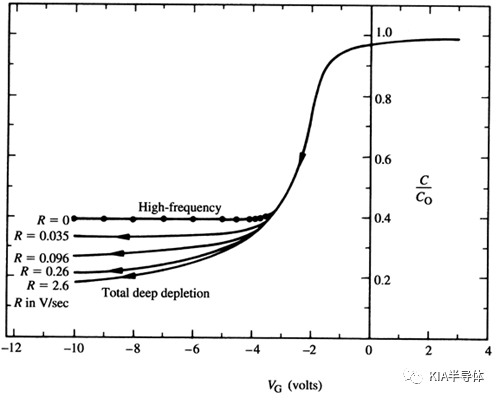

1) 頻率:我們之前將高頻由于載流子來不及響應,所以keep在最低了,而低頻在反型區電容也是最大值,所以頻率越低,反型區越向上平移。(當然實際case過程中,我們都是fix 頻率比如100MHZ去測量的)。

2) 襯底濃度:這個主要是跟反型區寬度決定的,襯底濃度越高,越難反型,所以反型區寬度越窄,所以電容變大,所以電容曲線也向上移動。

再講一個深耗盡(Deep Depletion)的概念,這個主要跟測試方法相關的。如果我們柵極電壓慢慢往上掃描,如果掃描速度過快,則反型層還來不及反型并達到熱平衡狀態,這就是我們說的深耗盡,這種情況下耗盡區寬度會持續增加,而導致電容進一步降低。所以可以嘗試減小掃描step,并優化Hold/wait time。

原文標題:使用C-V曲線查Case

文章出處:【微信公眾號:KIA半導體】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

電容

+關注

關注

100文章

6067瀏覽量

150598 -

MOS

+關注

關注

32文章

1279瀏覽量

93949 -

曲線

+關注

關注

1文章

82瀏覽量

20866

原文標題:使用C-V曲線查Case

文章出處:【微信號:KIA半導體,微信公眾號:KIA半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

能否提供ADS仿真中獲得N-MOS FD-SOI晶體管的C-V曲線?

半導體器件C-V特性測試方案

半導體C-V測量基礎(吉時利)

半導體C-V測量基礎

基于C-V模型的醫學圖像分割方法

基于C-V水平集模型的SAR圖像灰度分布不均勻的改進

吉時利2450型觸摸屏數字源表的性能特點及應用優勢

半導體器件C-V特性測試說明

AIN/AIGaN/GaN MIS異質結構C-V分析

MOS的C-V曲線與襯底濃度以及GOX特性的關系

MOS的C-V曲線與襯底濃度以及GOX特性的關系

評論