無論是x86、Arm還是新秀RISC-V,大家談及基于這些架構的處理器時,除了對比性能、功耗以外,不免會說到造就當下處理器差異化的另一大因素,那就是制造工藝。臺積電、中芯國際、三星還有英特爾,隨著如今幾乎所有代工廠都參與到RISC-V的制造中來,我們不妨挑幾個用上了先進工藝的RISC-V處理器看看。

臺積電5nm+HBM3的RISC-V處理器

去年,SiFive旗下的OpenFive,一個用差異化IP提供定制方案的業務部門宣布正式流片了基于臺積電5nm工藝的RISC-V處理器,該處理器集成的IP方案主要面向高性能計算/AI、網絡與存儲應用。

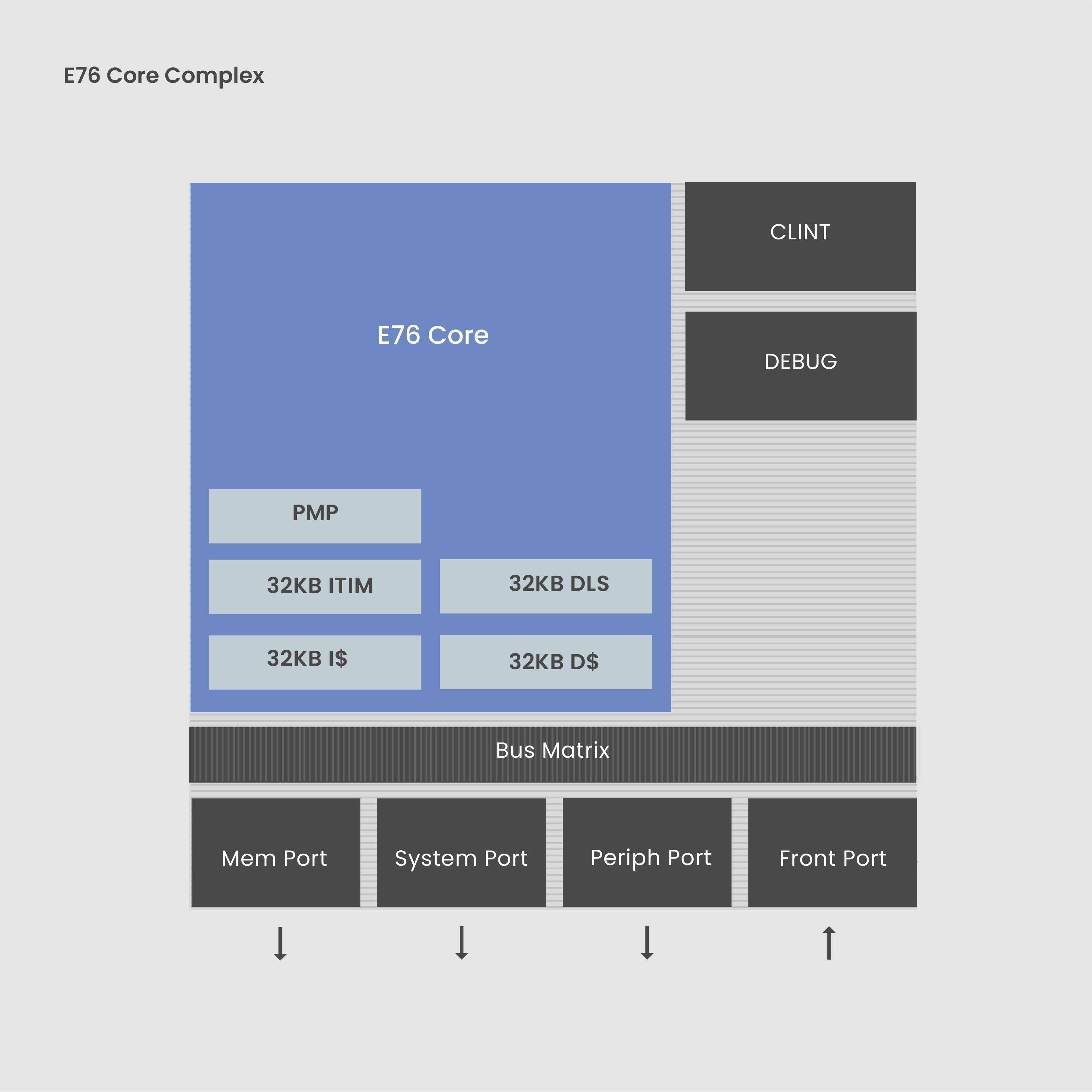

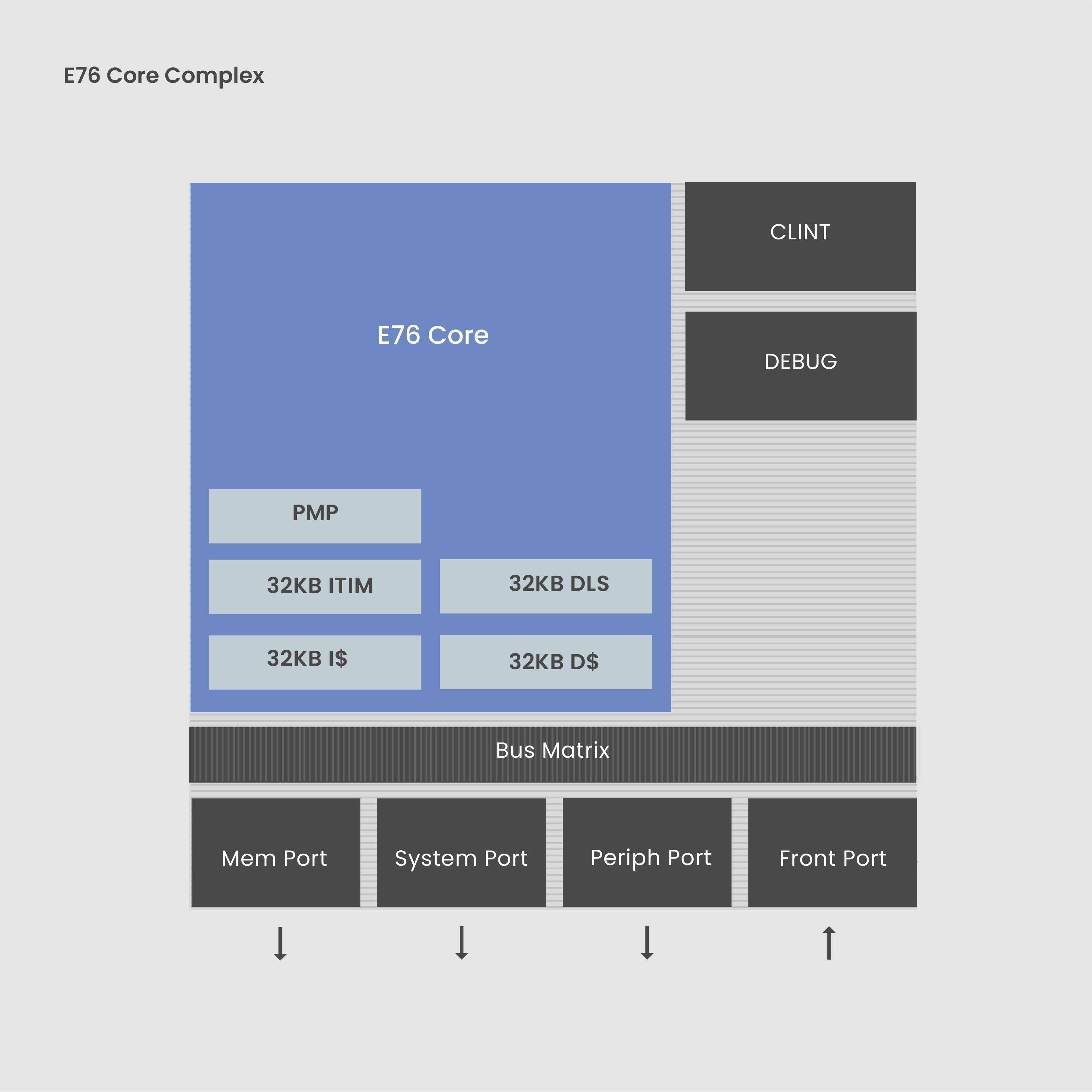

E76核心框圖/ SiFive

這款SoC用到了OpenFive的HBM3 IP子系統和D2D I/O,CPU核心則選用了SiFive的E76,8級流水線的32位RISC-V核心。其HBM3接口給到了7.2Gbps的速度,足以滿足任何計算密集型應用特定領域加速器的帶寬需求。在D2D接口技術的支持下,該SoC可以通過2.5D封裝實現更高的性能、更低的功耗與延遲。當然了,更重要的還是E76這個5.69CoreMark/Hz的RISC-V CPU核心。

不難看出,SiFive在高性能計算上有著自己的野心,哪怕目前Alphawave已經收購了SiFive的OpenFive業務部門。從SiFive和英特爾的關系來看,雙方未來也會和繼續合作,借助英特爾的IFS代工業務,為RISC-V處理器提供更先進的制造工藝,正如下面我們要提到的這款RISC-V處理器一樣。

以Intel4打造的近緩存計算RISC-V處理器

在我們已經看到的不少RISC-V處理器中,除了低功耗的以外,也有不少高性能的處理器,尤其是與AI/ML相關的。深度學習激發了一批數據并行的工作負載,而傳統的SIMD處理器雖然解決了更多通用算力的問題,但其內存帶寬還是無法這類應用的要求,這也是為何GPU和一眾加速器在AI/ML上更受歡迎的原因。

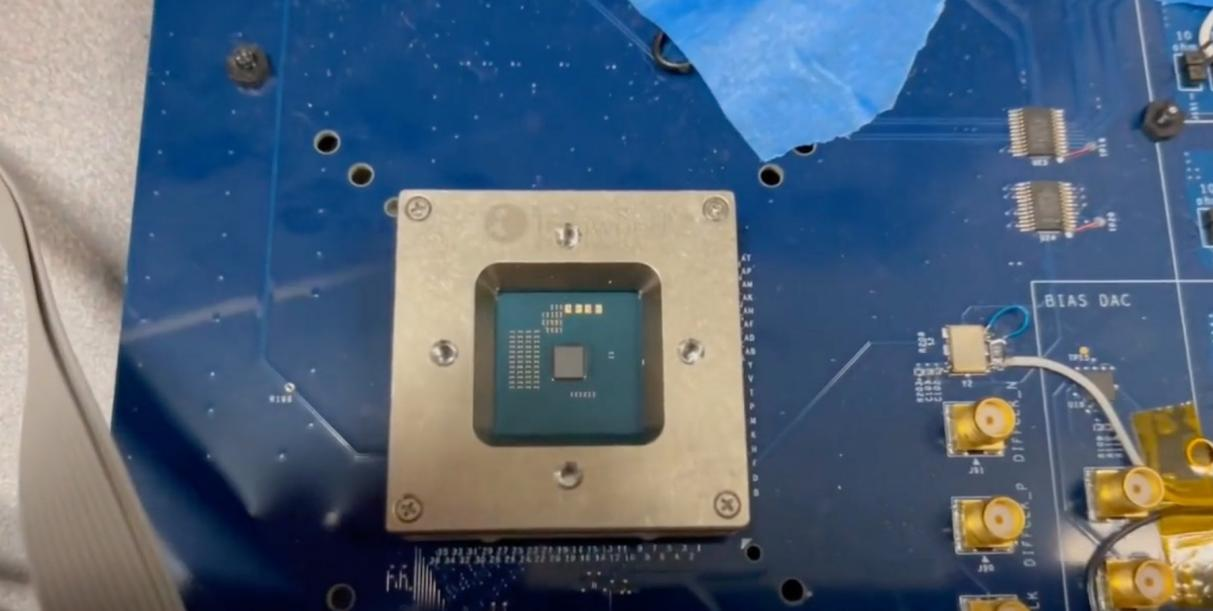

在今年的VLSI22上,英特爾的研究工程師們帶來了一個新的演示分享,一個全新的8核64位RISC-V處理器,代號Vela。該芯片完全基于Intel4的CMOS工藝打造。在這一先進工藝的助力下,這個頻率為1.15GHz的處理器僅僅占用了1.92mm2的面積,同時集成了512kB的共享LLC,每個核心分配了64kB SRAM。最關鍵的是Vela應用了近緩存計算(CNC)技術,使得該處理器在深度學習負載上展現了極佳的性能。

CNC不僅實現了高帶寬的訪問,也實現了在大容量片上SRAM中直接進行本地計算。而Vela將虛擬尋址,連貫性和一致性一并擴張到了CNC上,實現了可允許在Linux下的多核操作。與此同時,這個倒轉芯片封裝設計的處理器與一個FPGA相連,作為一個用于訪問DRAM和IO的芯片組。

英特爾在分享中展示了CNC LLC的數據路徑、CNC ISA規范以及編程模型,實際工作負載演示則為DNN提供了視覺化輸入與輸出。與將數據從LLC移動到核心內不同,CNC將成績累加運算搬到了LLC上,就地處理數據。如此一來避免了片上網絡的帶寬瓶頸,同時減少全局數據的移動,增加了吞吐量提高了能效。英特爾的研究員也給出了具體提升數據,與標量處理相比,其吞吐量提升了46倍;通過減少數據移動,其整體功耗降低了11%,推理功耗降低至52分之一;在MLPerf的異常檢測測試中,Vela將延遲降低了4.25倍,低至40μs。

不少人猜測這會不會是SiFive與英特爾打造的HorseCreek平臺,畢竟該平臺用到的也是英特爾的7nm工藝(Intel4)。不過在英特爾和SiFive雙方去年的聲明中,都提到了HorseCreek將使用SiFive的P550核心,一個13級流水線三發射的高性能RISC-V核心。但從其1.15GHz的頻率和1.92mm2的面積來看,很可能不是,至少不會是完整的HorseCreek。

結語

其實要說現在RISC-V處理器所用的工藝,還是7nm和之前的成熟工藝居多,畢竟RISC-V現在軟硬件生態都還在高速發展中,并沒有選擇與Arm或x86在通用CPU和手機SoC上硬碰硬。也許RISC-V不像Arm的公版核心一樣,有那么清晰的定位,但可以預見RISC-V未來覆蓋的市場很快就會與Arm重合,所用工藝的差距也將縮小,屆時觀察各大半導體廠商的選擇才更有趣。

臺積電5nm+HBM3的RISC-V處理器

去年,SiFive旗下的OpenFive,一個用差異化IP提供定制方案的業務部門宣布正式流片了基于臺積電5nm工藝的RISC-V處理器,該處理器集成的IP方案主要面向高性能計算/AI、網絡與存儲應用。

E76核心框圖/ SiFive

這款SoC用到了OpenFive的HBM3 IP子系統和D2D I/O,CPU核心則選用了SiFive的E76,8級流水線的32位RISC-V核心。其HBM3接口給到了7.2Gbps的速度,足以滿足任何計算密集型應用特定領域加速器的帶寬需求。在D2D接口技術的支持下,該SoC可以通過2.5D封裝實現更高的性能、更低的功耗與延遲。當然了,更重要的還是E76這個5.69CoreMark/Hz的RISC-V CPU核心。

不難看出,SiFive在高性能計算上有著自己的野心,哪怕目前Alphawave已經收購了SiFive的OpenFive業務部門。從SiFive和英特爾的關系來看,雙方未來也會和繼續合作,借助英特爾的IFS代工業務,為RISC-V處理器提供更先進的制造工藝,正如下面我們要提到的這款RISC-V處理器一樣。

以Intel4打造的近緩存計算RISC-V處理器

在我們已經看到的不少RISC-V處理器中,除了低功耗的以外,也有不少高性能的處理器,尤其是與AI/ML相關的。深度學習激發了一批數據并行的工作負載,而傳統的SIMD處理器雖然解決了更多通用算力的問題,但其內存帶寬還是無法這類應用的要求,這也是為何GPU和一眾加速器在AI/ML上更受歡迎的原因。

在今年的VLSI22上,英特爾的研究工程師們帶來了一個新的演示分享,一個全新的8核64位RISC-V處理器,代號Vela。該芯片完全基于Intel4的CMOS工藝打造。在這一先進工藝的助力下,這個頻率為1.15GHz的處理器僅僅占用了1.92mm2的面積,同時集成了512kB的共享LLC,每個核心分配了64kB SRAM。最關鍵的是Vela應用了近緩存計算(CNC)技術,使得該處理器在深度學習負載上展現了極佳的性能。

CNC不僅實現了高帶寬的訪問,也實現了在大容量片上SRAM中直接進行本地計算。而Vela將虛擬尋址,連貫性和一致性一并擴張到了CNC上,實現了可允許在Linux下的多核操作。與此同時,這個倒轉芯片封裝設計的處理器與一個FPGA相連,作為一個用于訪問DRAM和IO的芯片組。

英特爾在分享中展示了CNC LLC的數據路徑、CNC ISA規范以及編程模型,實際工作負載演示則為DNN提供了視覺化輸入與輸出。與將數據從LLC移動到核心內不同,CNC將成績累加運算搬到了LLC上,就地處理數據。如此一來避免了片上網絡的帶寬瓶頸,同時減少全局數據的移動,增加了吞吐量提高了能效。英特爾的研究員也給出了具體提升數據,與標量處理相比,其吞吐量提升了46倍;通過減少數據移動,其整體功耗降低了11%,推理功耗降低至52分之一;在MLPerf的異常檢測測試中,Vela將延遲降低了4.25倍,低至40μs。

不少人猜測這會不會是SiFive與英特爾打造的HorseCreek平臺,畢竟該平臺用到的也是英特爾的7nm工藝(Intel4)。不過在英特爾和SiFive雙方去年的聲明中,都提到了HorseCreek將使用SiFive的P550核心,一個13級流水線三發射的高性能RISC-V核心。但從其1.15GHz的頻率和1.92mm2的面積來看,很可能不是,至少不會是完整的HorseCreek。

結語

其實要說現在RISC-V處理器所用的工藝,還是7nm和之前的成熟工藝居多,畢竟RISC-V現在軟硬件生態都還在高速發展中,并沒有選擇與Arm或x86在通用CPU和手機SoC上硬碰硬。也許RISC-V不像Arm的公版核心一樣,有那么清晰的定位,但可以預見RISC-V未來覆蓋的市場很快就會與Arm重合,所用工藝的差距也將縮小,屆時觀察各大半導體廠商的選擇才更有趣。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

英特爾

+關注

關注

61文章

9984瀏覽量

171951 -

臺積電

+關注

關注

44文章

5651瀏覽量

166670 -

RISC-V

+關注

關注

45文章

2294瀏覽量

46249

發布評論請先 登錄

相關推薦

消息稱臺積電3nm、5nm和CoWoS工藝漲價,即日起效!

)計劃從2025年1月起對3nm、5nm先進制程和CoWoS封裝工藝進行價格調整。 先進制程2025年喊漲,最高漲幅20% 其中,對3

Andes晶心科技推出D45-SE RISC-V處理器

Andes晶心科技(TWSE:6533; SIN US03420C2089; ISIN:US03420C1099)是全球高效能、低功耗 32/64 位 RISC-V 處理器的領導廠商,也是

Rivos全新產品采用Andes晶心科技NX45 RISC-V處理器

專注于加速數據分析和生成式AI工作負載的RISC-V主要會員公司Rivos與32/64位RISC-V處理器內核的領先供貨商、RISC-V創始會員Andes晶心科技,宣布Rivos已獲得

《RISC-V能否復制Linux 的成功?》

,創建實現自有加速器算法的自定義異構集群。RISC-V作為一種ISA,我們一開始是在處理器內核中采用吸引人的通用構建塊,然后在此基礎上進行構建,同時還利用最好的商業工具增強使用者的信心。所以,IP

發表于 11-26 20:20

臺積電產能爆棚:3nm與5nm工藝供不應求

臺積電近期成為了高性能芯片代工領域的明星企業,其產能被各大科技巨頭瘋搶。據最新消息,臺積電的3nm和5nm工藝產能利用率均達到了極高水平,其中3nm將達到100%,而

4nm!小米 SoC芯片曝光!

SoC芯片解決方案,據說該芯片的性能與高通驍龍8 Gen1相當,同時采用臺積電4nm“N4P”工藝。 爆料人士@heyitsyogesh 沒有提供該定制芯片的名稱,但他提到了小米內部SoC芯片的一些細節。例如,采用臺積電的

消息稱臺積電3nm/5nm將漲價,終端產品或受影響

據業內手機晶片領域的資深人士透露,臺積電計劃在明年1月1日起對旗下的先進工藝制程進行價格調整,特別是針對3nm和5nm工藝制程,而其他

請問ESP32s3 ULP RISC-V協處理器是否支持ADC的讀取?

我在ULP RISC-V協處理器的例程中,沒有發現有對ADC的操作,請問RISC-V協處理器目前還不支持嗎?使用的IDF版本為4.4.2。

我想在ULP模式下,通過ADC來讀取外部器件

發表于 06-14 07:38

聯發科將發布4nm工藝天璣9300+芯片

4nm工藝打造,采用四顆超大核+四顆大核組合架構。天璣9300?Plus處理器作為天璣9300的升級加強版,在配置和性能上均有了顯著提升。采用了高性能的Cortex-X4超大核設計,主

臺積電升級4nm N4C工藝,優化能效與降低成本

在近日舉辦的 2024 年北美技術研討會上,業務發展副總裁張凱文發表講話稱:“盡管我們的 5nm 和 4nm 工藝尚未完全成熟,但從 N5 到 N4

國產RISC-V MCU推薦

,CH583搭載32位青稞RISC-V處理器WCH RISC-V4A,低功耗兩級流水線,高性能,擁有多檔系統主頻,最低32KHz ,擁有特有高速的中斷響應機制。

單片搞定Wi-Fi和藍牙

許多網友也

發表于 04-17 11:00

RISC-V 基礎學習:RISC-V 基礎介紹

縮寫

[###]

用于標識處理器位寬,取值[32, 64,128],也就是處理器的寄存器位寬

[abc...xyz]

標識該處理器支持的指令模塊集合

比如:RV64IMAC, 表示6

發表于 03-12 10:25

芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案

本土RISC-V CPU IP領軍企業——芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案,提供專業有效的信息安全保護以及加解密功能。

4nm、5nm,那些用上先進工藝的RISC-V處理器

4nm、5nm,那些用上先進工藝的RISC-V處理器

?

?

評論