PhiGent Heimdallr - 基于Xilinx KV26的立體視覺匹配方案

概要:

立體視覺匹配的目標是從不同視點圖像中找到匹配的對應點,最終輸出RGBD的深度圖像。

在本文中,我們將首先對基于AI 的雙目立體匹配算法進行介紹,接著會對本方案中使用的 Xilinx Vitis AI Tools 和 Xilinx Vitis Flow 開發流程進行介紹。

目標及原因:

深度估算是自動駕駛領域的一項關鍵技術。作為自動駕駛中最常用的傳感器,攝像頭能夠獲取全面、豐富又密集的信息。基于立體視覺的深度估算技術可以準確識別和定位運動與靜止目標以及路面對象。隨著深度學習技術的迅猛發展以及大規模立體數據集的問世,基于神經網絡的立體視覺匹配算法得以快速發展,計算精度與效率均超過了傳統算法。借助強大的特征提取功能,基于深度學習的端到端雙目立體匹配技術能確保具有弱紋理和重復紋理的對象仍然可以輸出有效的高精度深度信息,從而滿足智能駕駛系統在各種場景下的感測需求。

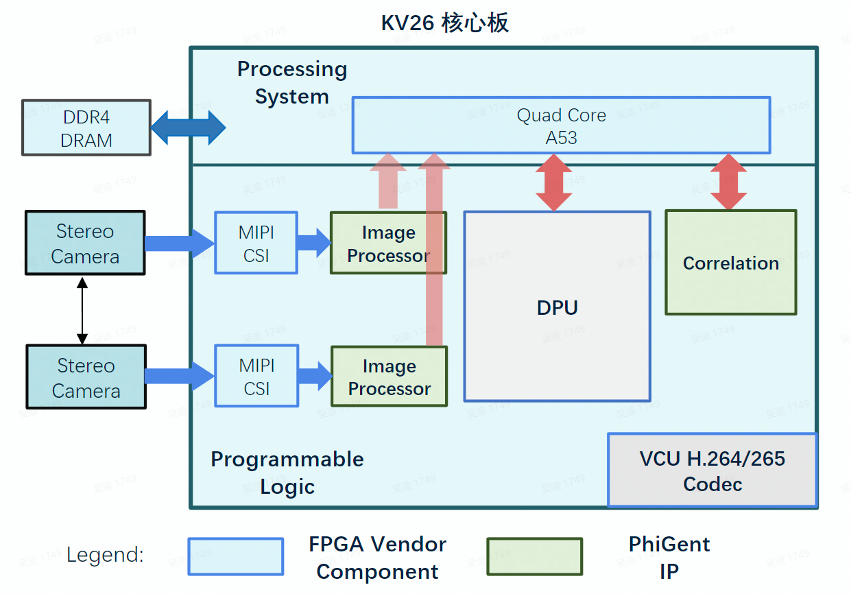

本方案使用了最新的基于卷積神經網絡的立體視覺匹配算法,并通過Xilinx VitisAI 工具包,將該算法中的卷積網絡部分部署至賽靈思深度學習處理器(DPU)上進行加速。同時,算法中無法使用 DPU 加速的部分,如相關層操作則使用了專用的定制IP 進行加速。除此之外,本方案還定制了專用的圖像預處理 IP 用來進行輸入圖像的預處理操作。

本方案可以部署至賽靈思 KV260 開發板或者基于 KV26 核心板的專用定制開發板Heimdallr-DEB。

基于 KV260 開發的方案由于受限于雙目立體視覺模組的硬件接口限制,僅能使用數據回灌方式驗證深度估計效果。基于本方案定制的 Heimdallr-DEB 開發板方案則能使用配套的雙目立體視覺模組,將本方案部署至汽車上,在車輛行駛過程中實時展示立體匹配效果。

技術方案介紹

本方案將從以下幾個部分進行介紹:

模型的選擇及調優;

FPGA PL側開發流程;

軟件配套程序開發;

方案部署及運行。

1

模型的創建及調優

模型選擇:

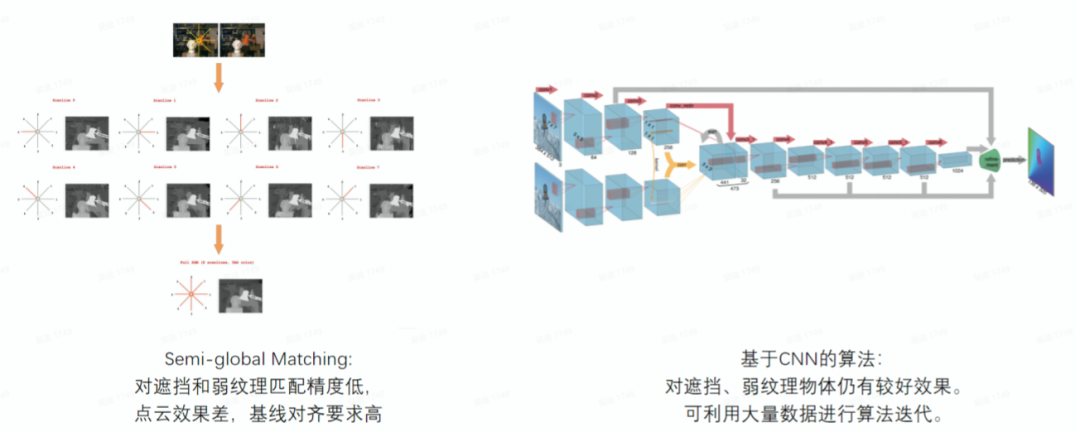

基于神經網絡的雙目立體視覺方案首先需要選定算法。在深度學習大火之前,研究者們都使用基于規則的方法去進行視差匹配,這些典型的傳統算法有:SGM,SGBM等。在卷積神經網絡迅速發展后,有大量學者使用基于 CNN 的方法進行立體視覺匹配算法的研究。目前,根據在 Kitti 2015 測試數據集上準確率較高的幾種 CNN 算法,有 Raft-Stereo, GA-Net, FADNet 等。基于神經網絡的匹配算法在遮擋、弱紋理區域仍能獲得非常好的效果,同時可以利用持續更新的數據集對算法進行迭代。

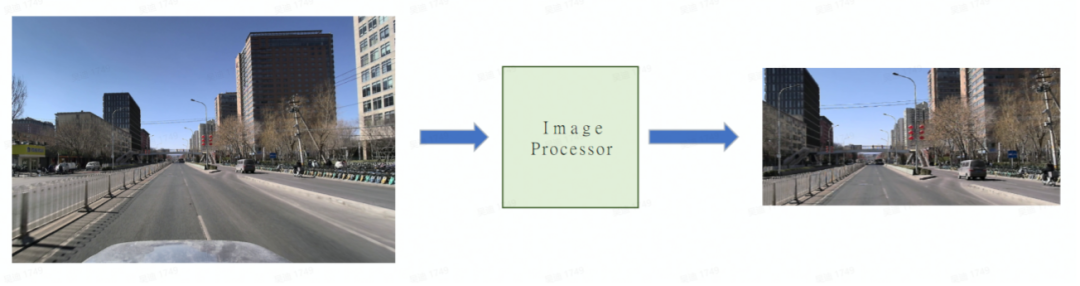

圖1:傳統匹配算法與基于CNN匹配算法的對比

但同時,這些基于神經網絡的算法或者計算量太大,或者使用了特殊的操作導致不適合部署到 FPGA 上實現。我們針對 FPGA 器件的特點,為充分利用 FPGA 的計算特性,提高計算效率,結合了幾種主流神經網絡算法的特點,創造出適合部署在 FPGA 器件上的網絡模型 PhiFADNet - PhiGent Fast and Accurate Disparity Network。PhiFADNet 計算量小,網絡結構簡單但保留了雙目神經網絡算法中最重要的 correlation 層,使得該算法在低算力的同時還能報錯不錯的準確率。

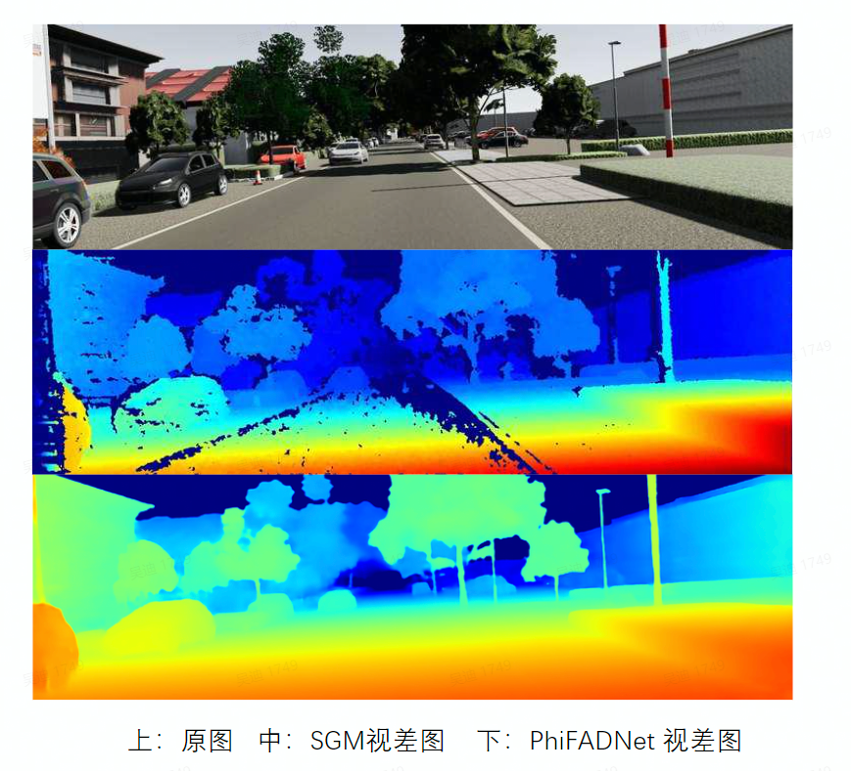

我們挑選了 Kitti 數據集中公開的一張圖片,并分別使用了SGM 和 PhiFADNet 進行視差匹配,發現使用 PhiFADNet 的視差結果,在地面等弱紋理區域有更好的連續視差結果,同時在細小物體出的檢測更加準確,整體的視差圖噪聲和飛點較少。

圖:SGM與 PhiFADNet 視差圖對比

模型量化和編譯:

Xilinx Vitis AI 提供了整套的工具用來對用戶自定義網絡進行 裁剪、量化和訓練。Vitis AI 軟件可作為 Docker 鏡像使用并且可從 Docker hub (xilinx/vitis-ai Tags | Docker Hub)下載。Vitis AI 用戶指南(Vitis AI User Guide)則提供了詳細的分步說明。我們使用 Xilinx Vitis AI Tools 對這三個網絡進行 Quantization-aware training (QAT). Xilinx Vitis AI Tools 包括AI Optimizer, AI Quantizer, AI Compiler和 AI Profiler。

模型測試效果:

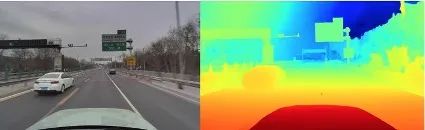

我們使用雙目模組在實車高速公路場景上采集了大量數據并進行了訓練,訓練后的模型效果在實際場景中的表現如下。

圖:PhiFADNet 實車路段視差圖展示

2

FPGA PL 側開發

Correlation Accelerator:

FADNet 結構中的相關層操作-correlation 并不能直接部署到 Xilinx DPU上,因此我們需要單獨把 correlation 操作提取出來進行運算。根據測試結果,如果使用 ZU5 芯片上的 4核 ARM-A53 進行correlation操作,共耗時80ms,而整個神經網絡其他部分使用DPU 運行的時間加起來也就80ms。使用 ARM 完成 correlation極大的增加了整個網絡的延時,而自動駕駛場景對延時有著嚴格的要求。因此我們考慮使用 FPGA 對 correlation 進行操作。

根據 correlation 操作的特點,我們定制化了一個專用 Correlation Accelerator IP 對其進行加速。由于 correlation操作的輸入和輸出都需要連接至 DPU,因此我們需要對改操作進行定點化操作,并支持 PS 進行 shift 移位配置。使用 FPGA 進行加速后的 Correlation 操作能獲得相比與 PS 處理時間 20倍的加速比。加速后的 Correlation 操作能極大的縮短雙目立體視覺的匹配延時。

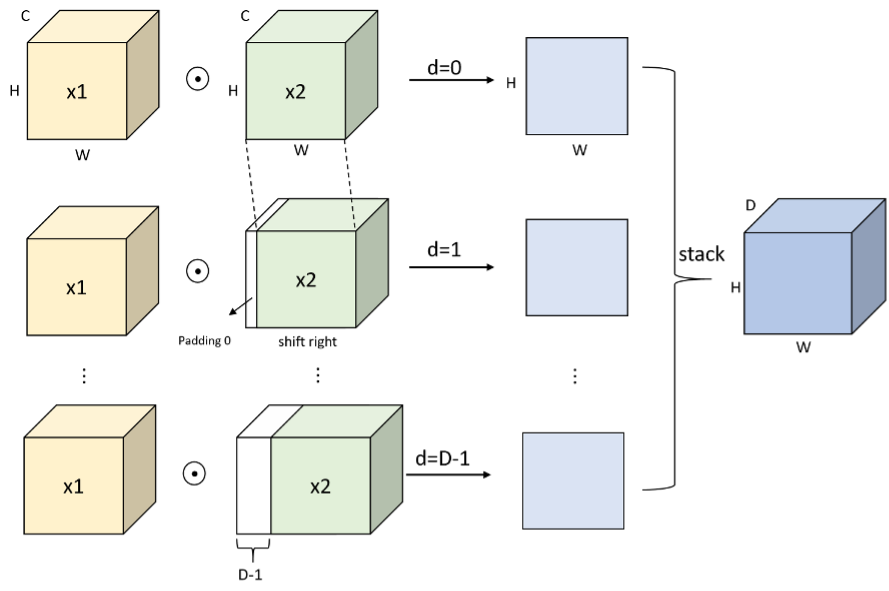

比較典型的 correlation 操作示意圖如下圖所示:

圖:Correlation 流程示例圖

圖像前處理:

無論是基于傳統算法或者神經網絡的雙目立體匹配系統,對圖像前處理都有著較高的要求。圖像前處理通常包括 ISP、畸變矯正、極線對齊、圖像下采樣等。

ISP模塊我們使用模組自帶的 ISP 芯片或者開發板上的 ISP 處理芯片完成圖像信號處理。

畸變矯正和極線對齊處理,我們可以通過標定獲取雙目攝像頭模組的內外參數并獲得矯正矩陣,通過該矯正矩陣可以同時完成圖像的畸變矯正和極線對齊。由于該操作主要是將圖像數據根據矯正矩陣進行重拍,使用PS 端 ARM 處理器進行該操作可以獲得較高的效率,同時節省部分 PL 資源。

最后在圖像輸入神經網絡處理前,我們需要對矯正對齊后的圖像進行下采樣處理。下采樣處理的主要目的是去除左右圖像中的無視差區域以及部分非感興趣區域(如:自動駕駛中的天空區域),下采樣后的圖像尺寸為神經網絡的輸入尺寸。我們使用 FPGA PL 部分來對該下采樣操作進行加速。加速后的下采樣操作針對單幅 2M pixel 圖像的處理時間縮減為 7ms,而使用 PS 部分進行該操作需要大概28ms。

圖像前處理的作用:去除圖像中的無視差區域;剔除圖像中的非感興趣區域(天空,車頭等);根據網絡尺寸動態調整輸入大小。

圖:圖像前處理剔除非感興趣區域

整體FPGA設計框架:

根據前文描述,整體FPGA設計框架包括雙目圖像前處理模塊(Image Processing),神經網絡加速器模塊(Xilinx DPU), 相關層加速模塊(Correlation IP)。本方案使用PS和PL協同工作,PS部分主要負責圖像校正對齊,數據調度,流程控制等。整個方案運行時,PS和PL的使用率都能達到80%以上,同時通過流水線并行處理使得整個系統能獲得最優的吞吐率。整個 FPGA 的設計框架如下所示:

圖:基于kv26核心板的 FPGA 設計框架

FPGA工程制作:

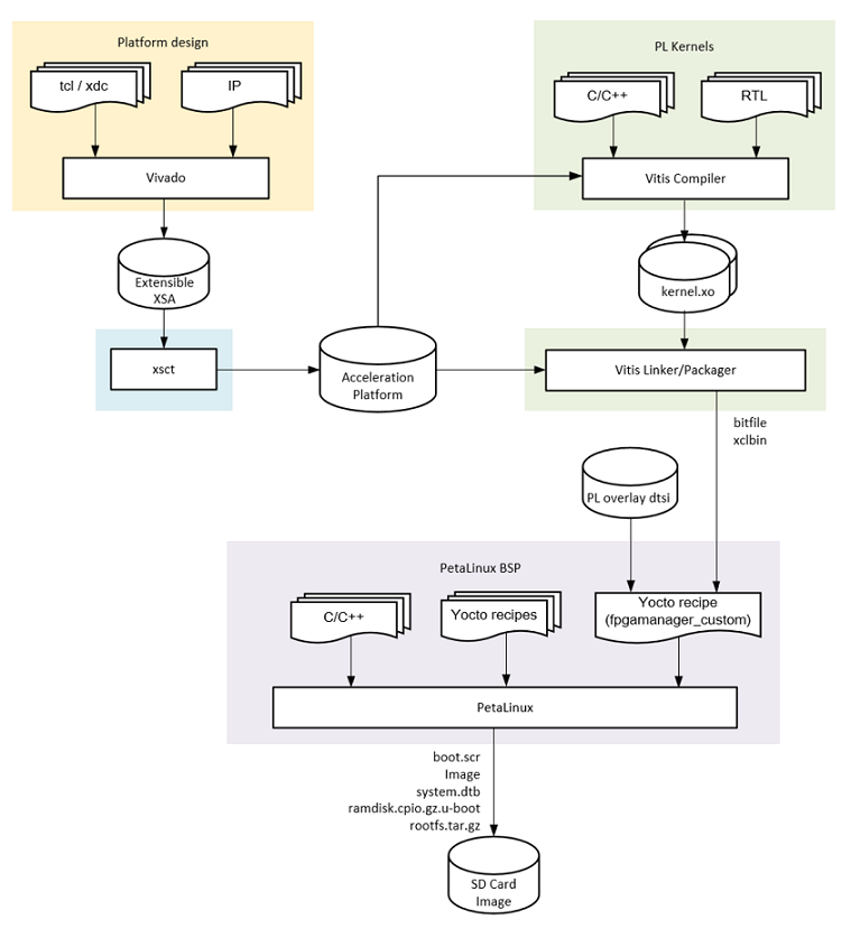

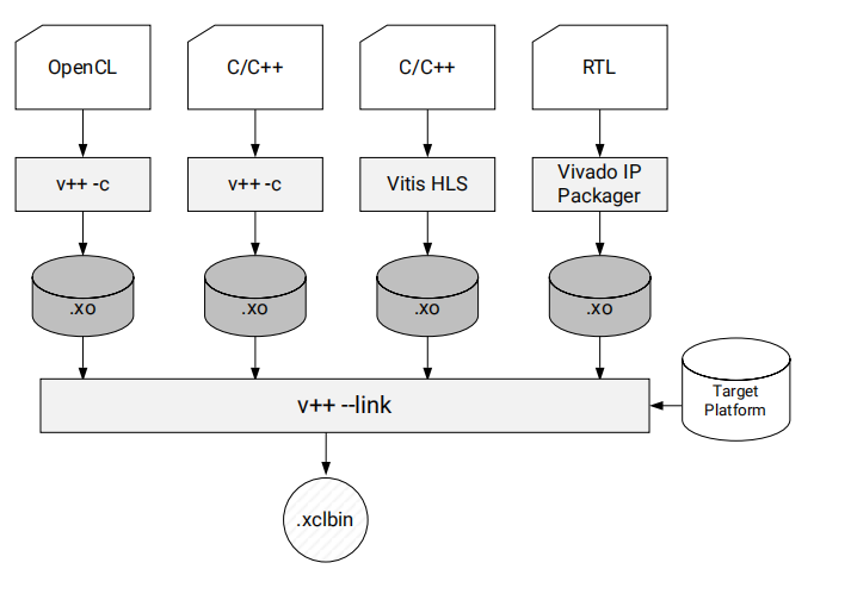

本方案使用 Xilinx Vitis Flow 完成整個 FPGA 工程的開發流程。整個 Vitis Flow 的開發流程如下圖所示(注:開發環境需要安裝有 Vivado 2021.1 和 Vitis 2021.1):

圖:Vitis Flow 開發流程示意圖

Vitis Platform Flow:

首先我們需要制作開發板對應的 platform。本方案提供了兩套實現方案,分別是基于 Xilinx KV260 開發板和 Phigent Heimdallr-DEB 開發板。兩套開發板的核心板都為 K26 SOM 核心板,僅在外圍的 GMSL 接口上有主要不同(Phigent Heimdallr-DEB 可以接入 Phigent 定制化雙目模組)。因此兩套方案可以使用相同的 Vitis Platform。

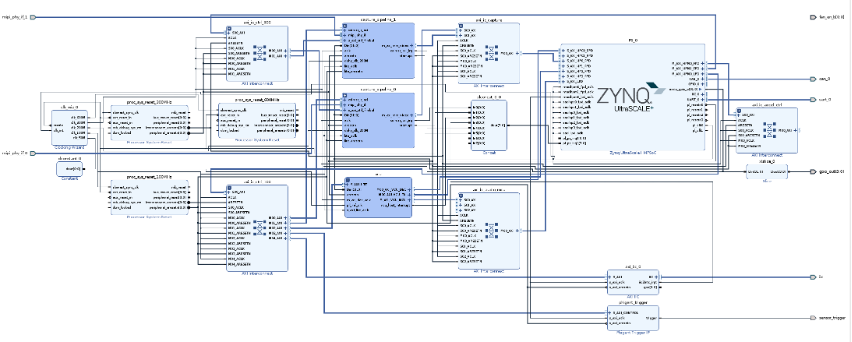

Vitis Platform Flow 首先需要使用 Vivado 生成定制化的 PL design。我們選定工程的芯片型號為 K26 SOM,然后在 vivado block design 中添加本方案需要的 platform 組件,包括 Xilinx MIPI RX Controller,VCU,Phigent Image Processor 和配套的 interconnect 等。整個 platform 的 block design 設計概覽如下圖所示。完成 Platform 的設計后,使用 Vivado 工具生成 .xsa 文件,該文件在后續配套的 petalinux 工程中還會進一步使用。

圖:使用 Vivado 生成 Block Design

生成 .xsa 文件后,使用 vitis 提供的 xsct 命令生成 pfm 文件,該文件會在后續用于集成 HLS/RTL kernel 并生成最后的 xclbin。

PL kernels:

Vitis Flow 將 FPGA 工程分成了 platform 和 PL kernels 兩個部分。其中 Platform 中用于配置工程中需要的基礎功能 IP、硬件接口、硬核/軟核設備等。PL kernels 為用戶自定義生成的一些加速IP,如本方案中使用 correlation IP 和 Xilinx DPU 均屬于 PL kernels。

開發完 Correlation IP 后,我們需要使用 Vitis Compiler 將 RTL kernel 編譯成可集成進Vitis Flow 的 kernel.xo 文件。Xilinx DPU 在官方 kv260 例程中有提供生成 kernel.xo 的流程,參考鏈接為:https://github.com/Xilinx/kv260-vitis。

Device Build Process

圖:Vitis Linker 鏈接 Platform 和 PL Kernels

準備好 Target Platform 和 PL kernels 后,最后使用 vitis V++ 命令將 Platform 和 PL kernel 鏈接起來并生成最后的 .xclbin 文件。

本方案中使用的整個Vitis Flow 流程可以參考:

https://github.com/PhigentRobotics/Phigent_Heimdallr

在該 git repository 中,已通過自動化腳本將整個 vitis flow 全部打包完成,用戶使用 make overlay OVERLAY=heimdallr 命令后就能自動跑完整個 vitis flow 流程并生成上板所需的 bit 文件和 xclbin文件。

3

軟件配套程序開發

軟件配套開發主要包括片上 linux 系統、 PS端應用軟件、PC端應用軟件的開發。

Linux 系統開發:

我們使用 Xilinx 官方提供的 petalinux 工具來為開發板量身定制 uboot、kernel、rootfs。

首先我們需要創建 petalinux工程,使用如下命令,template 參數表明創建的 petalinux 工程使用的平臺模板,從k26開發板bsp文件導入。

? petalinux-create -t project xilinx-k26-starterkit-v2021.1-final.bsp -n (工程名字)

接著我們需要導入 vivado 工程中生成的bit等,利用petalinux-create創建fpga app。

? petalinux-create -t apps --template fpgamanager -n

在本方案中,我們修改的主要是 device tree 和 kernel 文件。在 FPGA工程中我們使用了定制化的 image processing IP 對圖像進行前處理,所以需要配置相對應的驅動文件。使用如下命令來配置 linux 內核。

? petalinux-config -c kernel

設備樹文件需要修改 petalinux 工程中生成的 dtsi 文件。在該文件中加入 image processing IP 的設備描述。

配置完成后,執行如下命令進行編譯:

? petalinux-build

編譯完成后使用前面生成的所有文件和 bit 文件生成 BOOT.BIN 文件。

? petalinux-package --boot --fsbl --fpga --u-boot --force

最后生成鏡像文件

? petalinux-package --wic --bootfiles "ramdisk.cpio.gz.u-boot boot.scr Image system.dtb BOOT.BIN" --wic-extra-args "-c xz"

鏡像文件會保存在build/images/目錄下,文件名為petalinux-sdimage.wic.xz

PS應用程序開發:

由于本方案采用的是 PS 和 PL 部分協同工作的模式,PS 側需要調度 PL 側的 MIPI Controller、Image Processor、Correlation IP 和 DPU 來完成整個雙目立體視覺方案的實施。

圖像獲取:

基于V4L2框架接口初始化mipi、Image Processor等,分別獲取兩路sensor圖像,通過時間戳進行雙目圖像同步。

算法計算:

Xilinx Vitis AI 框架下,將左右camera圖像送入模型進行推理,得到視差結果。

1. 左右圖像分別做圖像預處理,包括圖像極線對齊,從圖像中切割出感興趣區域等。

2. 然后左右圖分別送入網絡提取特征。

3. 再做correlation計算后送入網絡進行視差預測。

Correlation IP調用:

應用程序利用xrt運行時庫與correlation ip進行交互,將運算輸入數據的地址和輸出數據地址設置到correlation ip寄存器,等計算完畢后將輸出結果送入解碼網絡。

PC端應用軟件開發:

PC端的應用程序需要通過網口接收來自 FPGA 開發板生成的前處理后的左右原圖,以及顯示最后生成的深度圖。

依賴三方庫

1. Grpc

2. Protobuf

3. Qt5

4. OSG (Open Scene Graph)

雙目設備用戶開發SDK:基于grpc、protobuf與PS側grpc server通信,從設備獲取校正后圖像和視差圖,經過同步后同時給到應用程序。

PC端應用程序:基于Qt5設計界面程序,使用雙目設備用戶開發SDK從設備獲取圖像和結果

4

方案部署及運行

硬件準備:

? FPGA 開發板:Xilinx KV260 或者 Phigent Heimdallr-DEB (非官方開發板,如有需要請單獨聯系)

? TF SD 卡 及配套的讀卡器

? Micro USB 線,網線

? Ubuntu 系統 PC

? 安裝有 Vivado 2021.1 和 Vitis 2021.1 的服務器

SD卡文件準備:

Git 路徑:

https://github.com/PhigentRobotics/Heimdallr_software

該 git repo 包含FPGA板卡上的可執行應用程序、BOOT 文件、PC端的應用程序、BSP文件、模型等。根據 git repo 里 README的描述,將鏡像文件下載至 SD 卡內。同時將 boot_fs 內的文件都放入 SD 文件夾內。

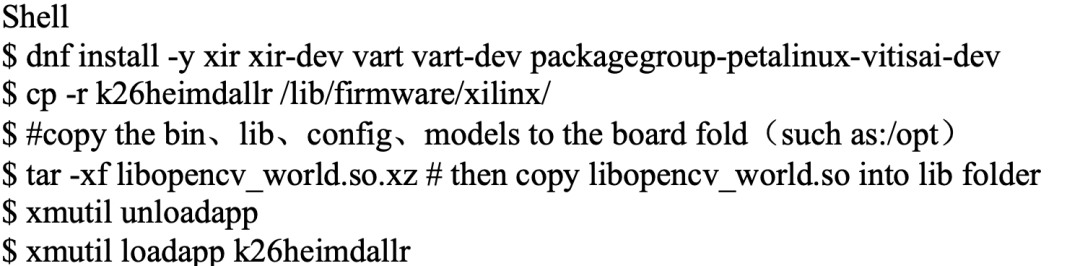

軟件配置:

將 heimdallr-hmi-bin.tgz 文件解壓至 Ubuntu PC 上,該應用程序用于獲取左右圖和最后輸出的深度圖的顯示。

在 FPGA 的片上系統上安裝 vitis ai 相關環境,將模型文件,配置文件等拷貝到相應文件夾。

程序運行:

On board(for kv260):

1.cd /opt/

2.sh bin/run_heimdallr-app_playback.sh & # kv260 development kits

On board(for heimdalr-DEB):

3.cd /opt/

4.sh bin/bin/run_heimdallr-app.sh & # Heimdallr-DEB development kits

On PC:

5. cd heimdallr-hmi-bin

6. ./AppRun.sh

審核編輯 :李倩

-

神經網絡

+關注

關注

42文章

4789瀏覽量

101830 -

算法

+關注

關注

23文章

4658瀏覽量

93983 -

Xilinx

+關注

關注

72文章

2175瀏覽量

123383

原文標題:基于Xilinx KV26的立體視覺匹配方案

文章出處:【微信號:vision263com,微信公眾號:新機器視覺】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

雙目立體視覺原理大揭秘(一)

雙目立體視覺原理大揭秘(二)

基于立體視覺的變形測量

雙目立體視覺的運用

雙目立體視覺在嵌入式中有何應用

基于HALCON的雙目立體視覺系統實現

圖像處理基本算法-立體視覺

Humanplus人加為各類機器人提供立體視覺感知解決方案

雙目立體計算機視覺的立體匹配研究綜述

評論