前序

對于激勵文件,我常用的是直接手寫,最初學這個的時候,好像是用的Quartus里的那個Modelsim-Altera的工具去弄了下圖形化編輯去制作約束,現在講到這ModelSim了,也就再撿點來折騰下,還是有點學習價值,畢竟編輯的約束就真的很“直觀”了。

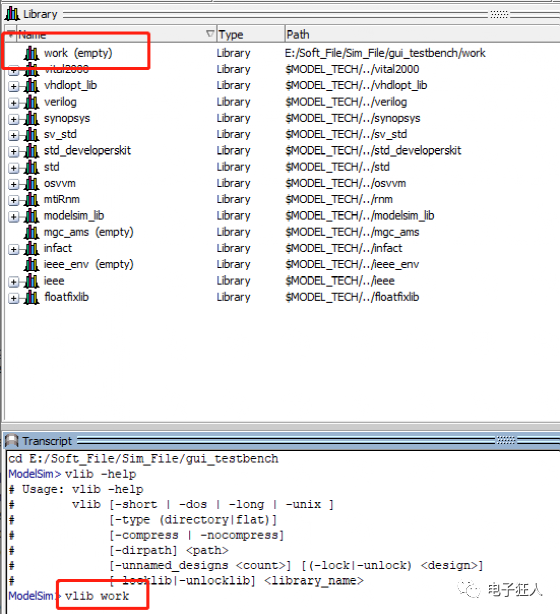

編譯文件

其他的就不多回憶了,直接開正題吧,一如既往,把待用的文件準備好,這次就只需要一個counter.v的文件,然后把ModelSim的當前路徑切換到你文件所放的路徑,接著在腳本窗口敲:

vlib work

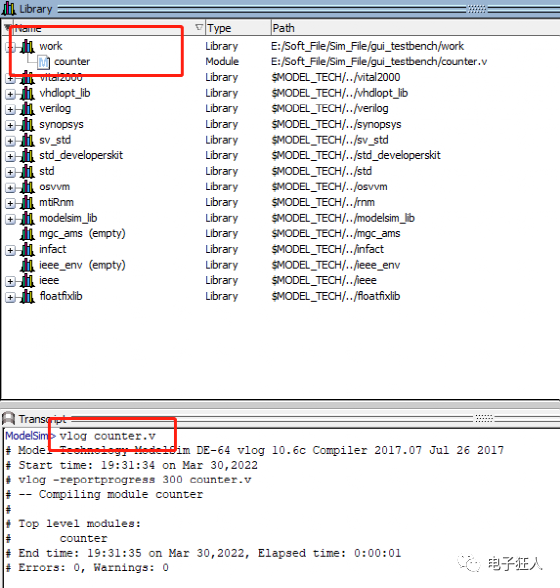

再把文件編譯一下:

vlog counter.v

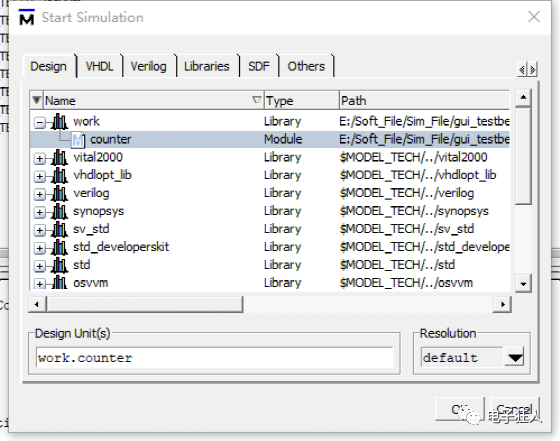

在菜單欄里 Simulate => Start Simulation,彈出來的窗口把文件選好準備進仿真界面;

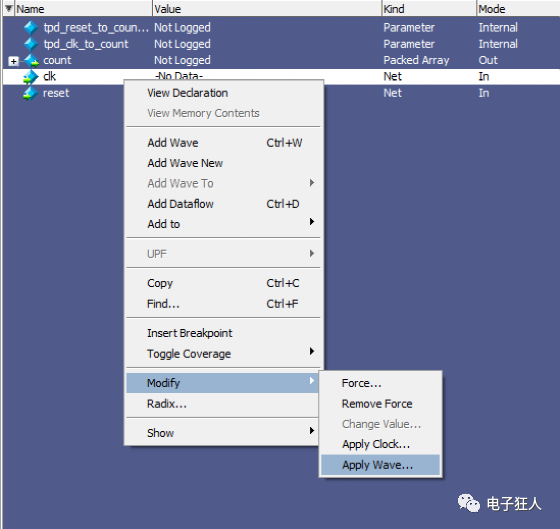

產生激勵信號

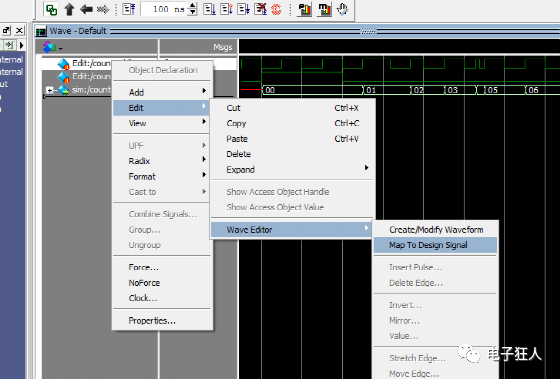

在仿真的界面,選中Objects的窗口里的clk,右鍵如下操作:

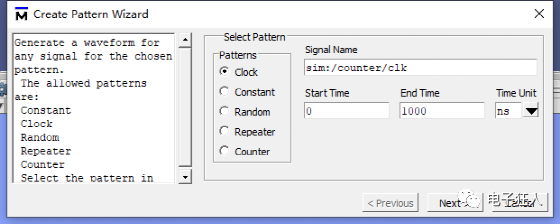

出來的界面,就是設置類型,然后就是開始和結束的時間,精度都是ns,根據自己情況改,我就默認Next下去

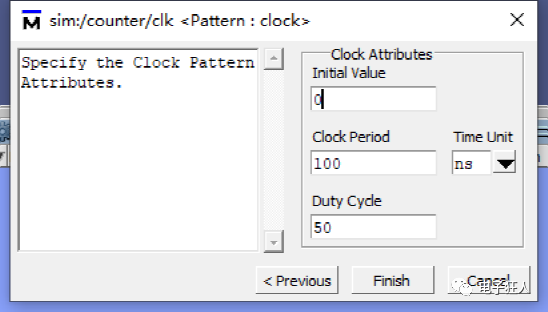

這個窗口就是讓你配時鐘參數,占空比、周期之類的,初始值寫個0進去

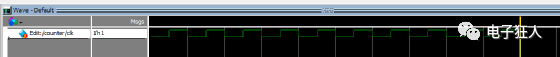

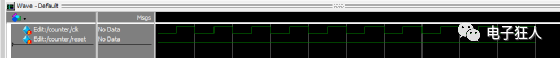

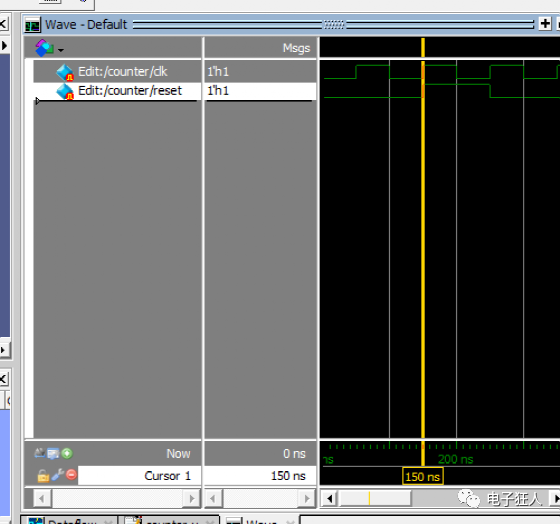

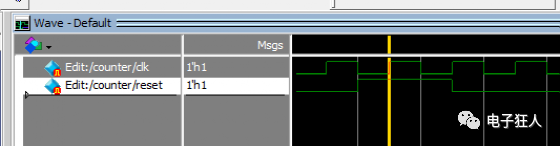

接著就在Wave的界面出現一個帶“Edit”還有紅色標記的clk信號

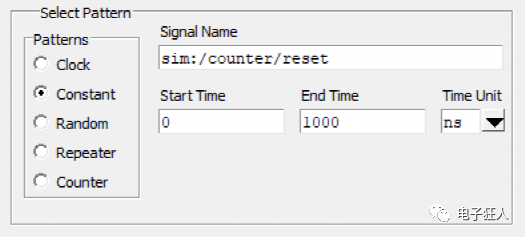

時鐘有了,就再加個復位信號

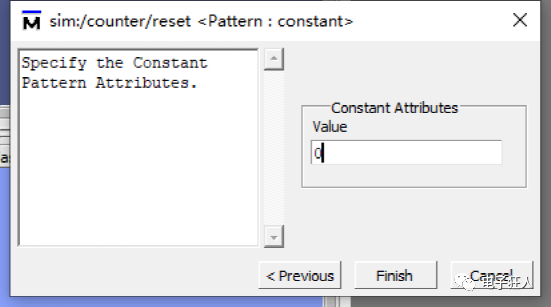

操作與上類似,類型就選個常數

把變量值寫個0

結束后,就有復位信號出現了

因為這個文件的功能比較簡單,所以有這兩個信號就夠用了,接著演示下怎么圖形化的去編輯波形,從而得到自己想要的激勵形式;

編輯激勵信號

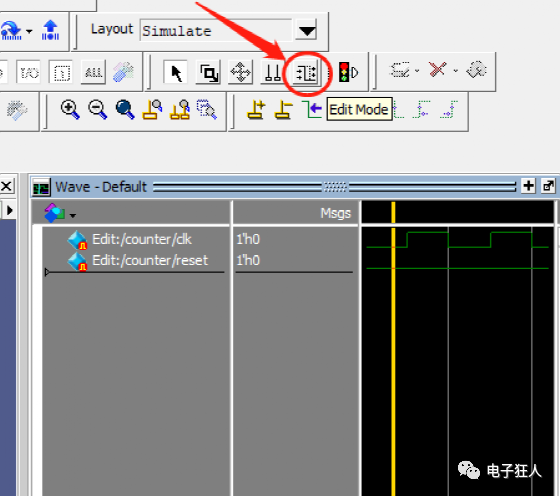

因為代碼是使用的高電平復位,所以先讓復位工作起來,再停止復位,就相當于在現在的0常量里頭加一個高電平脈沖,先鼠標點下Wave的界面,然后工具欄里的這個Edit Mode的圖標就會生效

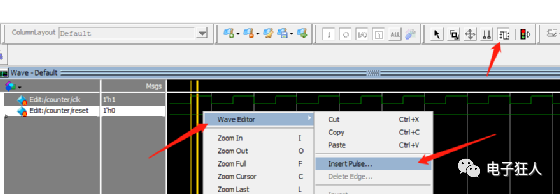

把模式切換到編輯模式,選中reset,右鍵后的Wave Editor就可以看到Inset Pulse的功能

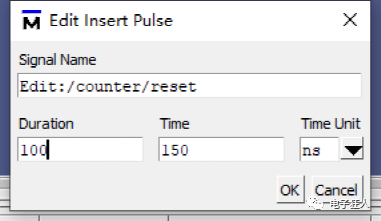

出現的設置項,就是要保持多長時間,已經開始插入脈沖的時刻;

reset就發生對應的變化

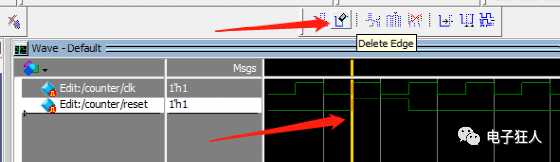

如果添加的不對,就可以選擇好添加脈沖的邊沿時刻,然后再工具欄找到“Delete Edge”的圖標(右鍵Wave Editor里也是一樣),點一下,出現的窗口是需要刪除的邊沿時刻,確定后就會把這個對應的時刻后邊的整個邊沿連續的部分,都刪除(刪除了記得再插回去哈,接著往下演)

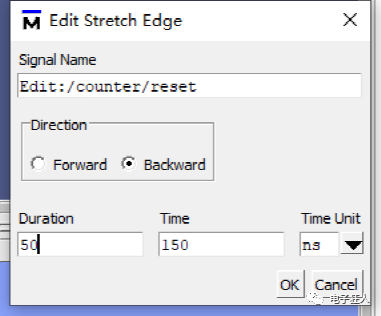

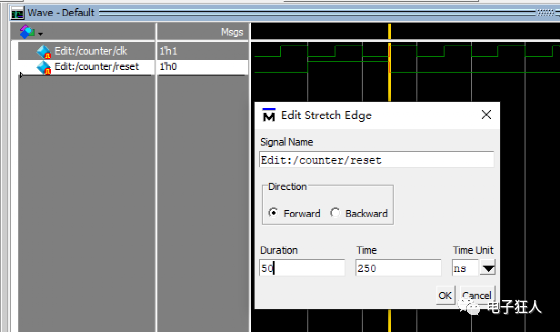

如果復位時間感覺不夠,就再補個拉伸的操作,把邊沿擴長,比如在150ns的時刻,從后向前補50ns(就相當于高電平在前面的50ns)

然后就可以看到效果了,在邊沿拉升到了100ns處

如果要往后面補,就選后邊沿,從前往后補

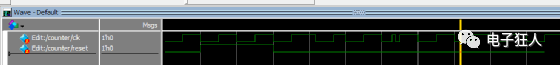

編輯上就是這樣根據自己情況去插入或者刪除多余的狀態,然后再過一下,把時鐘的信號隨便打亂幾拍(亂操作哈,別當成實際應用了.....)

約束就假裝編輯好了,然后可以準備“逆”生成一個激勵文件了~

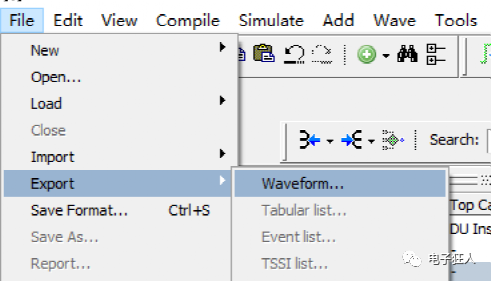

激勵文件生成

開始導出對應的文件

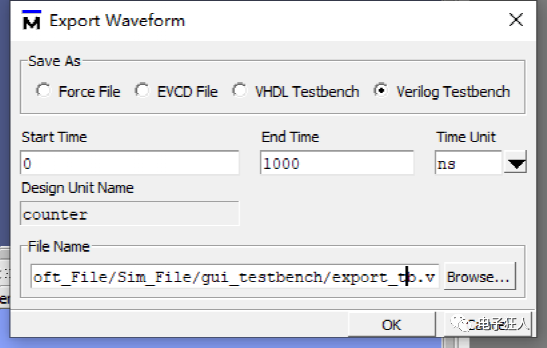

選擇Verilog形式的激勵文件(也搞個ECVD File),1000ns后結束激勵,選好存儲的路徑,文件名也設置好就可以OK

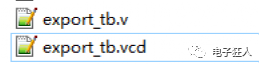

在對應的路徑就能有這兩個文件了

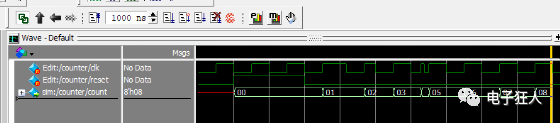

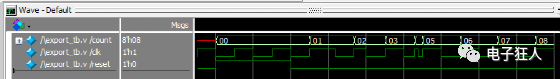

這時候再將Obejcets里的count變量添加到Wave窗口,并運行1000ns仿真,發現數據出來了~

退出仿真

Testbench測試

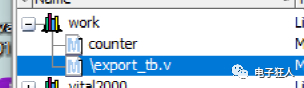

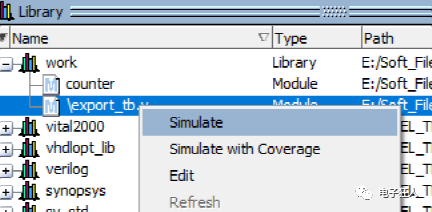

準備用剛剛導出的激勵文件來進行仿真測試,先把它編譯到工作庫里

vlog export_tb.v

然后運行仿真

把信號添加到Wave里作觀察,并運行1000ns的仿真

add wave *

run 1000ns

可以看到仿真按激勵進行~

退出仿真

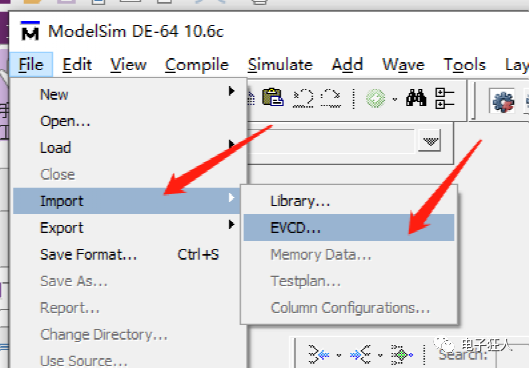

EVCD測試

接著演示下VCD文件的使用,直接啟動counter的仿真,然后先點下Wave界面,把這個EVCD的導入形式激活

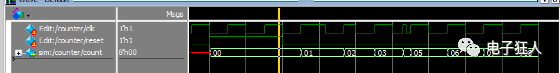

再把EVCD導進來,編輯的信號就又出來了,再把count的變量也加到Wave里,并運行1000ns

run 1000ns

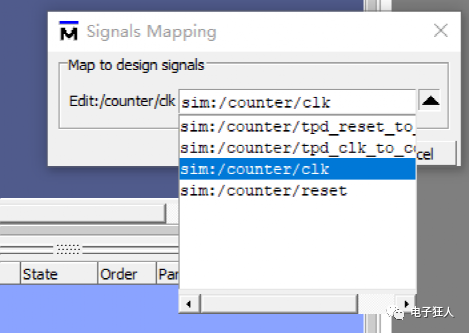

補個EVCD的使用,如果EVCD里的信號沒有和對應的代碼變量名對應起來,可以自己手動去把它進行映射,比如,clk

在窗口里選擇要映射的信號,OK后就映射好了

結束

這種可視化編輯,然后再產生出激勵文件的形式大概就這樣了,還不會咋寫激勵文件的可以這樣嘗試折騰折騰,說不定就突然很有“靈感”了。

原文標題:Modelsim的仿真之路(激勵文件“逆”生成)

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

-

仿真

+關注

關注

50文章

4070瀏覽量

133552 -

ModelSim

+關注

關注

5文章

174瀏覽量

47162 -

編譯

+關注

關注

0文章

657瀏覽量

32852

原文標題:Modelsim的仿真之路(激勵文件“逆”生成)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ISE 關聯 Modelsim 詳細操作

modelsim激勵程序怎么編寫

modelsim仿真詳細過程(功能仿真與時序仿真)

仿真軟件ModelSim及其應用,ModelSim的仿真流程

三態門原理HDL語言DSP和ARM總線的仿真及Modelsim使用教程資料

FPGA設計的全部流程詳細說明

基于ModelSim使用四ModelSim手動仿真教程

BOSHIDA DC電源模塊檢測穩定性能詳細流程

modelsim自動化仿真實驗 利用腳本實現modelsim自動化仿真

使用Modelsim編譯激勵文件的詳細流程

使用Modelsim編譯激勵文件的詳細流程

評論