ZYNQ從放棄到入門(一)MIO

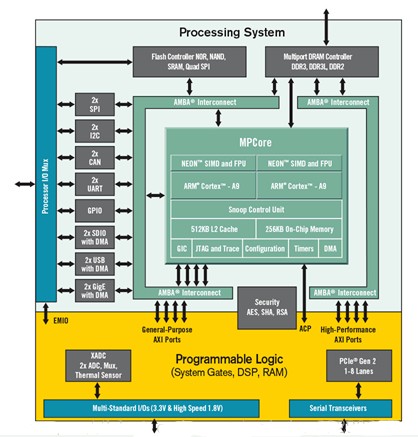

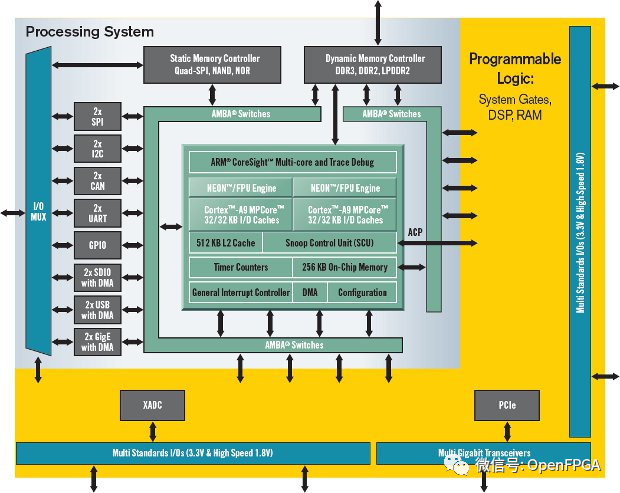

這篇博文特別關注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模塊。正是這個接口塊為 Zynq SoC 的雙核 ARM Cortex-A9 MPCore 處理器提供了許多標準接口。MIO 還包含確定 Zynq SoC 如何啟動的配置設置。MIO 連接到 Zynq SoC 的 PS(處理器系統)端。它連接到 Zynq 設備上的 54 個引腳(注意 CLG225 封裝中的 Zynq-7010 SoC 有 32 個 MIO 引腳),用于以下用途:

定義配置方法

四路 SPI 存儲器接口

SRAM/NOR閃存接口

NAND閃存接口

兩個 10/100/1000 以太網 MAC

兩個 USB 2.0 OTG 接口

兩個 SD 卡接口

兩個 UART

兩個主從 I2C 接口

兩個全雙工 SPI 接口

兩個 CAN 2.0B 接口

PJTAG 和 TRACE 調試接口

三重定時器/計數器 (TTC)

系統看門狗定時器

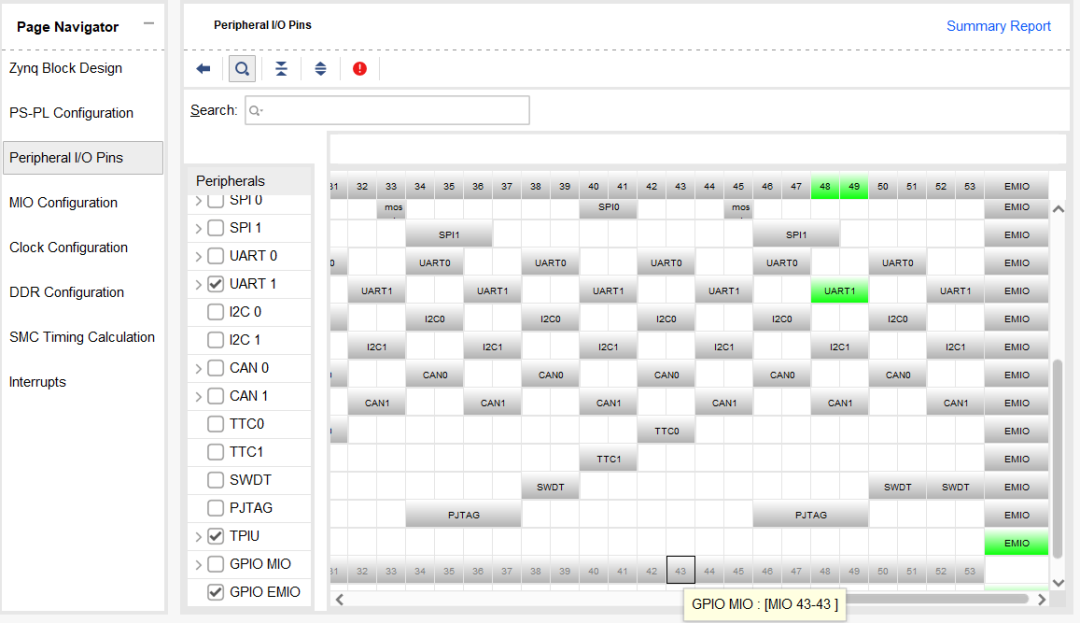

當然,有時會遇到需要用可用引腳數來權衡許多接口的情況。畢竟,工程學總是一門妥協的藝術。使用 Vivado 設計流程,可以通過雙擊框圖中的處理器來分配 MIO 中的功能,這會打開重新定制 IP 窗口。定義 MIO 有兩個選項。第一個選項——Peripheral I/O Pins——非常圖形化,讓您可以看到分配一個接口標準如何影響其他標準,如下圖所示:還可以使用此窗口為每個接口定義組電壓設置兩個 I/O bank(綠色 = 激活)。

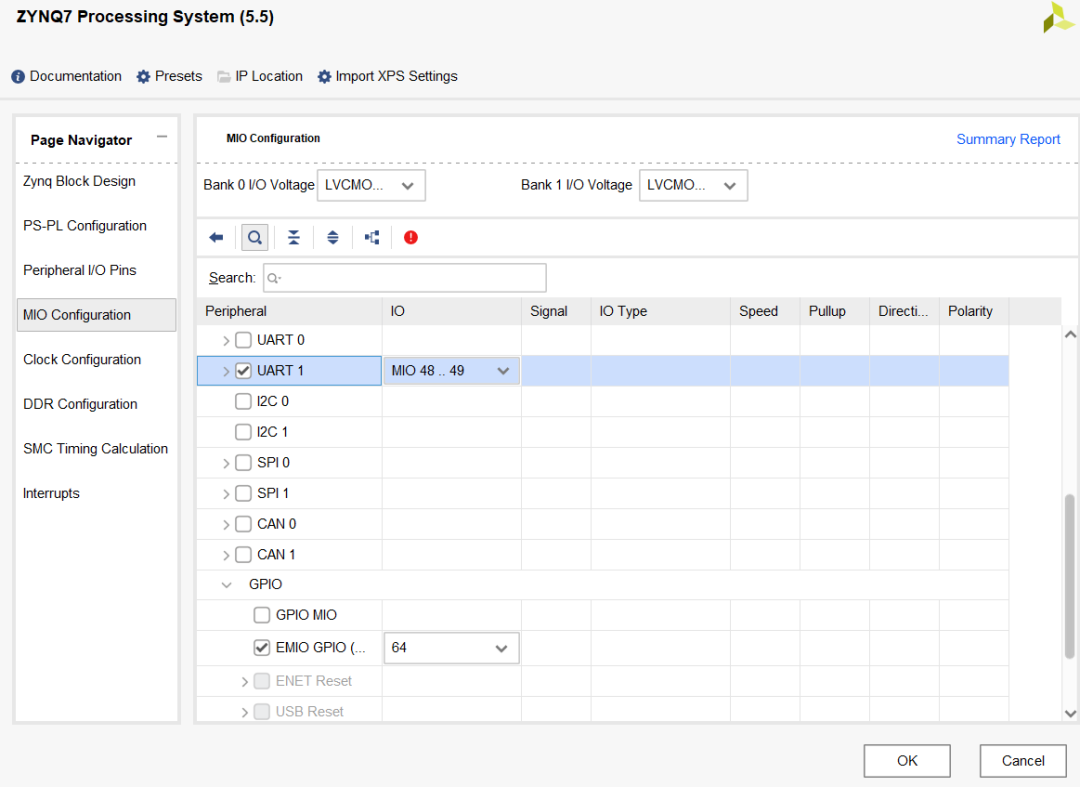

第二個選項是 Zynq 處理系統屏幕中的“MIO 配置”選項卡,如下所示,它會顯示分配給 MIO 的接口列表。我們還可以在此視圖中分配 EMIO 引腳,稍后我們將解決這個問題。MIO 分為兩個電壓組:

MIO0 引腳 0 到 15

MIO1 引腳 16 至 53

Bank 0 包括配置輸入引腳,在上電后對其進行采樣。這些模式引腳共享器件 PS 側的多用途 I/O 引腳。總共有七個模式引腳映射到 MIO[8:2]。前四個模式引腳定義啟動模式;第五個判斷是否使用PLL;第六和第七個模式引腳定義了上電期間 MIO bank 0 和 bank 1 上的 bank 電壓。在引導加載程序完成后,可以將 MIO bank 0 和 1 上定義的電壓標準從 LVCMOS 更改為 HTSL。

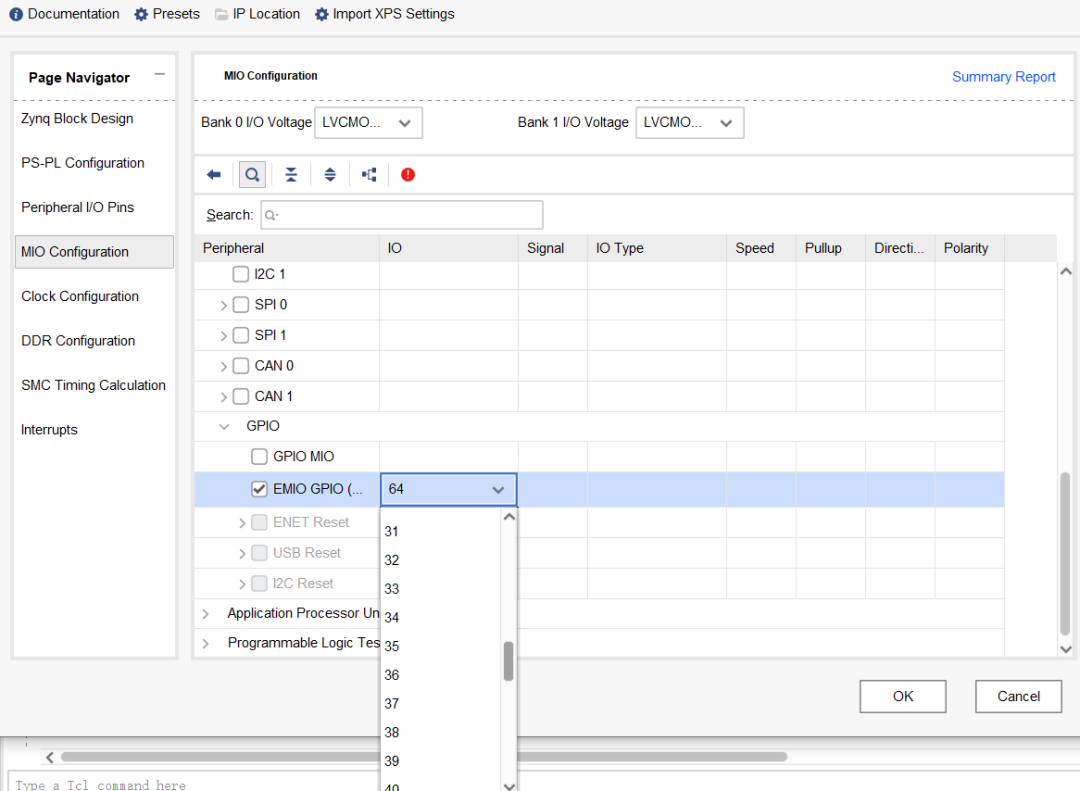

如上所述,有時沒有足夠的 MIO 引腳來顯示希望擁有的所有接口。在這種情況下,可以將 MIO 擴展到 Zynq SoC 的可編程邏輯 (PL) 端。這稱為擴展多用途 IO 或 EMIO(Extended Multipurpose IO )。EMIO 可以提供多達 64 個額外的 GPIO 引腳。或者,可以將大多數 MIO 接口分配給 EMIO,但 USB、SRAM/NOR 存儲器接口和 NAND 閃存接口除外。Zynq SoC 技術參考手冊提供了有關 MIO 和 EMIO 功能差異的非常詳細的信息。為 EMIO 分配功能非常簡單,只需單擊 Peripheral I/O Pins 選項卡末尾的 EMIO 按鈕即可完成,如下所示:

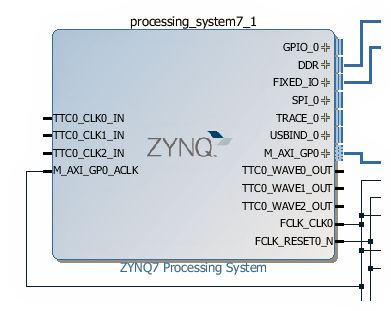

可以啟用 GPIO 設置并從 MIO 配置選項選項卡中選擇其大小。如果選擇了最大 64 位大小,則 GPIO 將分為兩組,每組 32 位。當關閉 re-customize IP 選項時,將看到您選擇的附加端口已添加到框圖中的 PS:上面的示例顯示了當 GPIO_0、SPI_0 TRACE_0 和 TTC_0 分配給 EMIO 時的 PS。然后可以將這些功能分配為外部 IO,并將出現在重新生成的 HDL 網表中。注意:因為 EMIO 位于 Zynq SoC 的 PL 側,所以不要忘記啟用 PS 和 PL 之間的電平轉換器以確保正確操作。

原文標題:ZYNQ從放棄到入門(一)MIO

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

接口

+關注

關注

33文章

8610瀏覽量

151220 -

封裝

+關注

關注

126文章

7914瀏覽量

142993 -

Zynq SoC

+關注

關注

0文章

6瀏覽量

3646

原文標題:ZYNQ從放棄到入門(一)MIO

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Zynq-7000 SoC提供 FPGA 資源

RTOS怎么添加到ZYNQ SoC設計中?

為什么人們使用Zynq SoC而不是其他類型的FPGA?

典型的ZYNQ SoC結構圖/系統框架

Xilinx Zynq-7000SOC的相關資料推薦

Xilinx客戶分享Zynq SoC設計成功經驗

運行于Zynq SoC上μITRON(操作系統)的繼任者:eT

將Zynq SoC上的兩個ARM Cortex

在Zynq SoC上實現雙核非對稱的多進程處理模式

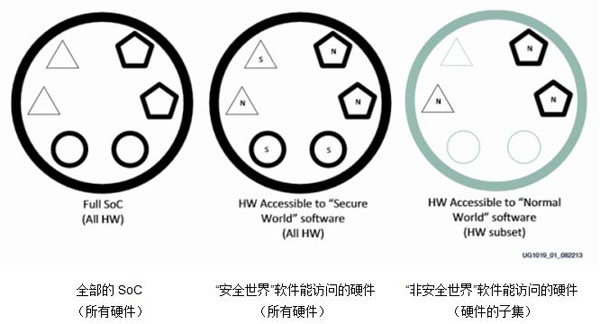

ARM TrustZone技術對Zynq SoC的作用

在ZYNQ上怎么加速CNN

Zynq SoC 設備上的多種用途

Zynq SoC 設備上的多種用途

評論