電容在PCB的EMC設計中,是使用最為廣泛的器件。按照功能的不同,電容可以分為三種:

去耦(Decouple):打破系統或電路的端口之間的耦合,以保證正常的操作。

旁路(Bypass):在瞬態能量產生的地方為其提供一個到地的低阻抗通路。是良好退耦的必備條件之一。

儲能(Bulk):儲能電容可以保證在負載快速變到最重時電壓不會下跌。

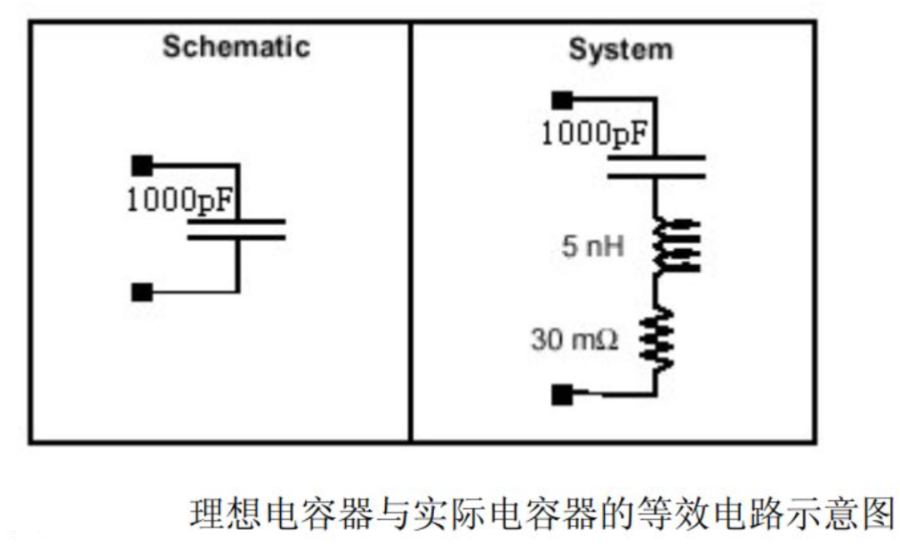

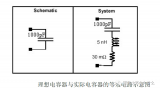

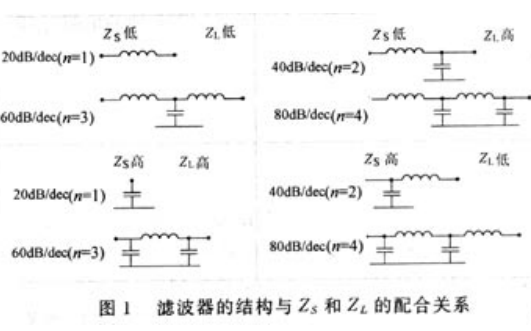

二、電容自諧振問題 我們用來濾波的電容器并不是理想的電容器,在系統中實際表現為理想電容與電感和電阻的串聯,如下圖所示:

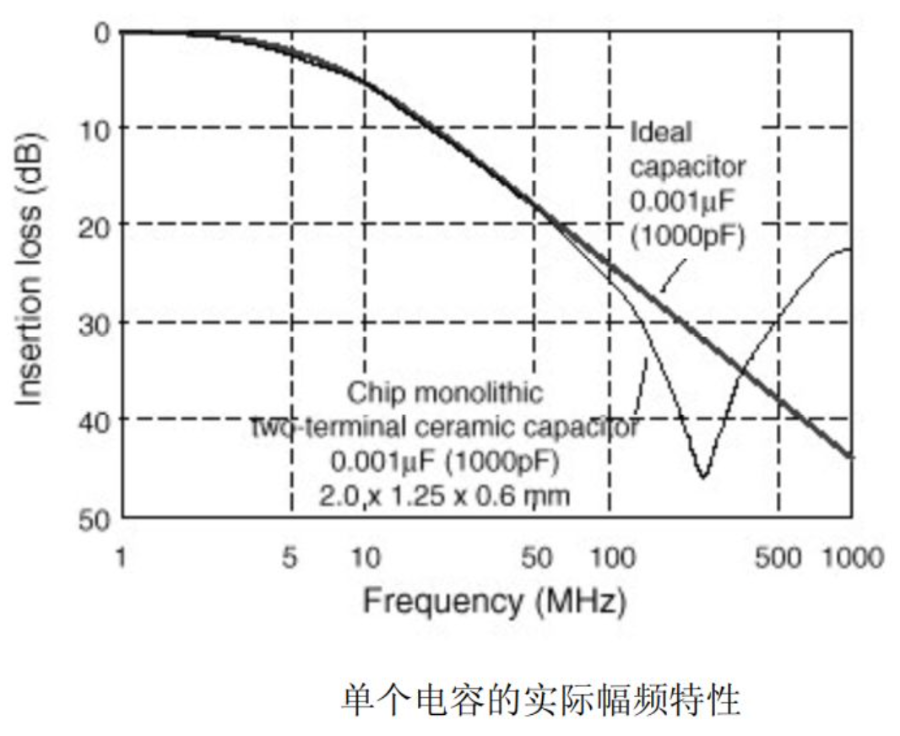

多層電容器(Muti-LayerCapacitor)在裝配到PCB板上時會產生將近5nH的寄生電感,再加上約30m歐的引線電阻,其頻率特性表現為如圖所示的曲線。濾波電容將不是理想的低通濾波器,實際的插入損耗特性表現為以自諧振點為中心的帶通濾波電路。

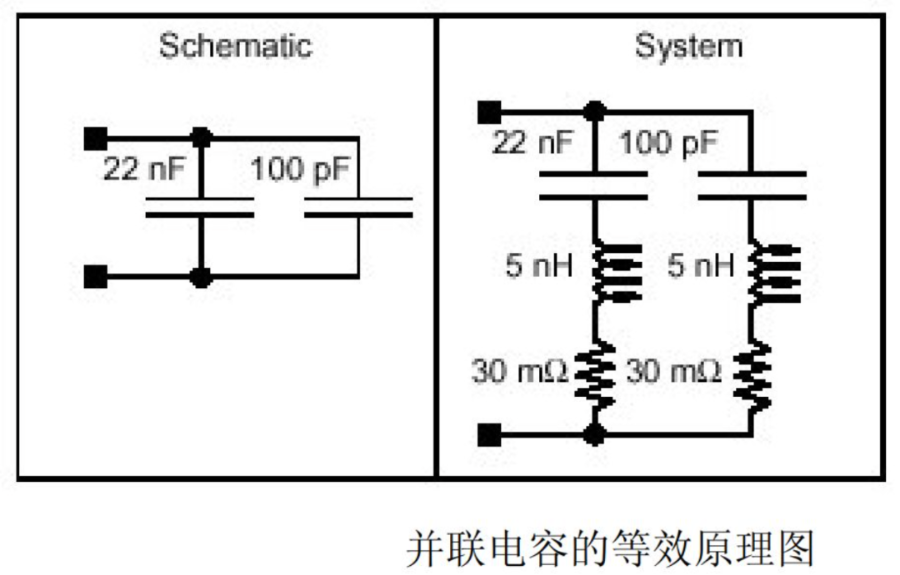

兩個電容串聯時,由于ESL(等效串聯電感)和ESR(等效串聯電阻)的存在,會產生反諧振問題。下圖給出了電容并聯的等效原理:

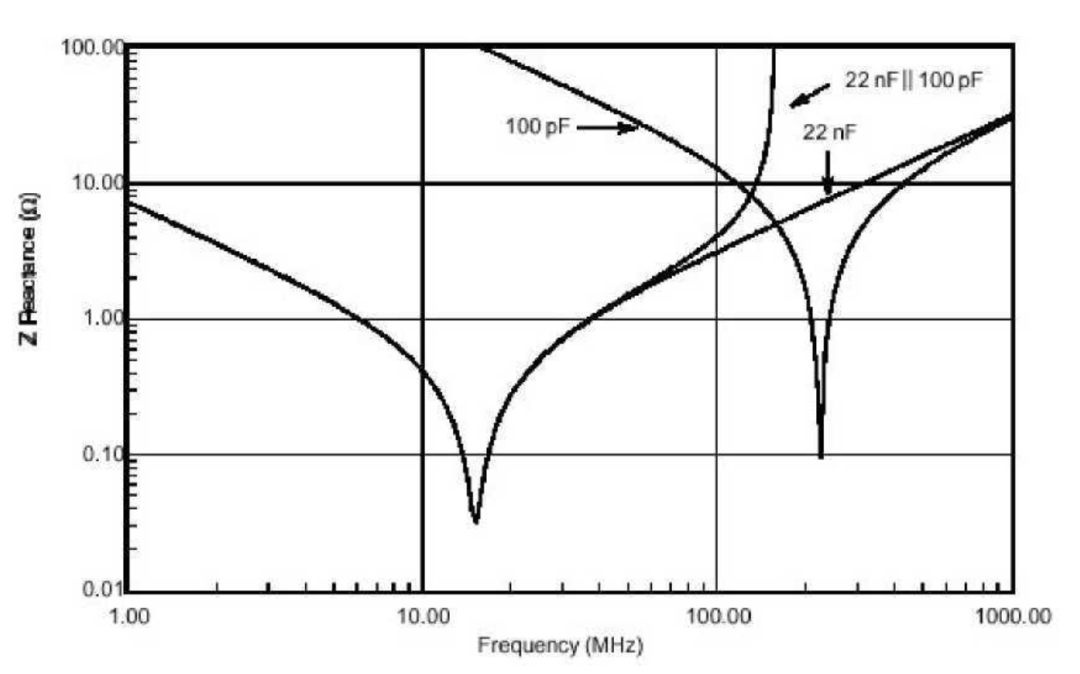

下圖給出了它們的真實的幅度-頻率特性:

在將近15MHz到175MHz的一個較寬的頻帶內,并聯電容的阻抗比單獨一個大電容的阻抗要來的大,由于兩電容產生了諧振,在150MHz處產生了一個阻抗的峰值,系統其他部分在該頻率范圍內產生的能量只能有很少的一部分被旁路到地平面。 三、ESR對并聯電容幅頻特性的影響 阻抗的峰值與電容器的ESR的值成反比,隨著單板設計水平與器件性能的提高,并聯電容的阻抗的峰值將會隨著ESR的減小而增加,并聯諧振峰值的形狀與位置取決于PCB板的設計與電容的選擇。有幾條原則應該了解:

隨著ESR的減小,諧振點的阻抗會減小,但反諧振點的阻抗會增大;

n個相同電容并聯使用時,最小陽抗口能小干ESRIn;

多個電容并聯時,阻抗并不一定發生在電容的諧振點;

對于給定數量的電容器,比較好的選擇是電容值在一個較大的范圍內均勻展開,各個電容值的ESR適中:比較差的選擇是僅有少量的電容值,而且電容的ESR都非常小。

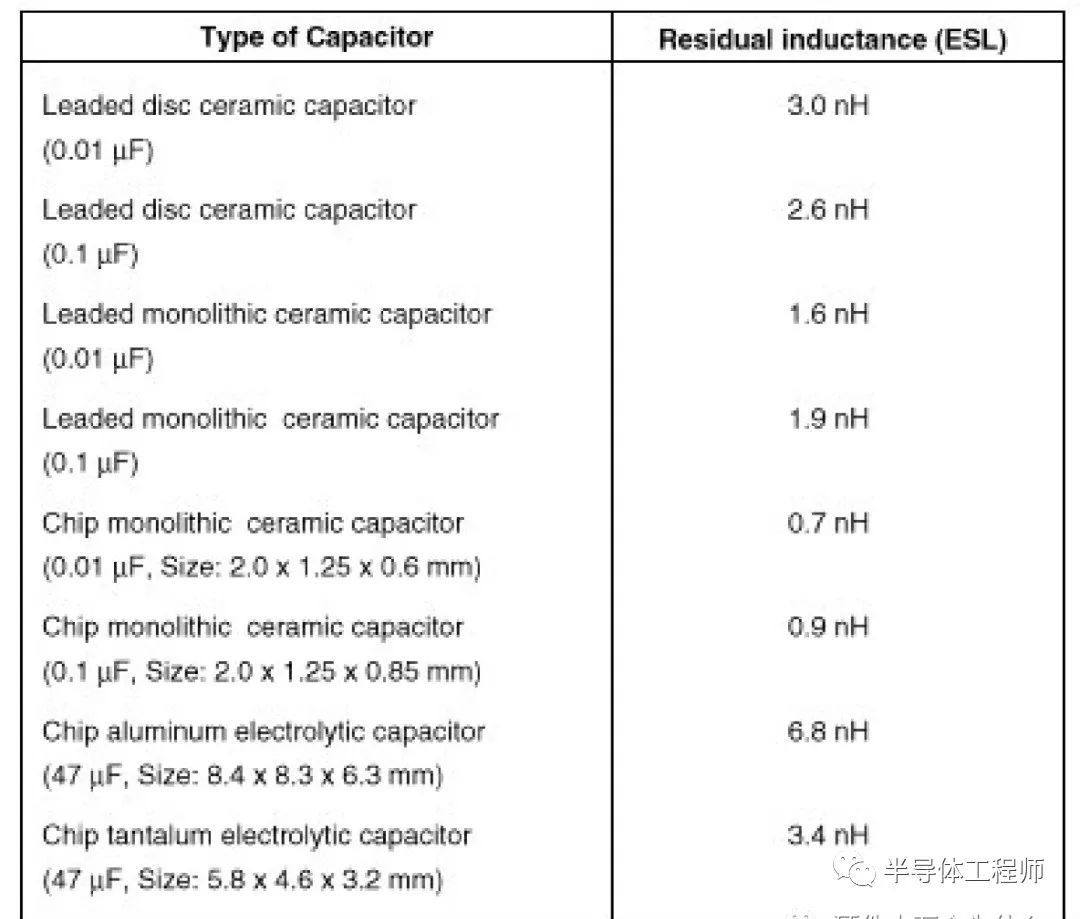

四、ESL對并聯電容幅頻特性的影響 電容封裝和結構不同,ESL也不同,幾種典型封裝電容的ESL如表所示:

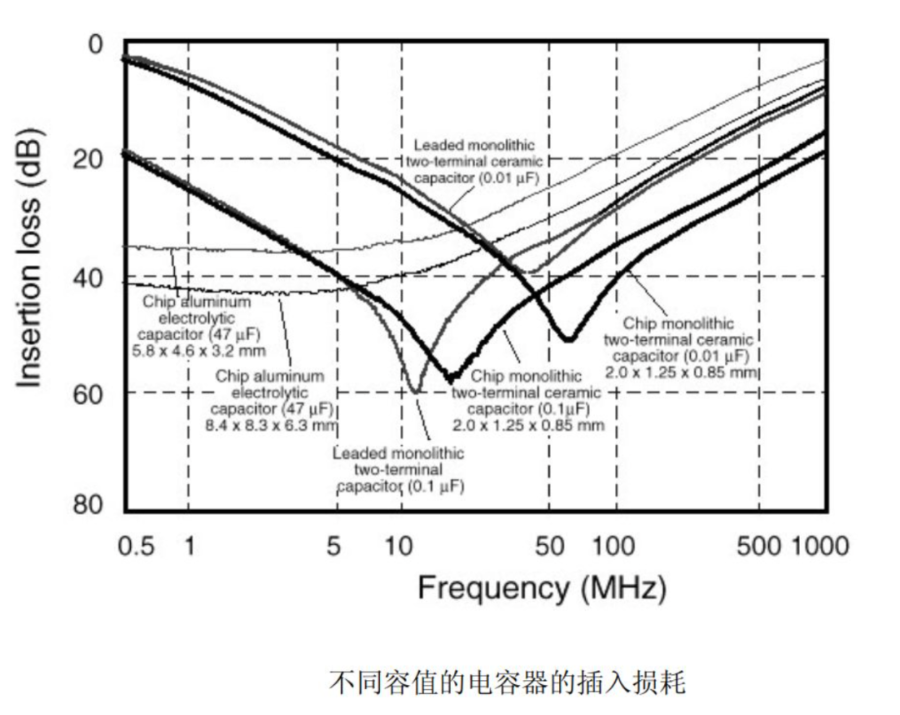

電容的ESL與電容值一起決定電容器的諧振點與并聯電容器的反諧振點的頻率范圍。在實際的設計中,應該盡量選用ESL小的電容器。 五、電容器的選擇 對于RF設計而言,陶瓷電容器、聚酯纖維電容器和聚苯乙烯薄膜電容器都是很好的選擇。 對于EMI濾波器來講,對電容器的介質材料要求并不高,常見的X7R、Y5V和Z5U等松散介質都是不錯的選擇:通常絕對的電容值、電容器的溫度系數、電壓變化系數等并不重要。不同種類、不同容值的電容濾波范圍是不同的,下面是典型的插入損耗比對效果:

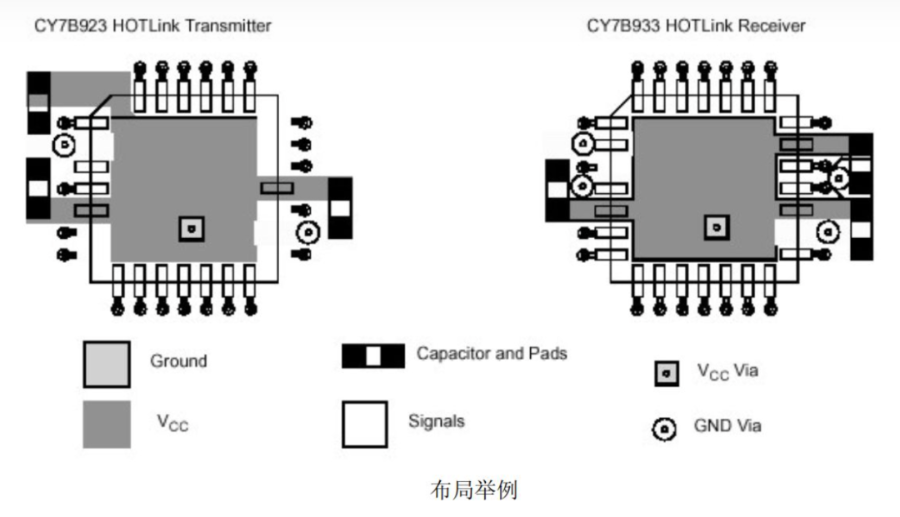

由上圖可以看出,同為0805封裝的貼片陶瓷電容,001UF的電容比0.1UF的電容具有更好的高頻濾波特性;建議板極工作頻率高于50MHZ的單板(如傳輸、MUSA的多數單板)全部使用0.01UF的濾波電容,而不是我們目前大量采用的0.1UF的濾波電容。 六、去耦電容與旁路電容的設計建議 1、以供應商提供的產品資料上的自諧振特性為基礎選擇電容,使之符合設計的時鐘速率與噪聲頻率的需要。 2、在所需要的頻率范圍內加盡可能多的電容。例如,22nF的電容的自諧振頻率將近為11MHz,有用的阻抗(Z1歐姆)范圍為6M~40MHz,你可以在該頻帶范圍內加盡可能多的電容,以達到需要退耦的水平。 3、在盡可能靠近IC每個電源管腳的地方,至少放一個去耦電容器,以減小寄生阻抗。 4、旁路電容與IC盡可能放在同一個PCB平面上。有一個需要特別注意的地方:在兩種布局中,Vcc網絡都只有一個點連到Vcc平面。這樣做可使IC內外的噪聲都必須通過這個唯一的過孔走到電源平面上去,過孔的附加阻抗幫助避免了噪聲向系統其余部分的擴散。

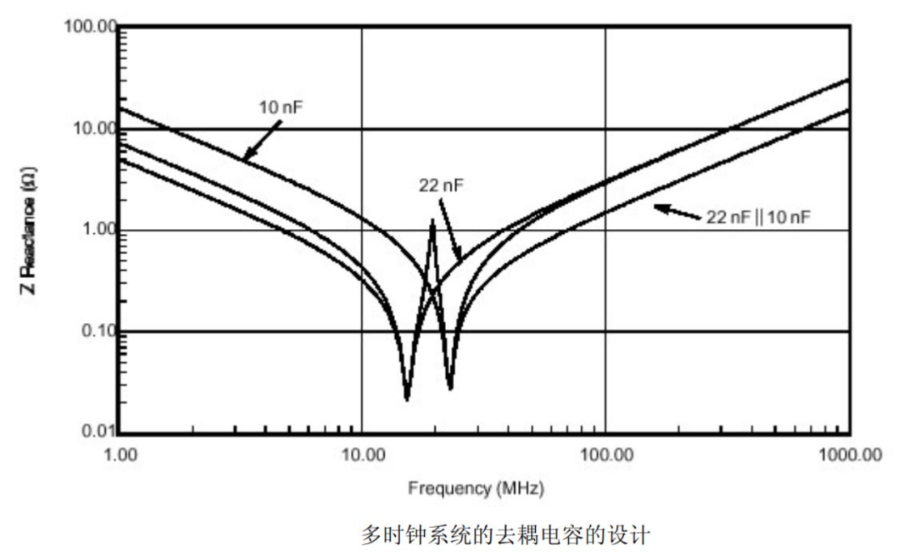

5、對于多時鐘系統可以將電源平面作圖3-14所示的分割,對每一個部分使用一種正確容值的電容器,被狹縫分隔的電源平面將一部分的噪聲與其他部分的敏感器件分隔開來,同時提供了中容值的分離。 6、對于時鐘頻率在一個較寬的范圍內變化的系統,旁路電容的選擇甚為困難。一個較好的解決方法是將兩個容值上接近2:1的電容并聯放置。 這樣做可以提供一個較寬的低阻抗區,和一個較寬的旁路頻率,下面這張圖可以看到,阻抗峰值仍然產生了,但卻小于15歐,而可用的頻率范圍(阻抗小于15歐)則擴展到將近3.25MHz到100MHz的范圍,這種多退耦電容的方法只在一個單獨的IC需要一個較寬的旁路頻率范圍而且單個電容無法達到這一頻帶時才使用。而且,容值必須保持2:1的范圍內,以避免阻抗峰值超過可用的范圍。

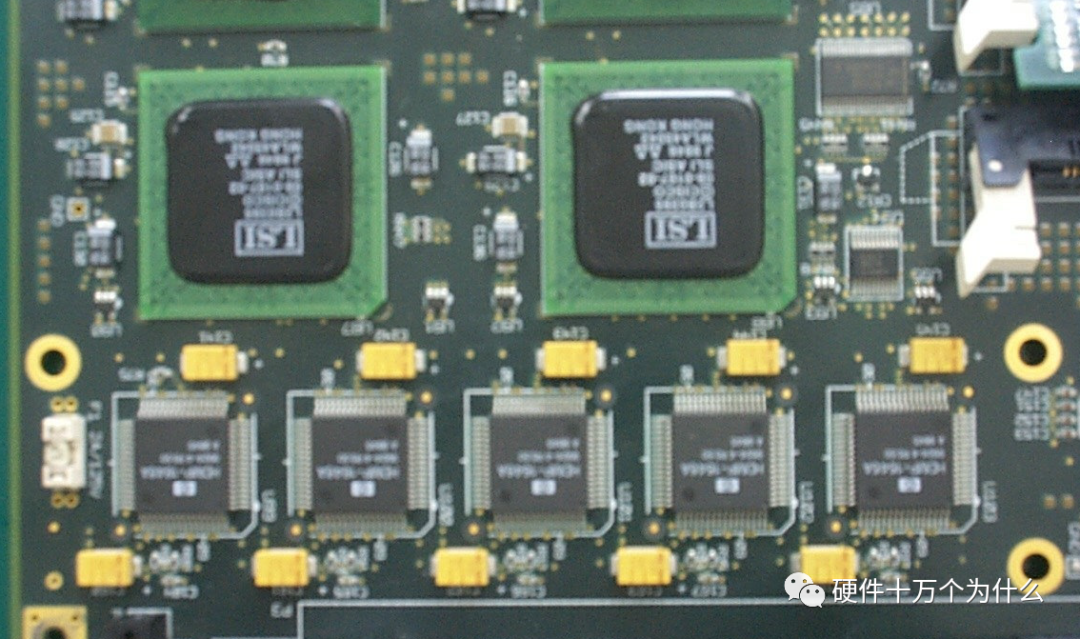

七、儲能電容的設計 儲能電容可以保證在負載快速變到最重時供電電壓不會下跌。儲能電容可分為板極儲能電容、器件級儲能電容兩種: 一是,板極儲能電容:保證負載快速變到最重時,單板各處供電電壓不會下跌。在高頻、高速單板(以及條件允許的背板),建議均勻排布一定數量的較大容值的鉭電容(luf、10uf、22uf、33uf),以保證單板同一電壓的值保持一致。 二是,器件級儲能電容:保證負載快速變到最重時,器件周圍各處供電電壓不會下跌。對于工作頻率、速率較高、功耗較大的器件,建議在其周圍排放1-4個較大容值的鉬電容(luf、10uf、22uf、33uf),以保證器件快速變換時其工作電壓保持不變。 儲能電容的設計應該與去耦電容的設計區別開來,有以下設計建議: 1、當單板上具有多種供電電壓時,對一種供電電壓儲能電容仍然只選用一種容值的電容器,一般選用表貼封裝的Tantalum電容(鉭電容),可以根據需要選擇10uf、22uf、33uf等。 2、不同供電電壓的芯片構成一個群落,儲能電容在這個群落內均勻分布,如下圖所示:

審核編輯 :李倩

-

濾波電容

+關注

關注

8文章

458瀏覽量

40086 -

emc

+關注

關注

170文章

3935瀏覽量

183380

原文標題:?干貨|詳解電容在EMC設計中的作用

文章出處:【微信號:電子工程世界,微信公眾號:電子工程世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

濾波電容在EMC中的功能

濾波電容在EMC中的功能

濾波電容在EMC中的功能

評論