一、AXI簡介

AXI——Advanced eXtensible Interface,直譯過來就是先進的可擴展接口,是由ARM公司提出的,是一種高性能、高帶寬、低延遲的片內總線。FPGA工程師會發現其大量運用于FPGA設計中,Vivado中的接口類IP全部都配有AXI接口,可見其重要性。AXI包括AXI、AXI-Lite(輕量級、簡化級)和AXI-Stream(Xilinx特有的高速數據流傳輸模式),其官方標準文檔我已經上傳,下載鏈接在這里,官方標準文檔不建議從頭看到尾,只需必要時查詢使用。

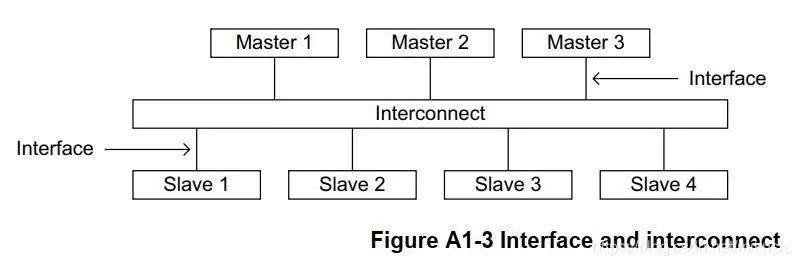

AXI是多Master和多Slave的拓撲結構,如下圖所示:

圖1 AXI的拓撲結構

中間的Interconnect是指的AXI交換設備。上圖需要特別注意的是,我們在設計過程中,有時同一個設備既可以作為Master,也可以作為Slave。

二、AXI總線的信號描述

AXI總線使用基于VALID/READY握手機制的數據傳輸協議,這是什么意思呢?就是無論是Master端,還是Slave端,要傳輸任何內容必須要確認對方給出了READY有效(不一定有效之后才傳輸,但是一定要等到有效,后面會有解釋),且無論傳輸給對方的是數據還是地址,是控制信號還是狀態信號,都要在VALID有效時進行傳輸。

1、AXI總線的通道和信號(AXI和AXI-Lite)

AXI總線一共分為6大通道,對于AXI和AXI-Lite,一般傳輸的信號線如下列出,對于AXI-Stream,后面單獨討論,對于猝發傳輸,會多幾根信號線,也放在后面單獨討論。

(1)讀地址通道,包含ARVALID, ARADDR, ARREADY信號。

(2)讀數據通道,包含RVALID, RDATA, RREADY, RRESP信號。

(3)寫地址通道,包含AWVALID,AWADDR, AWREADY信號。

(4)寫數據通道,包含WVALID, WDATA,WSTRB, WREADY信號。

(5)寫應答通道,包含BVALID, BRESP, BREADY信號。

(6)系統通道,包含ACLK,ARESETN信號。

可以看出,除了系統通道之外,每個通道都有VALID和READY。對于每個通道的信號名稱,可以得到這樣的一個規律:在前面加上一個字母R,表示讀通道,加上一個字母W,表示寫通道,加上一個字母B,表示應答通道(因為是VALID/READY機制,所以應答通道必然是寫應答,表示寫操作成功了,為什么沒有讀應答?讀者請自己思考。),對于讀通道和寫通道,再在前面加上一個字母A表示地址通道,如果不加就是數據通道。根據這樣的命名規律,大部分的信號線的意思就十分明白了,只有下面兩種信號線需要說明。

RESP——表示Slave發出響應(response),其中BRESP是從設備發出的寫響應,表示寫操作的狀態,RRESP是從設備發出的讀響應,表示讀操作的狀態,這兩個信號都是2位的,從00-11分別表示OKAY,EXOKAY,SLVERR,DECERR,一般情況下都是00,表示OKAY,就是說訪問成功。EXOKAY是單獨訪問(exclusive)成功的意思,單獨訪問是AXI總線的一種訪問模式,只允許一個Master對一個Slave進行訪問。SLVERR表示訪問錯誤,這時Master的地址和命令是已經給到了Slave了,但是Slave返回一個錯誤信息給Master。DECERR表示解碼(decode)錯誤,其實是地址解碼錯誤的意思,Master發出的訪問地址如果不能被識別,則會由中間的交換設備Interconnect返回DECERR給Master。

WSTRB——寫數據段有效,其每一位對應WDATA中的8位(1字節),用于標識對應字節是否有效,WSTRB的第0位為1表示WDATA的低8位有效,第1位為1表示WDATA的次低8位有效,以此類推。

AXI總線的R/WDATA的位寬可以選擇32、64、128和256,一般32和64就滿足于大部分設計了。當然,對于不同的數據位寬n,WSTRB的位寬是n/8。

2、AXI-Stream的信號和波形

可以不管這個小節直接跳到第三節。AXI4-Stream去掉了地址項,在這種模式下,其實就是簡單的從Master發送數據到Slave,中間不經過交換設備,我認為就相當于一般的帶著有效使能信號的大量數據傳輸,和AXI的理念相去甚遠。除時鐘和復位外,信號的命名規則以T開頭,如下所示。

(1)TREADY信號:Slave告訴Master做好傳輸準備。

(2)TDATA信號:傳輸數據,可選寬度32、64、128、256bit。

(3)TSTRB信號:每一bit對應TDATA的一個有效字節,寬度為TDATA/8。

(4)TLAST信號:Master告訴Slave傳輸數據的結尾。

(5)TVALID信號:Master輸出的傳輸有效使能。

(6)TUSER信號 :用戶定義信號,寬度為128bit,一般用來給傳輸計數。

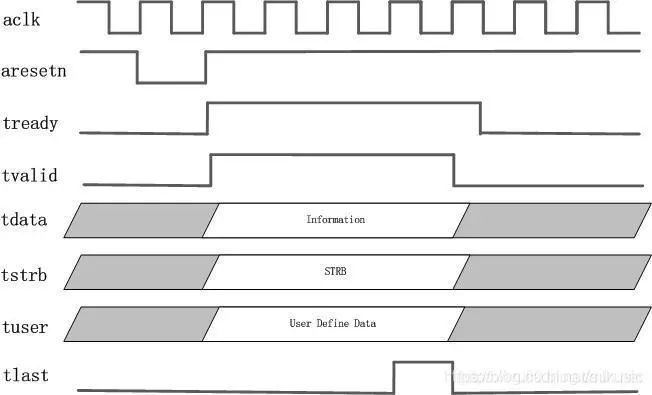

傳輸波形如下圖所示,我個人認為就像使用FIFO存取數據的那種波形,AXI-Stream的傳輸波形比AXI和AXI-Lite都簡單,后面不再討論這個模式。

圖2 AXI-Stream傳輸波形

三、AXI總線的數據傳輸過程

一般情況下,AXI-Lite用于配置寄存器和低速數據傳輸,AXI用于大量數據高速傳輸,所以AXI-Lite一般不支持猝發傳輸(也叫突發式傳輸,burst傳輸,即一次命令傳輸大量數據),所以下面分為猝發和非猝發來討論。

1、非猝發傳輸

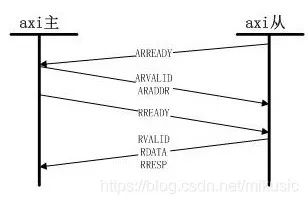

讀操作握手過程如下圖所示:

圖3 AXI讀操作握手過程

圖3是一個比較好理解的圖,但是實際的FPGA仿真波形中不是按這個圖的上下順序給出的信號,下面給出實際仿真的波形。

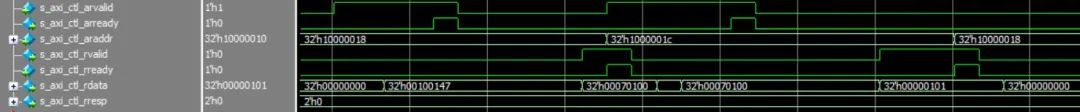

圖4 AXI讀操作實際波形

從上圖可以看出在FPGA內部,過程是這樣子的:

1、主設備有效ARVALID,這個時候必須保證ARADDR已經有效,表示主設備已經準備好地址,等待從設備響應。

2、從設備有效ARREADY,表示從設備已將接收地址和相關的控制信號鎖存,告訴主設備不需要再維持這個讀地址了,之后主設備可以把ARVALID拉低。

3、從設備有效RVALID,表示讀數據可用,這個時候必須保證讀數據RDATA已經有效,主設備監控該信號有效就可以讀取數據了。

4、這時由于RRESP為0也表示讀取數據正確,主設備則有效RREADY,表示主設備讀操作完成,從設備這時可以拉低RVALID了。

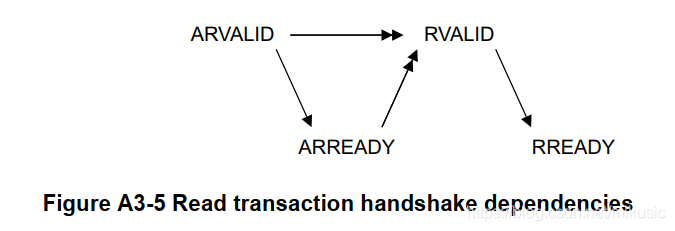

為什么握手過程圖和實際仿真波形會有差異?這時需要查閱標準文檔,在標準文檔中第三章有一個信號依賴關系圖可以說明這個問題。

圖5 AXI讀操作信號依賴關系

上圖中一個箭頭表示弱依賴關系,兩個箭頭表示強依賴關系。

從設備可以在ARVALID有效之后再給出ARREADY,也可以先給出ARREADY,再等待ARVALID有效。

從設備必須等待ARVALID和ARREADY都有效才能給出RVALID,并且同時開始給出數據傳輸。

主設備可以在RVALID有效之后再給出RREADY,也可以先給出RREADY,再等待RVALID有效。

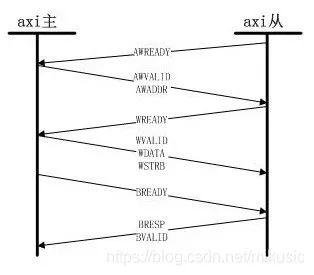

寫操作握手過程如下圖所示:

圖6 AXI寫操作握手過程

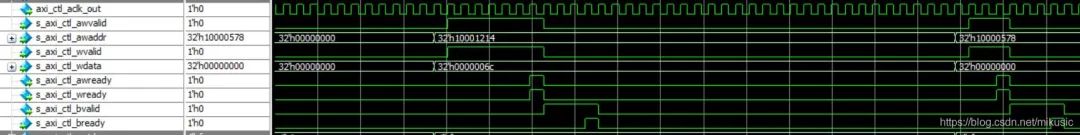

同樣的,實際的寫操作的波形和這個過程圖是有差異的。

圖7 AXI寫操作實際波形

這個過程的描述如下:

1、主設備有效AWVALID和WVALID,這個時候主設備的AWADDR和WDATA必須確保也已經有效,這兩個信號不一定同時有效,但我根據經驗發現一般情況下都表現為同時有效。表示主設備已經把地址和數據準備好了,等待從設備的AWREADY和WREADY。

2、從設備有效AWREADY和WREADY,這兩個信號不一定同時有效。表示從設備已經準備好接收地址和數據,同時告訴主設備可以拉低AWVALID和WVALID了。

3、從設備有效BVALID,表示從設備已經完成了在指定地址接收數據的操作。這個信號雖然大多數情況下會先于BREADY拉高,但是允許其在BREADY之后拉高,也就是說BVALID和BREADY嚴格意義上講并沒有先后順序,誰先完成誰先有效,并且拉高時和拉高之后就監控對方是否已經也拉高了,如果對方拉高,則己方在下一個時鐘節拍拉低。

4、主設備有效BREADY,表示主設備已經完成了其余工作,此時可以接收來自從設備的BVALID,由于大多數情況下BVALID已經拉高,此時主設備拉高這個信號也是為了告訴從設備可以拉低BVALID了。

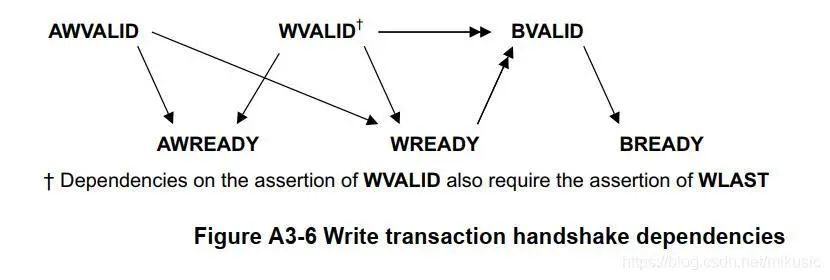

和讀操作類似,寫操作的信號依賴關系圖如下。

圖8 AXI寫操作信號依賴關系

主設備不一定得等待AWREADY或WREADY有效后再給出AWVALID或WVLAID。

從設備可以等待AWVALID或WVALID有效或者兩個都有效之后再給出AWREADY,也可以不用等待這兩個信號有效就給出AWREADY。

從設備可以等待AWVALID或WVALID有效或者兩個都有效之后再給出WREADY,也可以不用等待這兩個信號有效就給出WREADY。

從設備必須等待WVALID和WREADY都有效之后,才能給出BVALID,這里需要注意的是對于猝發傳輸,從設備除了要等待前面兩個信號有效之外還要等待WLAST有效之后才能給出BVALID。

主設備可以等待BVALID有效之后再給出BREADY,也可以不用等待BVALID有效直接給出BREADY。

信號依賴關系是不是有點暈,其實不用記這么多,在使用過程中看實際波形就可以了。

2、猝發傳輸(Burst傳輸)

AXI總線的最大特點就是其猝發傳輸(一次命令多個數據的傳輸形式),猝發傳輸時比上面的情況多了幾根信號線,猝發傳輸的起始地址最好以4KB對齊。猝發傳輸的過程以事務為單位,分為讀命令事務、寫命令事務、讀數據事務、寫數據事務、寫應答事務,分別對應上面的5個通道。以下是我個人的理解:AXI總線的這種將總線操作分解為事務的特點和PCI、PCIE相類似,分解成事務之后,所謂的"總線"這個概念其實就是某種“協議”,所謂的總線的管理過程就是事務的轉發過程,其實沒有什么看得見摸得著的“總線”,本質就是滿足特定協議的一堆接口以及中間的交換設備,這是所有高速總線的一大特點。下面兩圖大概說明了猝發傳輸的過程。

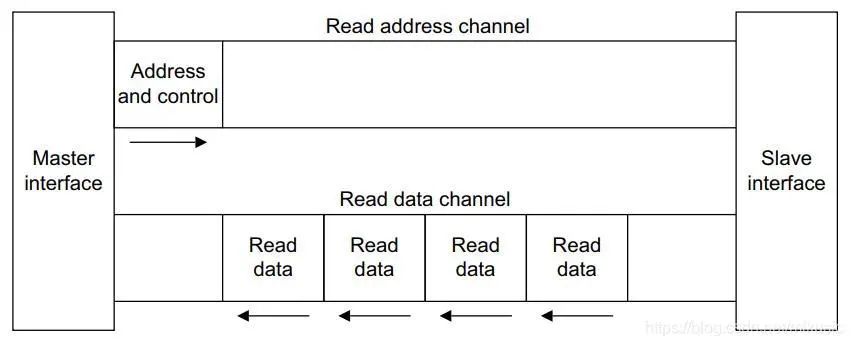

圖9 AXI讀猝發

圖10 AXI寫猝發

從上面兩圖,套用事務的概念,可以看出,對于讀操作的過程,事務的順序就是讀命令事務—>讀數據事務,對于寫操作的過程,事務的順序就是寫命令事務—>寫數據事務—>寫應答事務。

除了第二節中的6個通道包含的信號線以外的AXI信號線如下。

讀/寫地址通道:

猝發傳輸相關的信號線:

ARLEN/AWLEN:猝發傳輸的長度。此長度決定本次猝發傳輸的數據的個數,每個數據的大小以下面的SIZE決定,為0表示傳輸1個數據,為1表示傳輸2個數據,以此類推。

ARSIZE/AWSIZE:猝發傳輸的大小,為0表示取低8位,即數據大小為1byte,為1表示取低16位,即數據大小為2byte,以此類推,這個數值不能超過總線位寬所決定的最大byte數。

ARBURST/AWBURST:猝發傳輸的類型(注1)。

其他不常用的信號線:

ARLOCK/AWLOCK:鎖類型。原子操作相關(注2),初學者不用考慮,一般為0。

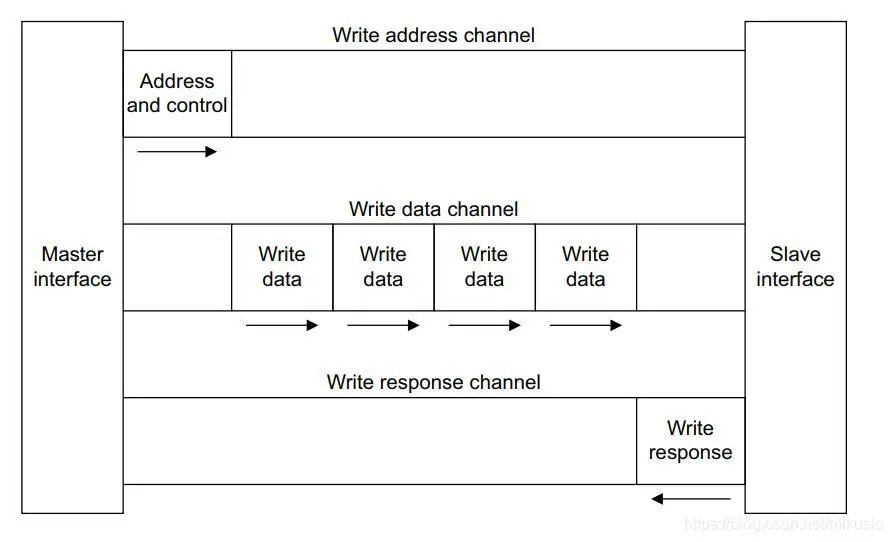

ARCACHE/AWCACHE:用于描述存儲類型。AXI總線支持訪問多種類型的存儲設備,一般不用考慮,由IP核自動填寫,存儲器類型見圖11。

ARPROT/AWPROT:保護類型,指明訪問優先級、是否采用安全訪問等信息,初學者不用考慮,一般為0。

讀/寫數據通道:

RLAST/WLAST:指示猝發傳輸的最后一個數據,不一定是一個節拍,但是一定是在本次需要傳輸的最后一個數據有效時才有效,如果其從有效變到無效,說明本次傳輸已經完成。

讀/寫/地址/數據/應答通道的ID信號線:

ARID/AWID:地址ID,交換設備轉發事務的標記。

WID/RID/BID:與前面的ARID/AWID保持一致。

圖11 AXI存儲類型指示信號的含義

注1:

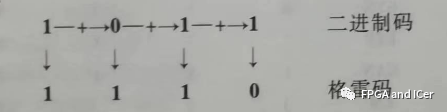

AXI協議用ARBURST/AWBURST[1:0]信號線定義了三種猝發傳輸的類型:固定式(FIXED,00)、遞增式(INCR,01)、回卷式(WRAP,10)。

(1)固定式是指地址是固定的,每一次傳輸的地址都不變。這樣的猝發傳輸是重復地對一個固定的位置進行存取,例如FIFO。

(2)遞增式是指每一次讀寫的地址都比上一次的地址增加一個固定的值,就是通常的順序存儲器,這是最常見的猝發傳輸形式。

(3)回卷式跟遞增式類似,當地址遞增到邊界時,自動返回到起始地址(起始地址必須按ARSIZE/AWSIZE對齊,猝發長度只能是2、4、8、16)。

注2:

原子操作是不可分割的,在執行完畢之前不會被任何其它任務或事件中斷。一般在單處理系統中的單條指令中可完成的操作都認為是原子操作。

AXI是一個比較復雜的協議,猝發傳輸時不一定是一次完成之后再進行下一次,經常會出現重疊式猝發,即同時給出兩次以上的命令事務,之后才進行數據事務,或者第一次數據事務還沒有完成就給出第二次的命令事務。此外還有窄帶傳輸和不對齊傳輸,我就不講了,新手只需掌握非猝發時的AXI握手規則,看懂仿真波形就可以了。在FPGA設計中,對于復雜程度比較高的協議我們通常是利用官方IP核,AXI的猝發傳輸只需大概看懂波形就可以了,有興趣可以深究,對于學習其他高速接口很有幫助。

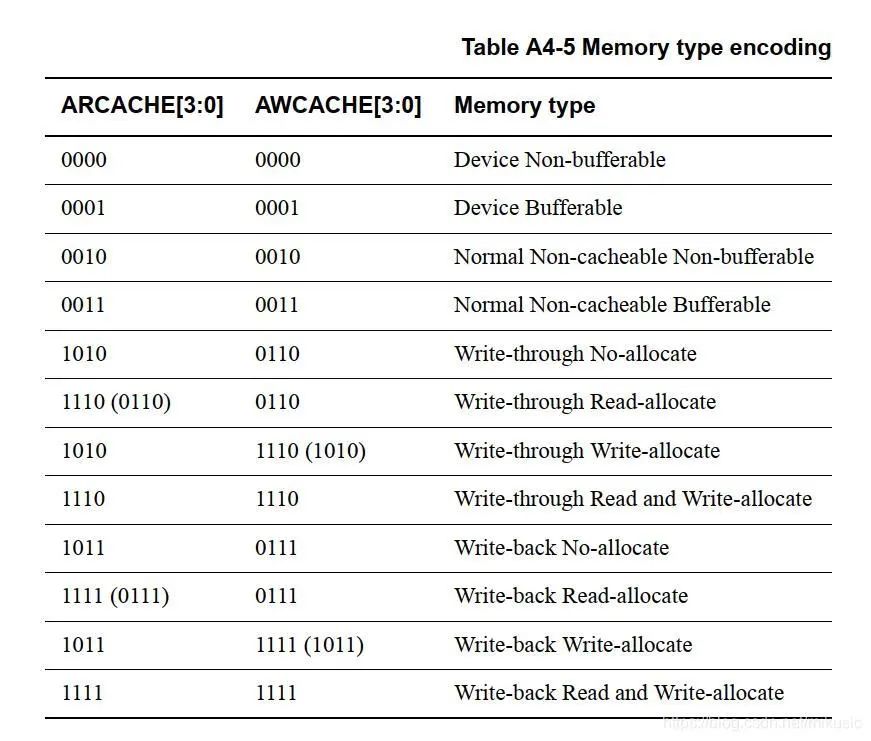

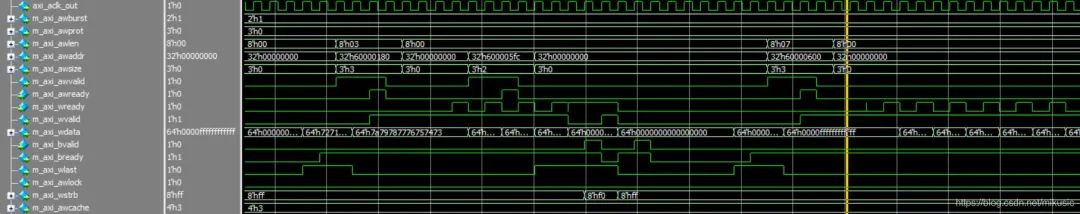

下圖是我截取的一段AXI重疊式猝發寫的波形圖供大家參考,圖中Master連續給了兩次寫命令事務。

圖12 AXI的burst寫操作的波形

審核編輯 :李倩

-

總線

+關注

關注

10文章

2891瀏覽量

88176 -

AXI

+關注

關注

1文章

128瀏覽量

16652

原文標題:FPGA學習-AXI總線知識點快速學習

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

單片機學習知識點全攻略(完結篇)

AXI總線知識點快速學習

AXI總線知識點快速學習

評論