ATE(Automatic Test Equipment)測試機在半導體領域是指檢驗IC(集成電路)功能完整性的設備,隨著工藝制程逐漸精進,單位芯片面積內容納的晶體管數量也與日俱增,芯片復雜度及集成度指數級增長,芯片測試在設計、開發、制造和封裝環節的重要性更加凸顯,尤其是在芯片設計和開發階段,高可靠性測試能夠極大地規避流片失敗對企業人力和物力造成的巨大創傷。

作為全球著名的ATE測試機供應商,泰瑞達(Teradyne)的半導體測試產品專用于滿足獨立集成電路、片上系統和系統級封裝設備開發人員和制造商的需求,領域涉及汽車、工業、通信、消費者、智能手機、計算機和電子游戲應用等。

近日,電子發燒友記者和泰瑞達中國區銷售副總經理黃飛鴻圍繞泰瑞達Ultra FLEX plus SoC 設備測試平臺以及ATE測試機后續發展趨勢進行了深入交流,在摩爾定律持續精進的情況下,ATE測試機又會迎來哪些顯著的變化。

根據SEMI發布的統計數據,2020年全球半導體設備市場規模達711.9億美元,同比增長19.15%。其中,半導體測試設備市場規模達60.1億美元,同比增長19.72%。按照SEMI的預測數據,2022年全球半導體測試設備市場規模預計將超過80億美元。從2020年的統計情況來看,在測試機、分選機和探針臺三類測試設備中,測試機仍占據較大份額,占比達到63.1%。

黃飛鴻表示,“2020年之后芯片代工制程已經進入5nm,未來將持續進入3nm、2nm,給ATE測試機帶來很大的挑戰,芯片內晶體管數量的增長速度超過本身可測試設計的技術。同時,芯片的生命周期越來越短,消費類芯片的迭代周期已經縮短至1年,甚至是AI芯片和AP高復雜度芯片也開始逐年迭代。這些都是復雜性因素,因此我們將這個時代定義為復雜性時代。”

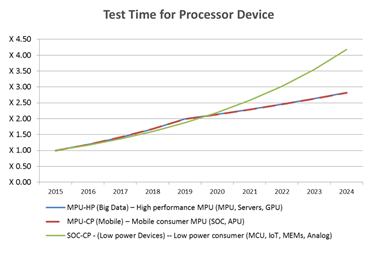

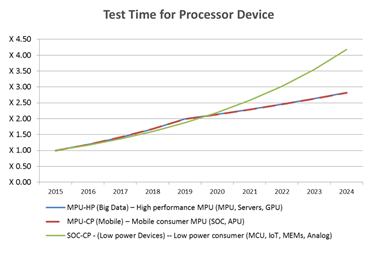

復雜性時代第一個顯著變化是測試時間的增長,根據黃飛鴻的描述,如下圖2所示,藍色線條是大數字芯片,能夠看出當前的測試時間相較于2015年已經增長了2.5倍,后續可能達到3倍以上的測試時間。

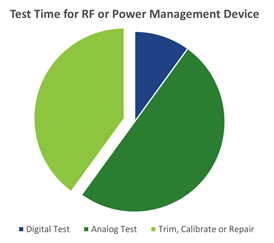

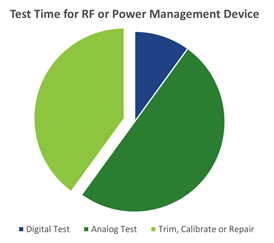

而從圖3能夠看出,以前在模擬和射頻芯片里面,測試時間所占比重很大的是模擬測試,而現在隨著工藝越來越先進,Trim測試這項額外多出來的測試所占的時間比重越來越高。

復雜性時代第二個顯著的挑戰是每顆芯片的裸片尺寸是不斷增加的,與之相對應的裸片失效的概率也在增加,導致每一片晶圓第一次量產的良率都不高,部分芯片的初次良率已經跌破10%。因此,隨著晶體管數量的增加,滿足最低質量標準所需的故障覆蓋率也成為了一個巨大的挑戰。與此同時,各行業對芯片的要求卻越來越高。

黃飛鴻特別強調,復雜性時代對測試機的要求是,測試一定要測的準,為管理測試成本,面對測試時間增加,測試單元必須更效率。

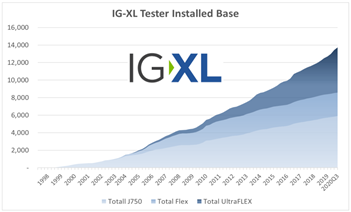

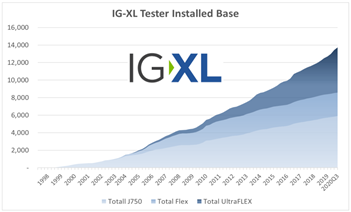

為了幫助AI 和 5G 網絡等行業提升測試效率,泰瑞達基于UltraFLEX和IG-XL平臺方案的成功經驗推出了UltraFLEX plus。根據黃飛鴻的介紹,目前UltraFLEX在全球已經有接近6000套的裝機量,而IG-XL平臺方案在截止到2020年Q3的統計數據顯示已經裝機接近1.4萬套,泰瑞達培養了超過1萬名IG-XL程序開發人員,該代碼庫已部署在全球超過 92% 的 IC 制造商中,過去6年之中,每年全球芯片行業評比中,IG-XL連續六年被評為使用率NO.1的軟件。基于統一的軟件平臺,UltraFLEX plus能夠與UltraFLEX無縫兼容,可以極大地提升測試工程師的測試效率。

在談到產品優勢時黃飛鴻講到,UltraFLEX plus能夠將IC量產所需的測試單元數量減少了 15%-50%,進而提高生產效率。對于設計公司而言,意味著更短的時間內能夠測出更多的芯片;對于下游工廠來說,可能只需要買一臺設備產出率便等同于原來1.5臺設備。

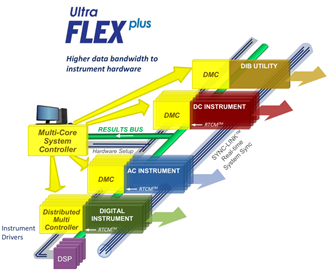

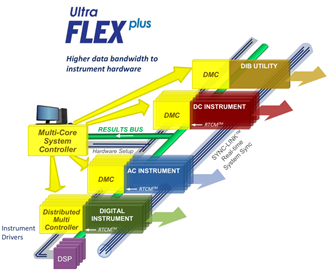

能夠做到如此顯著的測試效率提升主要源自UltraFLEX plus上的三大創新。

首先,UltraFLEX plus引入了創新的PACE運行架構,以最小的工程量創造出最高的測試單元產能,如下圖5所示,PACE是并發先進指令集架構,每個板卡上面都有自己的CPU可以獨立運算,得益于分布式多控制器 (DMC) 計算架構,以及板卡硬件數據帶寬的提高,使得測試效率顯著提升。

其次,UltraFLEX Plus有Q6到Q12到Q24三種不同的機臺配置,并采用全新一代數字板卡,包括下一代數字板卡UltraPin2200,新一代用于核心電源供電的板卡UVS64,高密度、高靈活性的通用電源板卡UVS256-HP以及下一代高密度模擬板卡UltraPAC300等。其中,Q24最多可以容納12288個數字通道,滿足市面上幾乎所有的需求,更大的測試頭能夠打造更多測試工位,且可以降低測試臺的PCB層數,明顯改善電源完整性或者信號完整性等關鍵性能,擁有更好的測試經濟性和測試效率。

第三,UltraFLEX Plus上面的Broadside應用接口簡化了DIB路由,并改善工位間結果一致性,從而加快上市時間。與傳統的ATE相比,Broadside DIB結構,將板卡較原先結構旋轉了90度,因此板卡的資源,能夠向芯片區域并行傳送。這意味著每個工位,都能夠獲得與之匹配的信號傳輸路徑。通過簡化原本復雜的 DIB布局,實現更快的上市時間、更多的工位數和更高的PCB良率。

面向未來,黃飛鴻表示,今年4nm已經逐漸開始放量,未來馬上會引來3nm和2nm,對測試設備提出的要求有兩項:其一,更高的數據率下面如何保證采樣的精度;其二,單芯片集成的晶體管密度指數級增長,掃描量可能超過1G,對單通道下面能存儲的向量深度提出了更高要求。UltraFLEX plus的掃描量深度最大可以容納19.2G,目前來看能夠滿足3nm和2nm需求。

作為全球著名的ATE測試機供應商,泰瑞達(Teradyne)的半導體測試產品專用于滿足獨立集成電路、片上系統和系統級封裝設備開發人員和制造商的需求,領域涉及汽車、工業、通信、消費者、智能手機、計算機和電子游戲應用等。

近日,電子發燒友記者和泰瑞達中國區銷售副總經理黃飛鴻圍繞泰瑞達Ultra FLEX plus SoC 設備測試平臺以及ATE測試機后續發展趨勢進行了深入交流,在摩爾定律持續精進的情況下,ATE測試機又會迎來哪些顯著的變化。

圖1:泰瑞達中國區銷售副總經理黃飛鴻

根據SEMI發布的統計數據,2020年全球半導體設備市場規模達711.9億美元,同比增長19.15%。其中,半導體測試設備市場規模達60.1億美元,同比增長19.72%。按照SEMI的預測數據,2022年全球半導體測試設備市場規模預計將超過80億美元。從2020年的統計情況來看,在測試機、分選機和探針臺三類測試設備中,測試機仍占據較大份額,占比達到63.1%。

黃飛鴻表示,“2020年之后芯片代工制程已經進入5nm,未來將持續進入3nm、2nm,給ATE測試機帶來很大的挑戰,芯片內晶體管數量的增長速度超過本身可測試設計的技術。同時,芯片的生命周期越來越短,消費類芯片的迭代周期已經縮短至1年,甚至是AI芯片和AP高復雜度芯片也開始逐年迭代。這些都是復雜性因素,因此我們將這個時代定義為復雜性時代。”

復雜性時代第一個顯著變化是測試時間的增長,根據黃飛鴻的描述,如下圖2所示,藍色線條是大數字芯片,能夠看出當前的測試時間相較于2015年已經增長了2.5倍,后續可能達到3倍以上的測試時間。

圖2:測試時間變化趨勢

而從圖3能夠看出,以前在模擬和射頻芯片里面,測試時間所占比重很大的是模擬測試,而現在隨著工藝越來越先進,Trim測試這項額外多出來的測試所占的時間比重越來越高。

圖3:模擬和射頻芯片測試時間情況

復雜性時代第二個顯著的挑戰是每顆芯片的裸片尺寸是不斷增加的,與之相對應的裸片失效的概率也在增加,導致每一片晶圓第一次量產的良率都不高,部分芯片的初次良率已經跌破10%。因此,隨著晶體管數量的增加,滿足最低質量標準所需的故障覆蓋率也成為了一個巨大的挑戰。與此同時,各行業對芯片的要求卻越來越高。

黃飛鴻特別強調,復雜性時代對測試機的要求是,測試一定要測的準,為管理測試成本,面對測試時間增加,測試單元必須更效率。

為了幫助AI 和 5G 網絡等行業提升測試效率,泰瑞達基于UltraFLEX和IG-XL平臺方案的成功經驗推出了UltraFLEX plus。根據黃飛鴻的介紹,目前UltraFLEX在全球已經有接近6000套的裝機量,而IG-XL平臺方案在截止到2020年Q3的統計數據顯示已經裝機接近1.4萬套,泰瑞達培養了超過1萬名IG-XL程序開發人員,該代碼庫已部署在全球超過 92% 的 IC 制造商中,過去6年之中,每年全球芯片行業評比中,IG-XL連續六年被評為使用率NO.1的軟件。基于統一的軟件平臺,UltraFLEX plus能夠與UltraFLEX無縫兼容,可以極大地提升測試工程師的測試效率。

圖4:IG-XL軟件裝機量

在談到產品優勢時黃飛鴻講到,UltraFLEX plus能夠將IC量產所需的測試單元數量減少了 15%-50%,進而提高生產效率。對于設計公司而言,意味著更短的時間內能夠測出更多的芯片;對于下游工廠來說,可能只需要買一臺設備產出率便等同于原來1.5臺設備。

能夠做到如此顯著的測試效率提升主要源自UltraFLEX plus上的三大創新。

首先,UltraFLEX plus引入了創新的PACE運行架構,以最小的工程量創造出最高的測試單元產能,如下圖5所示,PACE是并發先進指令集架構,每個板卡上面都有自己的CPU可以獨立運算,得益于分布式多控制器 (DMC) 計算架構,以及板卡硬件數據帶寬的提高,使得測試效率顯著提升。

圖5:PACE運行架構

其次,UltraFLEX Plus有Q6到Q12到Q24三種不同的機臺配置,并采用全新一代數字板卡,包括下一代數字板卡UltraPin2200,新一代用于核心電源供電的板卡UVS64,高密度、高靈活性的通用電源板卡UVS256-HP以及下一代高密度模擬板卡UltraPAC300等。其中,Q24最多可以容納12288個數字通道,滿足市面上幾乎所有的需求,更大的測試頭能夠打造更多測試工位,且可以降低測試臺的PCB層數,明顯改善電源完整性或者信號完整性等關鍵性能,擁有更好的測試經濟性和測試效率。

第三,UltraFLEX Plus上面的Broadside應用接口簡化了DIB路由,并改善工位間結果一致性,從而加快上市時間。與傳統的ATE相比,Broadside DIB結構,將板卡較原先結構旋轉了90度,因此板卡的資源,能夠向芯片區域并行傳送。這意味著每個工位,都能夠獲得與之匹配的信號傳輸路徑。通過簡化原本復雜的 DIB布局,實現更快的上市時間、更多的工位數和更高的PCB良率。

面向未來,黃飛鴻表示,今年4nm已經逐漸開始放量,未來馬上會引來3nm和2nm,對測試設備提出的要求有兩項:其一,更高的數據率下面如何保證采樣的精度;其二,單芯片集成的晶體管密度指數級增長,掃描量可能超過1G,對單通道下面能存儲的向量深度提出了更高要求。UltraFLEX plus的掃描量深度最大可以容納19.2G,目前來看能夠滿足3nm和2nm需求。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ATE

+關注

關注

5文章

124瀏覽量

26637 -

測試設備

+關注

關注

0文章

308瀏覽量

17795 -

3nm

+關注

關注

3文章

231瀏覽量

13986

發布評論請先 登錄

相關推薦

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰

電子發燒友網報道(文/李彎彎)近日消息,聯發科、高通新一波5G手機旗艦芯片將于第四季推出,兩大廠新芯片都以臺積電3nm制程生產,近期進入投片階段。 ? 在臺積電3nm制程加持之下,天璣9400的各

蘋果iPhone 17或沿用3nm技術,2nm得等到2026年了!

有消息稱iPhone17還是繼續沿用3nm技術,而此前熱議的2nm工藝得等到2026年了……

臺積電產能爆棚:3nm與5nm工藝供不應求

臺積電近期成為了高性能芯片代工領域的明星企業,其產能被各大科技巨頭瘋搶。據最新消息,臺積電的3nm和5nm工藝產能利用率均達到了極高水平,其中3nm將達到100%,而5nm更是突破了1

lm4673功放出來的聲音很小,調節放大倍數的電阻聲音無明顯變化是怎么回事?

請問lm4673功放出來的聲音很小,調節放大倍數的電阻聲音無明顯變化,調節隔直電容,聲音也沒有變大,這是怎么回事。lm4673在生產過程中怎么提高良品率

發表于 10-24 07:44

聯發科與英偉達合作AI PC 3nm CPU即將流片

據業內消息人士透露,聯發科與英偉達聯手打造的AI PC 3nm CPU即將于本月進入流片階段,預計將于明年下半年正式量產。這一合作標志著聯發科與英偉達在高性能計算領域的深度合作進一步加深。

聯發科將發布安卓陣營首顆3nm芯片

聯發科正式宣告,將于10月9日盛大揭幕其新一代MediaTek天璣旗艦芯片發布會,屆時將震撼推出天璣9400移動平臺。這款芯片不僅是聯發科迄今為止最為強大的手機處理器,更標志著安卓陣營正式邁入3nm工藝時代,成為業界首顆采用臺積電尖端3

臺積電3nm制程需求激增,全年營收預期上調

臺積電近期迎來3nm制程技術的出貨高潮,預示著其在半導體制造領域的領先地位進一步鞏固。隨著蘋果iPhone 16系列新機發布,預計搭載的A18系列處理器將采用臺積電3nm工藝,這一消息直接推動了臺積電3nm制程的訂單量激增,為臺

消息稱臺積電3nm/5nm將漲價,終端產品或受影響

據業內手機晶片領域的資深人士透露,臺積電計劃在明年1月1日起對旗下的先進工藝制程進行價格調整,特別是針對3nm和5nm工藝制程,而其他工藝制程的價格則保持不變。此次漲價的具體幅度為,3nm和5

臺積電3nm工藝穩坐釣魚臺,三星因良率問題遇冷

近日,全球芯片代工領域掀起了不小的波瀾。據媒體報道,臺積電在3nm制程的芯片代工價格上調5%之后,依然收獲了供不應求的訂單局面。而與此同時,韓國的三星電子在3nm工藝上卻遭遇了前所未有

臺積電3nm產能供不應求,驍龍8 Gen44成本或增

在半導體行業的最新動態中,三星的3nm GAA工藝量產并未如預期般成功,其首個3nm工藝節點SF3E的市場應用范圍相對有限。這一現狀促使了科技巨頭們紛紛轉向臺積電,尋求更穩定、更先進的

臺積電3nm工藝產能緊俏,蘋果等四巨頭瓜分

據臺灣媒體報道,近期全球芯片制造巨頭臺積電面臨了3nm系列工藝產能的激烈競爭。據悉,蘋果、高通、英偉達和AMD這四大科技巨頭已經率先瓜分完了臺積電當前的3nm系列工藝產能,導致其他廠商不得不排隊競購,目前相關訂單已經排至2026年。

臺積電3nm工藝迎來黃金期,蘋果等巨頭推動需求飆升

為加速其AI技術的突破,蘋果計劃在今年顯著提升對臺積電3nm晶圓的采購規模。即便蘋果已獨占臺積電全部3nm產能,其訂單量預計仍將較去年激增50%。

無意發展至10nm以下,第二梯隊晶圓代工廠的成熟工藝現狀

梯隊的廠商們還在成熟工藝上穩扎穩打。 ? 早在兩年前,我們還會將28nm視作成熟工藝以及先進工藝的分水嶺。但隨著3nm的推出,以及即將到來的2nm,成熟工藝的定義已經發生了

三星3nm良率 0%!

2500處理器時,發現均存在缺陷,良品率0%。 因為3nm工藝的Exynos 2500處理器存在生產缺陷,導致沒能通過質量測試,后續Galaxy Watch 7的處理器也無法量產。 結合此前爆料

臺積電3nm工藝預計2024年產量達80%

據悉,2024年臺積電的第二代3nm工藝(稱為N3E)有望得到更廣泛運用。此前只有蘋果有能力訂購第一代N3B高端晶圓。經過解決工藝難題及提升產量后,臺積電推出經濟實惠的3nm版型,吸引

3nm時代即將到來,ATE測試機有了這些明顯變化

3nm時代即將到來,ATE測試機有了這些明顯變化

評論