電子發(fā)燒友網(wǎng)報(bào)道(文/吳子鵬)Chiplet,小芯片,也被譯為芯粒,其核心思想是通過預(yù)先開發(fā)設(shè)計(jì)好的die直接集成到IC封裝中,以此來降低芯片開發(fā)的時(shí)間和成本。

目前主流的做法是,如果要打造一顆高性能的芯片,需要開發(fā)一個(gè)片上系統(tǒng)(SoC),然后借助晶圓代工廠的先進(jìn)工藝將里面的功能單元微縮,在相同面積或者更小面積的裸片上實(shí)現(xiàn)更高的性能。很明顯,隨著特征尺寸逐漸逼近物理極限,且工藝復(fù)雜度越來越高,這條路越走下去難度會越大。

通俗地講,小芯片的方式就是像搭積木一樣制造芯片,AMD、英特爾、臺積電、Marvell、Cadence等產(chǎn)業(yè)巨頭對其都頗為關(guān)注,將其視為延續(xù)摩爾定律的選擇之一。在這里,我們看一下AMD在小芯片方面的布局。

可以說,業(yè)界如今對于小芯片的關(guān)注,AMD在其中起到了重要作用。小芯片概念最早可以追溯到上世紀(jì)七十年代的多芯片模組——將原來制造好的芯片再加以組裝。2014 年,芯片設(shè)計(jì)公司開始關(guān)注到這項(xiàng)技術(shù)。2016年,美國國防部高級研究計(jì)劃局Darpa 啟動(dòng)Chips 項(xiàng)目,里面提到了chiplet Reuse 的想法。但小芯片真正聲名鵲起還是因?yàn)锳MD EYPC系列CPU的成功。

2017年,AMD 在其“Zen 2”架構(gòu)中使用小芯片來開發(fā)EYPC 服務(wù)器處理器“Naples”,根據(jù)當(dāng)時(shí)的AMD工程師表述,采用這樣的創(chuàng)新方式,比片上系統(tǒng)設(shè)計(jì)減少了一半的成本,并大幅降低了設(shè)計(jì)時(shí)間。隨后,AMD在消費(fèi)級 CPU和企業(yè)級 EPYC 處理器中都部署了“Zen 2”小芯片技術(shù)。

AMD在官網(wǎng)中提到,“Zen 2”核心在“Zen”架構(gòu)之上進(jìn)行了重大更新。主要優(yōu)勢如下:

時(shí)鐘周期指令數(shù)提升高達(dá) 15%

3 級高速緩存容量翻倍(高達(dá)32MB)

浮點(diǎn)吞吐能力翻倍(256位)

OpCache 容量翻倍(4K)

Infinity Fabric 帶寬翻倍(512位)

全新的 TAGE 分支預(yù)測器

我們以Ryzen 3000 為例來看一下這項(xiàng)技術(shù)的創(chuàng)新點(diǎn)。在之前片上系統(tǒng)的AMD CPU中,會使用四個(gè) Zen CPU 模塊,而在Ryzen 3000 中,AMD采用了Zen 2核心,也就是8個(gè)小CPU核心,采用臺積電7nm工藝,并搭載了采用格芯14nm工藝的 I/O 芯片,既保證了性能,又降低了成本。

通過采用7nm工藝的小CPU核心,AMD EPYC Rome 處理器擁有多達(dá) 8 個(gè)芯片,從而使平臺能夠支持多達(dá) 64 個(gè)內(nèi)核。目前,小芯片技術(shù)已經(jīng)廣泛大量應(yīng)用于AMD的EPYC服務(wù)器CPU和線程撕裂者桌面CPU產(chǎn)品中。

在CPU取得成功之后,AMD又計(jì)劃將小芯片技術(shù)引入到了GPU領(lǐng)域。半導(dǎo)體制造設(shè)備也有光罩尺寸限制,這實(shí)質(zhì)上造成了一個(gè)障礙,無法制造更大的 GPU,這讓后續(xù)單顆GPU芯片的性能提升非常困難。在專利中AMD提到,由于多數(shù)應(yīng)用是以單個(gè)GPU為前提打造的,所以為了保留現(xiàn)有的應(yīng)用編程模型,將小芯片設(shè)計(jì)實(shí)現(xiàn)在GPU上向來都是一大挑戰(zhàn)。

為了解決這一挑戰(zhàn),AMD使用高帶寬互連來促進(jìn)小芯片之間的通信,AMD將這種交聯(lián)稱為 HBX。該方法具體的實(shí)現(xiàn)方式是將CPU連接到第一個(gè)GPU小芯片,并且用一個(gè)無源互連將L3緩存和小芯片之間的其他通道連接在一起。這意味著就 CPU而言,它與一個(gè)大GPU而不是一堆小GPU進(jìn)行通信。 從開發(fā)人員的角度來看,GPU模型不會發(fā)生變化。

在 COMPUTEX 2021 上,AMD 總裁兼首席執(zhí)行官 Lisa Su 分享了AMD在3D小芯片方面的最新進(jìn)展。她表示,AMD 將繼續(xù)利用 AMD 3D 小芯片技術(shù)鞏固其領(lǐng)先的 IP 和對領(lǐng)先制造和封裝技術(shù)的投資,這是一項(xiàng)封裝突破,使用行業(yè)領(lǐng)先的混合鍵合方法將 AMD 的創(chuàng)新小芯片架構(gòu)與3D堆疊相結(jié)合,提供超過200倍的互連密度,2D小芯片的數(shù)量和密度是現(xiàn)有 3D封裝解決方案的15倍以上。與臺積電密切合作率先推出的行業(yè)領(lǐng)先技術(shù),其能耗也低于當(dāng)前的3D解決方案,是世界上最靈活的主動(dòng)對主動(dòng)硅堆疊技術(shù)。

聲明:本文由電子發(fā)燒友原創(chuàng),轉(zhuǎn)載請注明以上來源。如需入群交流,請?zhí)砑游⑿舉lecfans999,投稿爆料采訪需求,請發(fā)郵箱huangjingjing@elecfans.com。

編輯:jq

-

amd

+關(guān)注

關(guān)注

25文章

5479瀏覽量

134306 -

英特爾

+關(guān)注

關(guān)注

61文章

9985瀏覽量

171960 -

臺積電

+關(guān)注

關(guān)注

44文章

5652瀏覽量

166682 -

cpu

+關(guān)注

關(guān)注

68文章

10882瀏覽量

212224 -

soc

+關(guān)注

關(guān)注

38文章

4182瀏覽量

218512

原文標(biāo)題:解密AMD面向未來的小芯片設(shè)計(jì)

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AMD芯片首次進(jìn)入戴爾企業(yè)PC,戴爾品牌簡化新策略

AMD獲得玻璃核心基板技術(shù)專利

使用 AMD Versal AI 引擎釋放 DSP 計(jì)算的潛力

AMD加入玻璃基板戰(zhàn)局

AMD或涉足手機(jī)芯片市場

使用AMD Versal AI引擎加速高性能DSP應(yīng)用

AMD發(fā)布新一代AI芯片MI325X

AMD AI芯片需求井噴,業(yè)績預(yù)估再獲提升

面向手機(jī)直連的星載相控陣:關(guān)鍵技術(shù)與未來展望

使用STM32F407ZGT6的設(shè)備無法連接到AMD處理器的電腦上,怎么處理?

一文詳解超算中的InfiniBand網(wǎng)絡(luò)、HDR與IB

港燈打造了面向未來的下一代電力數(shù)據(jù)中心網(wǎng)絡(luò)

Arm首次面向汽車應(yīng)用發(fā)布Neoverse級芯片設(shè)計(jì)

IP承載網(wǎng)絡(luò)面向Net5.5G將如何持續(xù)演進(jìn)?

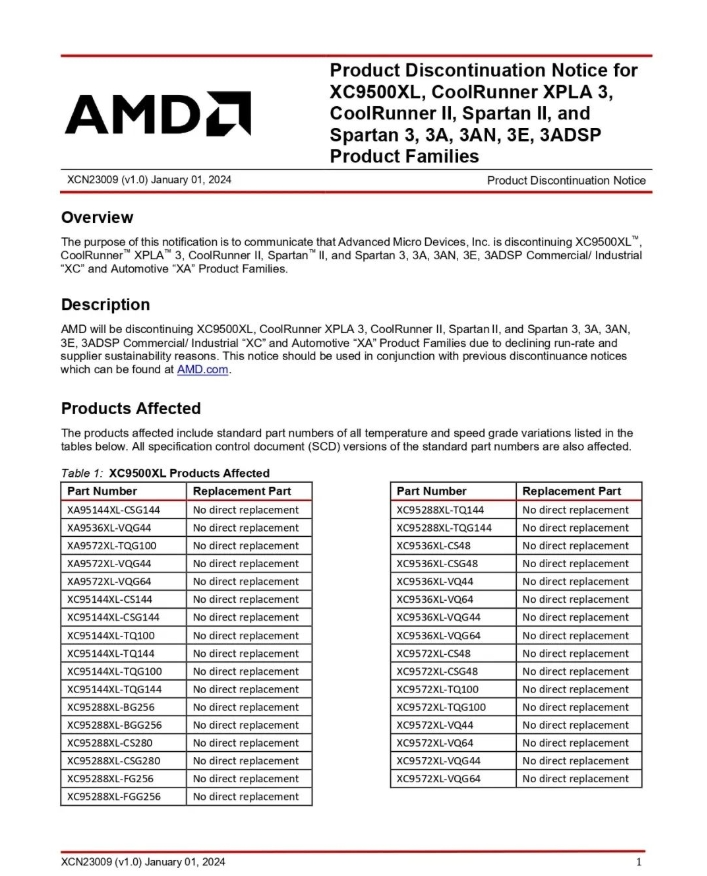

剛剛!AMD宣布停產(chǎn)多款芯片!

揭密AMD面向未來的小芯片設(shè)計(jì)

揭密AMD面向未來的小芯片設(shè)計(jì)

評論