原理

關于Multiboot的原理參考《Xilinx 7系列FPGA Multiboot介紹-遠程更新》,基本原理都在此文寫的很清楚,本文主要從實例出發演示Multiboot。

補充

FPGA SPI閃存配置接口

7系列FPGA和具有x1數據寬度的SPI閃存之間的基本連接。讀取和地址指令通過主輸出-從輸入(MOSI)引腳從FPGA發送到SPI閃存。數據通過主輸入從輸出(MISO)引腳從SPI閃存返回。SCK是時鐘引腳,SS是低電平從選擇引腳。

參考:UG470

Vivado工具流程(Multiboot大致流程)

為Multiboot程序準備bit流

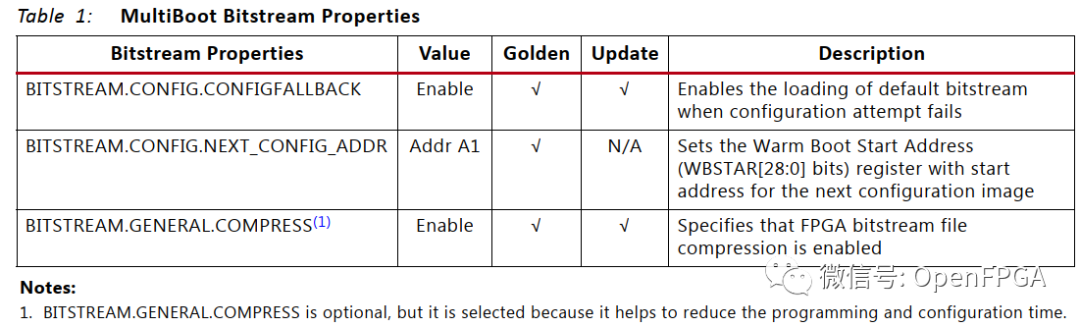

本節概述了為多引導應用程序創建和更新比特流所需的比特流屬性。對于未指定的位流選項,請使用默認設置。

表1概述了用于生成和更新具有每個屬性描述的位流的基本多引導位流屬性。有關這些屬性的詳細說明,請參閱Vivado Design Suite用戶指南:編程和調試(UG908)。

具體含義如下:

啟用在配置嘗試失敗時加載默認位流

使用下一個配置映像的啟動地址設置熱啟動啟動啟動地址(WBSTAR[28:0]位)寄存器

指定啟用FPGA位流文件壓縮

在Vivado中打開黃金設計實現(Golden)的約束文件(.xdc)。將以下內容復制粘貼到約束文件中,然后保存對.xdc文件所做的更改:

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

上述不理解沒關系,后續實例會有使用教程。

接下來,可以在更新設計(將要更新的文件)中打開約束文件(.xdc),并將以下比特流屬性添加到約束文件中,然后保存:

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

注:默認情況下,SPI_BUS為x1,如果未使用默認x1模式,請確保設置此屬性。

生成SPI閃存編程文件

具體查看《【Vivado那些事】Vivado兩種生成、固化燒錄文件》。

使用write_cfgmem Tcl命令創建閃存編程文件(.mcs)。

write_cfgmem獲取FPGA位流(.bit)并生成可用于編程SPI閃存的閃存文件(.mcs)。

例如,生成包含兩個FPGA位流(.bit文件)的閃存編程文件(.mcs)文件,如下所示:

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

注:地址值0x0400000是參考設計中使用的示例。應使用黃金圖像(更新圖像的起始地址)中設置的Addr A1值(見表1)。

請參閱Vivado Design Suite用戶指南:編程和調試(UG908或使用Vivado中的-help命令,以了解每個write_cfgmem命令選項的詳細說明:

write_cfgmem -help

硬件驗證

硬件驗證其實很簡單,我們分別建立兩個工程,兩個工程都是流水燈程序,分別從左到右和從右到左流水燈,這樣可以很清楚知道FPGA運行了哪個程序。接下來破壞golden程序,按照上述制作MCS文件后運行,看下運行哪個程序。

建立工程

詳細的Verilog文件如下:

golden工程

moduleTop_MultiBoot_Module_A(

inputCLK,

outputreg[3:0]LED_Out

);

////////////////////////////////////////////

wireRESET;

assignRESET=1'b1;

////////////////////////////////////////////

//

//首先定義一個時間計數寄存器counter,每當達到預定的100ms時,

//計數寄存器就清零,否則的話寄存器就加1??//然后計算計數器計數的最大值。時鐘頻率為12MHZ??//也就是周期為1/12M ??3ns,要計數的最大值為T100MS= 100ms/83ns-1 = 120_4818??//

reg[31:0]counter;

parameterT100MS=25'd920_4818;

always@(posedgeCLK)

if(counter==T100MS)

counter<=25'd0;

else

counter<=counter+1'b1;

////////////////////////////////////////////

always@(posedgeCLKornegedgeRESET)

if(!RESET)

LED_Out<=4'b0001;//初值,最低位led[0]燈亮

elseif(counter==T100MS)

begin

if(LED_Out==4'b0000)//當溢出最高位時

LED_Out<=4'b0001;//回到復位時的狀態

else

LED_Out<=LED_Out<<1;?????//循環左移一位?

?end

endmodule?//?Run_LED

update工程

moduleTop_MultiBoot_Module_B(

inputCLK,

outputreg[3:0]LED_Out

);

////////////////////////////////////////////

wireRESET;

assignRESET=1'b1;

////////////////////////////////////////////

//

//首先定義一個時間計數寄存器counter,每當達到預定的100ms時,

//計數寄存器就清零,否則的話寄存器就加1??//然后計算計數器計數的最大值。時鐘頻率為12MHZ??//也就是周期為1/12M ??3ns,要計數的最大值為T100MS= 100ms/83ns-1 = 120_4818??//

reg[31:0]counter;

parameterT100MS=25'd920_4818;

always@(posedgeCLK)

if(counter==T100MS)

counter<=25'd0;

else

counter<=counter+1'b1;

////////////////////////////////////////////

always@(posedgeCLKornegedgeRESET)

if(!RESET)

LED_Out<=4'b0001;//初值,最低位led[0]燈亮

elseif(counter==T100MS)

begin

if(LED_Out==4'b0000)//當溢出最高位時

LED_Out<=4'b0001;//回到復位時的狀態

else

LED_Out<=LED_Out<<1;?????//循環左移一位?

?end

endmodule?//?Run_LED

兩個工程基本一樣,流水的操作是在約束里實現的。

golden工程約束

#CLOCKS

#SYSCLK

set_propertyIOSTANDARDLVCMOS18[get_portsCLK]

set_propertyPACKAGE_PIND27[get_portsCLK]

#GPIOLEDs

#set_propertyPACKAGE_PINAB8[get_portsLED_REVXX[7]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[7]]

#set_propertyPACKAGE_PINAA8[get_portsLED_REVXX[6]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[6]]

#set_propertyPACKAGE_PINAC9[get_portsLED_REVXX[5]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[5]]

#set_propertyPACKAGE_PINAB9[get_portsLED_REVXX[4]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[4]]

#set_propertyPACKAGE_PINAE26[get_portsLED_Out[3]]

#set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[3]]

set_propertyPACKAGE_PINT21[get_portsLED_Out[2]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[2]]

set_propertyPACKAGE_PINT20[get_portsLED_Out[1]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[1]]

set_propertyPACKAGE_PINR24[get_portsLED_Out[0]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[0]]

#CFGBVSandSPImodeproperties

set_propertyCFGBVSVCCO[current_design]

set_propertyCONFIG_VOLTAGE2.5[current_design]

set_propertyCONFIG_MODESPIX1[current_design]

#Compressthebitstreamtofiton128MQSPIoftheK7

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

#BITSTREAMPROPERTIESREQUIREDFORGOLDENIMAGE:

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

#(IftheSPIflashisequaltoorgreaterthan256Mb,uncommenttheconstraintbelow):

#set_propertyBITSTREAM.CONFIG.SPI_32BIT_ADDRYES[current_design]

這里解釋一下,前面物理約束不重要,因為“窮”,我的板子只有3顆LED,所以只進行了三個物理約束。

CFGBVS and SPI mode properties及Compress the bitstream to fit on 128M QSPI of the K7、BITSTREAM PROPERTIES REQUIRED FOR GOLDEN IMAGE是重點約束的對象,具體解釋看下表一。

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

這三個約束是和UPDATE工程有關,一個是SPI的BUSWIDTH,一個是否開啟CONFIGFALLBACK,最后一個是地址,這是非常重要的。

接下來是update工程的約束文件

#CLOCKS

#SYSCLK

set_propertyIOSTANDARDLVCMOS18[get_portsCLK]

set_propertyPACKAGE_PIND27[get_portsCLK]

#GPIOLEDs

#set_propertyPACKAGE_PINAB8[get_portsLED_REVXX[7]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[7]]

#set_propertyPACKAGE_PINAA8[get_portsLED_REVXX[6]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[6]]

#set_propertyPACKAGE_PINAC9[get_portsLED_REVXX[5]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[5]]

#set_propertyPACKAGE_PINAB9[get_portsLED_REVXX[4]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[4]]

#set_propertyPACKAGE_PINAE26[get_portsLED_Out[3]]

#set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[3]]

set_propertyPACKAGE_PINR24[get_portsLED_Out[2]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[2]]

set_propertyPACKAGE_PINT20[get_portsLED_Out[1]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[1]]

set_propertyPACKAGE_PINT21[get_portsLED_Out[0]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[0]]

#CFGBVSandSPImodeproperties

set_propertyCFGBVSVCCO[current_design]

set_propertyCONFIG_VOLTAGE2.5[current_design]

set_propertyCONFIG_MODESPIX1[current_design]

#Compressthebitstream

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

#BITSTREAMPROPERTIESREQUIREDFORGOLDENIMAGE:

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

#(IftheSPIflashisequaltoorgreaterthan256Mb,uncommenttheconstraintbelow):

#set_propertyBITSTREAM.CONFIG.SPI_32BIT_ADDRYES[current_design]

物理約束同樣不重要,重要的還是下面的和multiboot相關的約束,具體解釋和上面一樣。

生成Bit流并運行

上述兩個工程分別生成Bit流并運行,查看兩個流水燈是否是兩個不同方向的。

合成MCS文件并運行

將兩個BIT流文件合成一個MCS文件,命令如下:

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

兩個bit流文件位置;

filename: mcs文件名稱。

將上訴mcs文件下載到FPGA開發板上,可以看見update工程文件運行。

破壞Golden文件

回退到Golden可以通過不同的方式觸發。主要有以下幾種方式:

- ID Code錯誤

- CRC錯誤

- Watchdog超時

- BPI地址越界

有關更多信息,請參閱UG470中的重新配置和多引導章節。

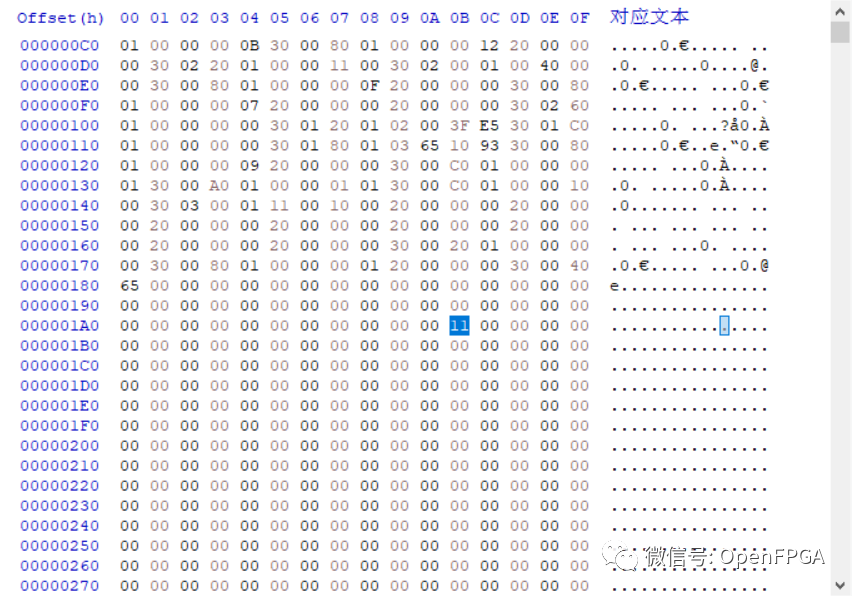

本應用說明演示了由CRC錯誤觸發的回退。可以手動損壞更新位流以導致CRC錯誤。在RESET CRC命令和CRC命令之間有許多可以翻轉位的位置。下圖顯示了一個示例。

- 1.使用十六進制編輯器(HxD Hex Editor)中打開更新(update)比特流(.bit),在比特流中間翻轉一些數據字節,例如從00到11,如圖所示。

為了保證破壞徹底,可以多更改幾處。

- 保存損壞的更新位流,并使用此損壞的位流生成新的閃存編程文件(.mcs)。

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

- 3.重新下載文件

觀察是Golden還是update文件運行,同理可以將上訴命令修改,將golden和update更換一下mcs文件位置,對比測試,上訴兩個情況本人都有親自測試過,都是golden文件運行,證明multiboot已經生效。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605738 -

led

+關注

關注

242文章

23347瀏覽量

662913 -

閃存編程

+關注

關注

0文章

11瀏覽量

6684

原文標題:Xilinx Multiboot實例演示

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

云服務器 Flexus X 實例:部署 Gitea,擁有自己的 Git 倉庫,管理本地代碼

深入解析華為云 X 實例保障云上業務安全的關鍵策略

一文搞懂軟核的固化、啟動和MultiBoot實現

【AG32開發板體驗連載】AG32VF407啟動與探究

深入探究石英可編程 DXO/VCXO 振蕩器 SWPQ201 系列(10MHz 至 1500 MHz)

Python在AI中的應用實例

深入探究 MEMS LVCMOS 振蕩器 SiT1602 系列 52 種標準頻率

神經網絡結構類型和應用實例

步進電機的控制原理與應用實例

飛天技術沙龍回顧:業務創新新選擇,倚天Arm架構深入探討

高效節能的DC電源模塊技術探究

Xilinx fpga芯片系列有哪些

AMD Xilinx 7系列FPGA的Multiboot多bit配置

深入探究Xilinx Multiboot實例

深入探究Xilinx Multiboot實例

評論