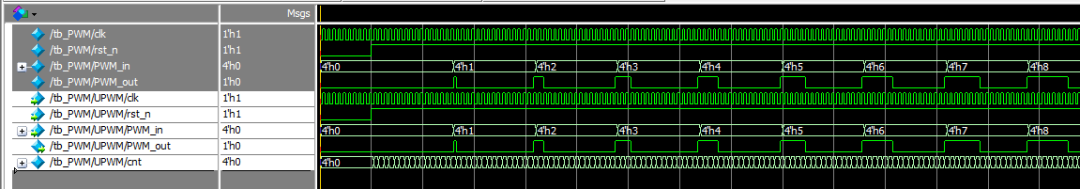

PWM 采用任意寬度的輸入值,并創建只有一位寬度的輸出。使用自由運行計數器的 PWM,這是能做的最簡單的 PWM。

module PWM( input clk, input rst_n, input [3:0] PWM_in, output PWM_out);

reg [3:0] cnt;always @(posedge clk or negedge rst_n) if(!rst_n) cnt《=0; else cnt 《= cnt + 1‘b1; // free-running counter

assign PWM_out = (PWM_in 》 cnt)?1’b1:1‘b0; // comparatorendmodule

選擇了一個4位的 PWM 這里,所以 PWM 周期是16。輸入可以從0到15,因此 PWM 輸出比從0% 到15/16 = 93% 。如果需要能夠達到100% ,輸入需要有一個額外的bit位。

這段代碼工作得很好,盡管當前形式的代碼有點幼稚,因為輸入必須是固定的(或者只有當計數器溢出 = 返回到0時才會更改)。否則輸出將出現故障。因此,很可能需要一些額外的邏輯(通常是在正確的時間捕獲輸入的閂鎖)

使用可加載的上下計數器的 PWM,這是一個稍微復雜一點的設計。

module PWM2( input clk, input rst_n, input [3:0] PWM_in, output PWM_out);

reg [3:0] cnt;reg cnt_dir; // 0 to count up, 1 to count downwire [3:0] cnt_next = cnt_dir ? cnt-1’b1 : cnt+1‘b1;wire cnt_end = cnt_dir ? cnt==4’b0000 : cnt==4‘b1111;

always @(posedge clk or negedge rst_n ) if(!rst_n) cnt 《= 0; else cnt 《= cnt_end ? PWM_in : cnt_next;always @(posedge clk or negedge rst_n) if(!rst_n) cnt_dir《=1’b0; else cnt_dir 《= cnt_dir ^ cnt_end;assign PWM_out = cnt_dir;endmodule

它使用一個可加載的上下計數器,不需要輸出比較器。有趣的是,它并不完全等同于第一個設計,因為輸出周期有17個狀態而不是16個(輸出從1/17 = 6% 到16/17 = 94%)。

編輯:jq

-

PWM

+關注

關注

114文章

5193瀏覽量

214240 -

比較器

+關注

關注

14文章

1656瀏覽量

107304 -

計數器

+關注

關注

32文章

2256瀏覽量

94714

原文標題:verilog 實現PWM DAC

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

使用PWM實現電源管理的策略

如何利用Verilog-A開發器件模型

用于現場發送器的高性能16位PWM 4-20 MA DAC

技術分享:國產工業級HMI芯片Model系列PWM-DAC實現指南

在低成本MSP430 MCU上使用PWM實現數字DAC應用說明

淺析基于verilog如何實現PWM DAC

淺析基于verilog如何實現PWM DAC

評論