提出一種可進(jìn)化IP核的設(shè)計(jì)和實(shí)現(xiàn)方法。這種IP核采用進(jìn)化硬件的設(shè)計(jì)思想,將遺傳算法運(yùn)用于硬件電路的設(shè)計(jì)中,使電路能根據(jù)當(dāng)前的環(huán)境自動(dòng)進(jìn)行內(nèi)部電路的時(shí)化,從而生成最有效的電路,并能在普通的FPGA器件上實(shí)現(xiàn)。可進(jìn)化IP核以HDL源泉代碼的形式表示,與普通IP核的復(fù)用方式相同,可被綜合到不同的目標(biāo)可重構(gòu)器件中去,大大減少了復(fù)雜系統(tǒng)的設(shè)計(jì)時(shí)間,提高了設(shè)計(jì)的利用率,是可進(jìn)化硬件一個(gè)頗具潛力的發(fā)展方向。

隨著信息技術(shù)的飛速發(fā)展,計(jì)算機(jī)系統(tǒng)面臨的問(wèn)題越來(lái)越復(fù)雜,如何保證復(fù)雜系統(tǒng)的可靠性成為一個(gè)不容忽視的問(wèn)題。可進(jìn)化硬件給我們提供了一個(gè)很好的解決方案。可進(jìn)化硬件EHW(Evolvable Hardware)是將進(jìn)化算法和可編程邏輯元件融合在一起而產(chǎn)生的一種新的硬件研究流派。當(dāng)所使用的環(huán)境發(fā)生變化時(shí),或被放置于未知的環(huán)境中時(shí),這種硬件會(huì)自動(dòng)地改變內(nèi)部結(jié)構(gòu),使之經(jīng)常處于最適合狀態(tài),快速高效地完成規(guī)定的任務(wù)。

可編程門(mén)陣列(FPGA)以其獨(dú)有的優(yōu)點(diǎn)為國(guó)外多數(shù)研究人員用作硬件進(jìn)化平臺(tái)。EHW利用FPGA的在線(xiàn)可編程技術(shù)(ISP)及動(dòng)態(tài)重構(gòu)技術(shù),將FPGA的配置信息作為染色體,通過(guò)遺傳算法(GA)對(duì)其進(jìn)行反復(fù)的適應(yīng)度計(jì)算,交叉和變異,最終進(jìn)化出符號(hào)環(huán)境要求的個(gè)體(即電路配置),從而使電路適合環(huán)境的變化。

與此同時(shí),隨著FPGA技術(shù)的發(fā)展,芯片的性能越來(lái)越強(qiáng)、規(guī)模越來(lái)越大、開(kāi)發(fā)的周期越來(lái)越長(zhǎng),使得芯片設(shè)計(jì)業(yè)正面臨一系列新的問(wèn)題:設(shè)計(jì)質(zhì)量難以控制,設(shè)計(jì)成本也越來(lái)越高。IP(Intelligence Property)技術(shù)解決了當(dāng)今芯片設(shè)計(jì)業(yè)所面臨的難題。IP是指可用來(lái)生成ASIC和PLD的邏輯功能塊,又稱(chēng)IP核(IP Core)或虛擬器件(VC)。設(shè)計(jì)者可以重復(fù)使用已經(jīng)設(shè)計(jì)并經(jīng)過(guò)驗(yàn)證的IP核,從而專(zhuān)注于整個(gè)系統(tǒng)的設(shè)計(jì),提高設(shè)計(jì)的效率和正確性,降低成本。目前數(shù)字IP已得到了充分的發(fā)展,可以很方便地購(gòu)買(mǎi)到IP核并整合到SoC的設(shè)計(jì)中。

因此,可以考慮將進(jìn)化硬件的思想應(yīng)用于IP核的設(shè)計(jì)中,設(shè)計(jì)一種可進(jìn)化的IP核,根據(jù)當(dāng)前的環(huán)境進(jìn)化出相應(yīng)的電路,并能夠在普通的可重構(gòu)器件中實(shí)現(xiàn)。

1 什么是可進(jìn)化IP核

從進(jìn)化硬件的經(jīng)驗(yàn)可知,系統(tǒng)通常只有一部分是適應(yīng)性的(可進(jìn)化的),另一部分可以通過(guò)傳統(tǒng)的不可變的電路來(lái)實(shí)現(xiàn)。同樣,使用IP核構(gòu)造的系統(tǒng)也是有些IP核是可進(jìn)化的,有些IP核是不可變的。可進(jìn)化的那些IP核稱(chēng)為可進(jìn)化組件或可進(jìn)化IP核。

可進(jìn)化IP核像普通的IP核一樣被存儲(chǔ)在組件庫(kù)中,在被下載并放在一個(gè)可重構(gòu)器件中后,它們將自動(dòng)地進(jìn)化它們的內(nèi)部電路。當(dāng)不再需要適應(yīng)性行為時(shí),可以從可重構(gòu)器件中刪除可進(jìn)化IP核。可進(jìn)化IP核和普通IP核的復(fù)用方式相同。

2 可進(jìn)化IP核的一般體系結(jié)構(gòu)

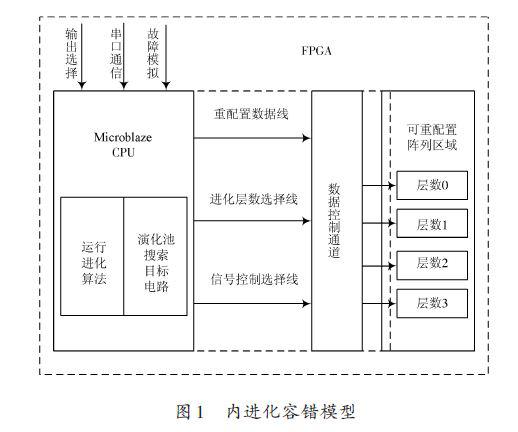

如圖1所示,可進(jìn)化IP核由可重構(gòu)電路,基因單元和控制器構(gòu)成(本文中可重構(gòu)電路是指可進(jìn)化IP核內(nèi)的一個(gè)部分;可重構(gòu)器件是指整個(gè)可重構(gòu)平臺(tái),如FPGA)。這里要強(qiáng)調(diào)的是,基因單元不包含適應(yīng)度計(jì)算,它只實(shí)現(xiàn)基因的操作、染色體存儲(chǔ)和適應(yīng)度存儲(chǔ)。適應(yīng)度的計(jì)算和環(huán)境由其它的核來(lái)提供。基因單元生成一些配置并上載到可重構(gòu)電路中去,環(huán)境對(duì)這些配置進(jìn)行評(píng)估,并將適應(yīng)度值發(fā)送給IP核。可進(jìn)化IP核實(shí)際上是一個(gè)由環(huán)境控制的電路生成器。

環(huán)境(由其它核提出)和可進(jìn)化IP核之間的通信如下:首先IP核被初始化(生成初始化種群),然后進(jìn)入如下無(wú)限循環(huán)——當(dāng)環(huán)境發(fā)生變化后,環(huán)境計(jì)算當(dāng)前電路配置的適應(yīng)度,并判斷電路是否適應(yīng)環(huán)境。如果染色體存儲(chǔ)器中的配置不可用,則向IP核發(fā)出控制信息,IP核開(kāi)始進(jìn)化。即基因單元把硬件配置信息作為染色體,根據(jù)適應(yīng)度對(duì)其進(jìn)行交叉、變異等遺傳操作,生成一個(gè)新的種群。環(huán)境對(duì)新種群進(jìn)行適應(yīng)度計(jì)算,并判斷是否有滿(mǎn)足當(dāng)前環(huán)境的個(gè)體(配置)。若沒(méi)有,向IP核發(fā)控制信息,遺傳單元繼續(xù)對(duì)電路配置進(jìn)行進(jìn)化,直至有滿(mǎn)足當(dāng)前環(huán)境的配置為止;若有,則將適應(yīng)度值發(fā)給IP核,IP核用這個(gè)新生成的最優(yōu)配置來(lái)重配置可重構(gòu)電路,并在染色體存儲(chǔ)器中保存當(dāng)前最優(yōu)配置及其適應(yīng)度值,等待來(lái)自環(huán)境的下一個(gè)請(qǐng)求。

環(huán)境總是要求下載當(dāng)前最優(yōu)的進(jìn)化電路,因此,IP核必須保存目前為止最優(yōu)的配置,并且在需要的時(shí)候提供出去。可進(jìn)化IP核總是屏蔽重構(gòu)過(guò)程,因此它對(duì)于外部環(huán)境來(lái)說(shuō)是不可見(jiàn)的。

對(duì)于一些特殊的應(yīng)用,必須為它們開(kāi)發(fā)專(zhuān)用的可進(jìn)化IP核,因?yàn)榉从硲?yīng)用的要求基因單元和可重構(gòu)電路的體系結(jié)構(gòu)將使進(jìn)化過(guò)程優(yōu)于一個(gè)隨機(jī)的搜索。由于適應(yīng)度計(jì)算是在IP核外進(jìn)行的,因此IP核原則上支持動(dòng)態(tài)適應(yīng)度函數(shù)和無(wú)限的進(jìn)化。可進(jìn)化IP核可以用軟件實(shí)現(xiàn)。

3 可進(jìn)化IP核的實(shí)現(xiàn)

3.1 實(shí)現(xiàn)中的問(wèn)題

可復(fù)用的IP核通常有軟核、固核和硬核三種。本文討論的是軟核。本文的目標(biāo)是,設(shè)計(jì)和實(shí)現(xiàn)以HDL源代碼(例如,VHDL)表示的可進(jìn)化IP核。其優(yōu)點(diǎn)是IP核的表示獨(dú)立于平臺(tái),這樣它們就可以在各種不同的目標(biāo)結(jié)構(gòu)中運(yùn)行。要解決的主要問(wèn)題是,可進(jìn)化的IP核的內(nèi)部可重構(gòu)電路的自動(dòng)重構(gòu)(因?yàn)樗鼈兪强蛇M(jìn)化的)。

當(dāng)一個(gè)可進(jìn)化IP核從一個(gè)組件庫(kù)中被下載到可重構(gòu)器件的一個(gè)指定位置時(shí),它的內(nèi)部可重構(gòu)電路必須進(jìn)行重構(gòu)。這就意味著這個(gè)可重構(gòu)器件中的一些可編程塊必須能配置這個(gè)可重構(gòu)器件的其它內(nèi)部可編程塊。另外,這個(gè)可進(jìn)化IP核(它的基因單元)能被放置于這個(gè)可編程陣列(即可重構(gòu)器件)的任何位置,也就是說(shuō),這個(gè)可重構(gòu)器件中必須支持內(nèi)部重構(gòu)。

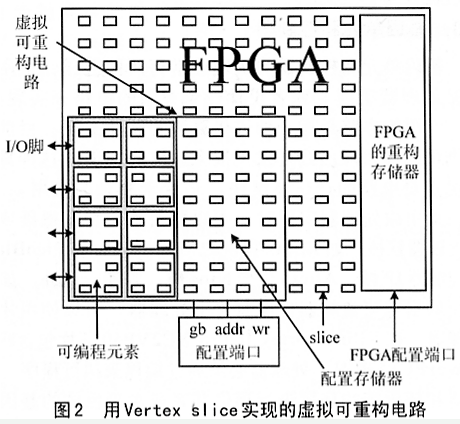

FPGA以其動(dòng)態(tài)可重構(gòu)的優(yōu)點(diǎn),無(wú)疑是可進(jìn)化IP核的最佳實(shí)現(xiàn)平臺(tái)。然而,通常的FPGA并不支持內(nèi)部重構(gòu),而只允許通過(guò)一個(gè)特殊的配置接口外部重構(gòu)(如圖2)。目前,只存在一種支持內(nèi)部重構(gòu)的平臺(tái),就是單元陣列,但這種芯片目前還相當(dāng)少。因此,為了在普通FPGA器件實(shí)現(xiàn)可進(jìn)化IP核,使之能在實(shí)際應(yīng)用中發(fā)揮作用,必須采用其它的一些方法。硬件虛擬化是基于FPGA的系統(tǒng)常用的一種設(shè)計(jì)技術(shù)。從這個(gè)思想出發(fā),本文采用了一個(gè)被稱(chēng)為虛擬可重構(gòu)電路的技術(shù)來(lái)實(shí)現(xiàn)可進(jìn)化硬件中的內(nèi)部可重構(gòu)電路。但文中對(duì)設(shè)計(jì)虛擬可重構(gòu)電路的概念進(jìn)行了擴(kuò)展。

3.2 虛擬可重構(gòu)電路

一些FPGA芯片支持部分重構(gòu),也就是允許可重構(gòu)系統(tǒng)的一部分重構(gòu),而不影響其余部分的運(yùn)行。部分重構(gòu)的優(yōu)點(diǎn)在于,其重構(gòu)所花的時(shí)間比全部重構(gòu)更少。本文以支持部分重構(gòu)的Xilinx Virtex FPGA為例,來(lái)說(shuō)明虛擬可重構(gòu)電路的實(shí)現(xiàn)。IP核可以動(dòng)態(tài)地下載到FPGA或從FPGA刪除。所有的操作都通過(guò)Virtex重構(gòu)端口和Jbits接口來(lái)完成。當(dāng)一個(gè)可進(jìn)化IP核被下載時(shí),它的重構(gòu)位串在指定位置構(gòu)靠下列單元;虛擬可重構(gòu)電路、基因單元和控制器。

圖2表明,虛擬可重構(gòu)電路實(shí)際上是一種在普通FPGA上實(shí)現(xiàn)的新的可重構(gòu)電路。本例中由八個(gè)可編程元素構(gòu)成,由Virtex單元(slice)實(shí)現(xiàn)。Virtex單元實(shí)現(xiàn)新的可編程元素陣列、新的布線(xiàn)電路和新的配置存儲(chǔ)器。虛擬電路能內(nèi)部重構(gòu),但如果有其它新的配置存儲(chǔ)器與之連接,也可從FPGA的I/O引腳配置。

這種方法的優(yōu)點(diǎn)在于:可根據(jù)具體的應(yīng)用需要準(zhǔn)確地設(shè)計(jì)可編程元素陣列、布線(xiàn)電路和配置存儲(chǔ)器。虛擬可重構(gòu)電路的重構(gòu)方式和粒度能準(zhǔn)確地反映具體應(yīng)用的需要。通過(guò)虛擬可重構(gòu)電路,很容易把領(lǐng)域知識(shí)插入到基因單元和可重構(gòu)電路的體系結(jié)構(gòu)中,從而獲得電路軟件模型的精確實(shí)現(xiàn)。

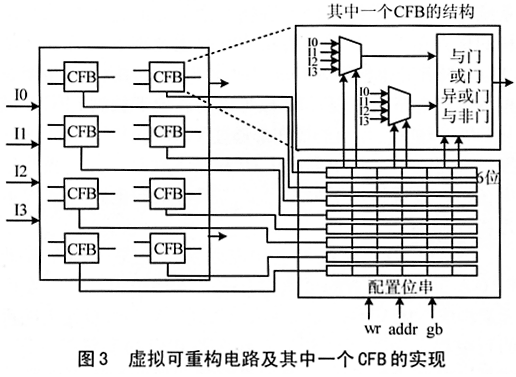

圖3給出了一個(gè)虛擬可編程元素的例子。這個(gè)虛擬可重構(gòu)電路由8個(gè)這樣的元素構(gòu)成,有4個(gè)輸入和2個(gè)輸出。這些虛擬可編程元素稱(chēng)為可重配置功能塊CFB(Configurable Functional Blocks)。每個(gè)CFB對(duì)應(yīng)一個(gè)配置位串(這里的位串為6位),其中兩個(gè)配置位決定了CFB的功能,其它四位定義了輸入的連接信息。布線(xiàn)電路由多路器組成,它們由配置存儲(chǔ)器中的位串控制。配置存儲(chǔ)器由Virtex單元構(gòu)成,一個(gè)Virtex單元包含兩個(gè)觸發(fā)器,用于存儲(chǔ)配置位串中的兩位。配置存儲(chǔ)器的所有位都連到多路器,多路器控制布線(xiàn)和CFB中功能的選擇。

虛擬可重構(gòu)電路中CFB的數(shù)量由具體的應(yīng)用決定。虛擬可重構(gòu)電路用結(jié)構(gòu)級(jí)VHDL語(yǔ)言來(lái)描述,但是一些基本的電路(例如“MAX”電路)用行為級(jí)來(lái)描述。虛擬可重構(gòu)能在不同的目標(biāo)器件下綜合,目標(biāo)器件并不需要支持部分重構(gòu)。

3.3 基因單元和控制器

基因單元和控制器的實(shí)現(xiàn)通常有兩種選擇:采用普通微處理器實(shí)現(xiàn),或者設(shè)計(jì)一個(gè)專(zhuān)用的電路來(lái)實(shí)現(xiàn)。

專(zhuān)用的電路是指一種進(jìn)化算法的硬件實(shí)現(xiàn),目前在可進(jìn)化硬件領(lǐng)域已經(jīng)開(kāi)發(fā)了很多這樣的實(shí)現(xiàn)。這種算法的優(yōu)點(diǎn)是電路的進(jìn)化速度快,適合于復(fù)雜的應(yīng)用。

采用微處理器實(shí)現(xiàn)時(shí),可以購(gòu)買(mǎi)或免費(fèi)獲得現(xiàn)成的微處理器軟核,如Xilinx提供的MicroBlaze和PicoBlaze微控制器IP核,Altera生產(chǎn)Nios核,等等。此外,如果給出的目標(biāo)可重構(gòu)器件中有片上處理器,可以使用片上處理器,Xilinx Virtex II Pro XC2VP50芯片包含四個(gè)PowerPC處理器。處理器必須通過(guò)編程來(lái)執(zhí)行程序,它們能和核周?chē)沫h(huán)境進(jìn)行通信并完成對(duì)染色體的基因操作。此外,處理器還負(fù)責(zé)內(nèi)部虛擬可重構(gòu)電路的重構(gòu)。

4 結(jié)論

文中定義了數(shù)字系統(tǒng)設(shè)計(jì)的一個(gè)新的抽象級(jí)別,并將一些組件的方法引入可進(jìn)化硬件的設(shè)計(jì)。為了實(shí)現(xiàn)可進(jìn)化IP核,使用一種虛擬可重構(gòu)電路。這種方法在門(mén)的數(shù)量方面代價(jià)稍大,但卻能大大加快進(jìn)化硬件的速度。

可進(jìn)化IP核的設(shè)計(jì)目的主要是以合理的代價(jià)實(shí)現(xiàn)適應(yīng)性和高性能實(shí)時(shí)系統(tǒng),最常見(jiàn)的如圖像壓縮。本文提出的核的結(jié)構(gòu)和接口都只是最基本的,實(shí)際應(yīng)用中還可進(jìn)行擴(kuò)充。例如,還可以給核擴(kuò)充一個(gè)讀配置的端口,這個(gè)對(duì)于某些應(yīng)用來(lái)說(shuō)是必需的。或者在可進(jìn)化IP核中包含兩個(gè)虛擬可重構(gòu)電路RC1和RC2。RC1實(shí)現(xiàn)當(dāng)前最優(yōu)的進(jìn)化電路。電路不斷進(jìn)化在RC2中完成。如果RC2中進(jìn)化出更好的電路,就把它的配置送入RC1,然后RC1以一系列數(shù)字電路的形式表現(xiàn)出對(duì)變化的環(huán)境的最佳的響應(yīng)。

與以往的方法相比,本文提出的方法具有更強(qiáng)的適應(yīng)性和可移植性。可進(jìn)化IP核以HDL源代碼的形式表示,易于重用和修改。此外,進(jìn)化的配置位串也可以作為一種變化的IP核在其它應(yīng)用中被重用。可進(jìn)化IP核縮短了電路設(shè)計(jì)的時(shí)間,提高了設(shè)計(jì)的利用率,促進(jìn)可進(jìn)化硬件向?qū)嵱没陌l(fā)展。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603589 -

PLD

+關(guān)注

關(guān)注

6文章

224瀏覽量

59415 -

IP核

+關(guān)注

關(guān)注

4文章

327瀏覽量

49506

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于演化硬件技術(shù)的內(nèi)進(jìn)化容錯(cuò)模型設(shè)計(jì)與可靠性研究分析

基于IP橋接技術(shù)實(shí)現(xiàn)密碼算法多IP核集成的應(yīng)用方案設(shè)計(jì)

基于FPGA的數(shù)據(jù)采集控制器IP核的設(shè)計(jì)方案和實(shí)現(xiàn)方法研究

Altera浮點(diǎn)矩陣相乘IP核怎么提高運(yùn)算速度?

求大佬分享一種可進(jìn)化IP核的設(shè)計(jì)和實(shí)現(xiàn)方法

一種可進(jìn)化IP 核的設(shè)計(jì)和實(shí)現(xiàn)

基于EHW 的可進(jìn)化傳感器的研究

USB設(shè)備接口IP核的設(shè)計(jì)

基于SOPC技術(shù)的異步串行通信IP核的設(shè)計(jì)

三個(gè)不同AXI IP核的實(shí)現(xiàn)的方法_性能的對(duì)比及差異的分析

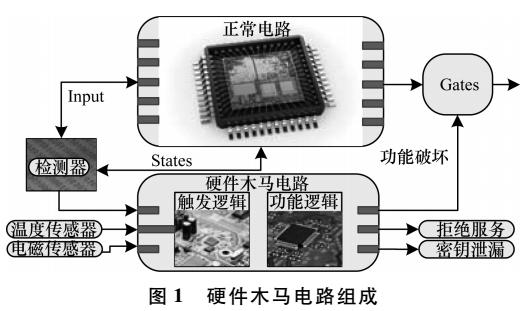

基于特征匹配的IP軟核硬件木馬檢測(cè)

FPGA實(shí)現(xiàn)基于Vivado的BRAM IP核的使用

HDLC協(xié)議IP核的設(shè)計(jì)與實(shí)現(xiàn)

基于可進(jìn)化硬件EHW實(shí)現(xiàn)IP核的改進(jìn)設(shè)計(jì)

基于可進(jìn)化硬件EHW實(shí)現(xiàn)IP核的改進(jìn)設(shè)計(jì)

評(píng)論