時(shí)鐘設(shè)計(jì)方案在復(fù)雜的FPGA設(shè)計(jì)中,設(shè)計(jì)時(shí)鐘方案是一項(xiàng)具有挑戰(zhàn)性的任務(wù)。設(shè)計(jì)者需要很好地掌握目標(biāo)器件所能提供的時(shí)鐘資源及它們的限制,需要了解不同設(shè)計(jì)技術(shù)之間的權(quán)衡,并且需要很好地掌握一系列設(shè)計(jì)實(shí)踐知識(shí)。

不正確的設(shè)計(jì)或次優(yōu)的時(shí)鐘方案可能會(huì)導(dǎo)致在最好情況下較差的設(shè)計(jì)性能,或者在最壞情況下的隨機(jī)和難以查找的錯(cuò)誤。FPGA時(shí)鐘資源指目標(biāo)FPGA中大量與時(shí)鐘有關(guān)的不同資源,如時(shí)鐘類(lèi)型(局部的和全局的)、頻率限制和不同時(shí)鐘管理器的抖動(dòng)特性,以及能用于單個(gè)時(shí)鐘域的時(shí)鐘最大數(shù)量。本文介紹了時(shí)鐘設(shè)計(jì)方案中的每個(gè)部分,并推薦了一些設(shè)計(jì)方法。

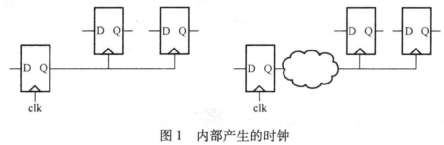

內(nèi)部產(chǎn)生的時(shí)鐘是組合邏輯或寄存器的輸出,如圖1所示。

組合邏輯產(chǎn)生的時(shí)鐘可能有毛刺,會(huì)被錯(cuò)誤地當(dāng)成有效時(shí)鐘邊沿,在設(shè)計(jì)中會(huì)導(dǎo)致功能錯(cuò)誤。因此,不要使用組合邏輯的輸出作為時(shí)鐘。內(nèi)部產(chǎn)生的時(shí)鐘使用通用布線(xiàn)資源。因此,與專(zhuān)用時(shí)鐘布線(xiàn)相比延遲較長(zhǎng)。其后果是時(shí)鐘偏移增加,滿(mǎn)足時(shí)序的過(guò)程更加困難。如果大量的邏輯使用了該內(nèi)部時(shí)鐘,這個(gè)問(wèn)題尤為突出。公眾號(hào):OpenFPGA作為一般規(guī)則,盡量避免使用內(nèi)部產(chǎn)生的時(shí)鐘,盡可能使用專(zhuān)用時(shí)鐘資源。

除了一些特殊電路[如雙倍數(shù)據(jù)速率(DDR)的數(shù)據(jù)捕獲]之外,寄存數(shù)據(jù)通常總是使用時(shí)鐘的上升沿或下降沿。使用兩個(gè)邊沿帶來(lái)的問(wèn)題是由于時(shí)鐘占空比可能并不總是50%,這會(huì)對(duì)電路的正常工作產(chǎn)生影響。

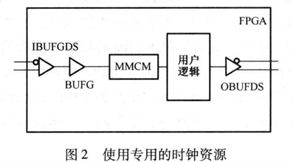

建議在頻率高的情況下使用差分時(shí)鐘。通常認(rèn)為頻率高于100MHz以上屬于高頻。差分時(shí)鐘相比單端時(shí)鐘的主要優(yōu)勢(shì)是共模噪聲抑制,因此抗噪聲性能更好。具有PECL、LVPECL和LVDS信號(hào)電平的差分時(shí)鐘是高速邏輯下時(shí)鐘的首選。Xilinx FPGA提供了一些用于差分時(shí)鐘的專(zhuān)用原語(yǔ):IBUFDS、IBUFGDS、IBUFGDS_DIFF、OBUFDS、0BUFTDS等(見(jiàn)圖2)。

時(shí)鐘門(mén)控是設(shè)計(jì)中通過(guò)使用控制信號(hào),禁止或允許時(shí)鐘輸入到寄存器和其他同步元件上的一種方法。它能有效降低功耗,因此被廣泛應(yīng)用于ASIC設(shè)計(jì)中。然而,在FPGA設(shè)計(jì)中應(yīng)盡量避免使用門(mén)控時(shí)鐘。

不建議將時(shí)鐘信號(hào)作為通用邏輯的控制、復(fù)位或數(shù)據(jù)輸入。下面是這類(lèi)電路的例子。

module clock_schemes(input clk1,clk2,clk3,clk4,clk5,input data_in,output reg data_out1,data_out2,data_out3,data_out4,data_out5,data_out6);wire data_from_clock, reset_from_clock, control_from_clock;/ / 時(shí)鐘被用做數(shù)據(jù)輸入assign data_from_clock = clk1;always @(posedge clkl) data out1 《= ~data out1;

always @(posedge clk2) data out2 《= ~data out2 & data_from_clock;

/ / 時(shí)鐘被用做復(fù)位輸入assign reset_from_clock = clk3;always @(posedge clk3) data out3 《= ~data out2;always @(posedge clk4, posedge reset_from_clock) if (reset_from_clock) data_out4 《= 0; else data out4 《= data in;/ / 時(shí)鐘被用做控制assign control_from_clock = clk5;always @(posedge clk5) data out5 《= ~data out5;always @(*) data_out6 = control_from_clock ? data_in : data_out6;endmodule // clock schemes

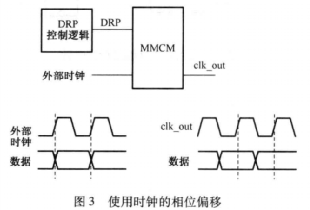

許多與FPGA接口的外設(shè)都使用與數(shù)據(jù)一樣的源同步時(shí)鐘。如果接口在高速下工作,可能需要對(duì)時(shí)鐘邊沿進(jìn)行校準(zhǔn),以便在數(shù)據(jù)窗口的中間捕獲數(shù)據(jù)。為實(shí)現(xiàn)動(dòng)態(tài)校準(zhǔn)Xilinx MMCM原語(yǔ)提供了動(dòng)態(tài)重新配置端口DRP),允許時(shí)鐘的可編程相位偏移。圖3說(shuō)明了來(lái)自MMCM的時(shí)鐘被移位后,使時(shí)鐘的上升沿在窗口的中間位置采樣數(shù)據(jù)。

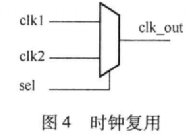

當(dāng)同一個(gè)邏輯有來(lái)自不同時(shí)鐘源的時(shí)鐘時(shí),需要在設(shè)計(jì)中對(duì)這些時(shí)鐘源進(jìn)行時(shí)鐘復(fù)用(見(jiàn)圖4)。一個(gè)例子是使用2.5MHz、25MHz或125MHz時(shí)鐘的以太網(wǎng)MAC,選取哪種時(shí)鐘取決于10Mbps、100Mbps或1Gbps的協(xié)商速度(negotiated speed)。另一個(gè)例子是電源內(nèi)置自測(cè)(BIST)電路,在正常工作期間,使用了來(lái)自同一個(gè)時(shí)鐘源的不同時(shí)鐘信號(hào)。公眾號(hào):OpenFPGA

建議使用專(zhuān)用的時(shí)鐘資源實(shí)現(xiàn)時(shí)鐘復(fù)用,確保輸人和輸出時(shí)鐘使用專(zhuān)用時(shí)鐘線(xiàn),而不是通用邏輯。參與復(fù)用的時(shí)鐘頻率可能彼此并不相關(guān)。使用組合邏輯實(shí)現(xiàn)的多路復(fù)用器在切換時(shí)會(huì)在時(shí)鐘線(xiàn)上產(chǎn)生毛刺,從而危害整個(gè)系統(tǒng)。這些毛刺會(huì)被一些寄存器當(dāng)成有效時(shí)鐘邊沿,而被另一些寄存器忽略。

Xilinx提供了能在兩個(gè)全局時(shí)鐘源之間進(jìn)行復(fù)用的BUFGMUX原語(yǔ)。它還確保了當(dāng)輸人時(shí)鐘切換后不會(huì)產(chǎn)生毛刺。時(shí)鐘復(fù)用需要對(duì)復(fù)用器中所有從輸入到輸出的時(shí)鐘路徑進(jìn)行細(xì)致的時(shí)序約束

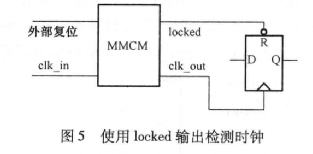

檢測(cè)時(shí)鐘缺失 (absence)的一種方法,是使用其他更高速的時(shí)鐘對(duì)其進(jìn)行過(guò)采樣,缺點(diǎn)是時(shí)鐘可能沒(méi)有可用的高速時(shí)鐘。還有一種方法是使用 Xilinx MMCM 原語(yǔ)的 locked 輸出,如圖 5 所示。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604306 -

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120668 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7081瀏覽量

89189 -

Xilinx

+關(guān)注

關(guān)注

71文章

2168瀏覽量

121687

原文標(biāo)題:FPGA時(shí)鐘設(shè)計(jì)方案

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

2024年ICPC與華為挑戰(zhàn)賽冠軍杯圓滿(mǎn)落幕

邊緣計(jì)算的技術(shù)挑戰(zhàn)與解決方案

【智能生活新寵】:WTR096芯片語(yǔ)音時(shí)鐘方案,錄音播放+時(shí)鐘提醒+計(jì)時(shí)時(shí)鐘功能一體,一鍵掌控您的日常節(jié)奏

康謀分享 | 在基于場(chǎng)景的AD/ADAS驗(yàn)證過(guò)程中,識(shí)別挑戰(zhàn)性場(chǎng)景!

CC2340系統(tǒng)降低成本的方案剖析

FPGA設(shè)計(jì)面臨的挑戰(zhàn)和解決方案

FPGA的sata接口設(shè)計(jì)時(shí)需要注意哪些問(wèn)題

具有密集交聯(lián)結(jié)構(gòu)的明膠基水凝膠電解質(zhì)(ODGelMA)

使用STM8L做內(nèi)部RTC做時(shí)鐘,時(shí)鐘計(jì)時(shí)計(jì)到了超過(guò)24時(shí)怎么解決?

EPSON 的 RX8010SJ 為安防產(chǎn)品提供高可靠性低功耗的實(shí)時(shí)時(shí)鐘模塊解決方案

單片機(jī)開(kāi)發(fā)好學(xué)嗎?學(xué)習(xí)中有哪些樂(lè)趣與挑戰(zhàn)?

硬件工程師在可靠性設(shè)計(jì)中所面臨的挑戰(zhàn)及解決之道

時(shí)鐘同步系統(tǒng)在網(wǎng)絡(luò)通信中的重要性及優(yōu)勢(shì)

探討制造中差異變量的概念和重要性

FPGA時(shí)鐘內(nèi)部設(shè)計(jì)方案

剖析具有挑戰(zhàn)性的設(shè)計(jì)時(shí)鐘方案

剖析具有挑戰(zhàn)性的設(shè)計(jì)時(shí)鐘方案

評(píng)論