中科院微電子所近期發(fā)表了先導(dǎo)工藝研發(fā)中心團(tuán)隊(duì)在垂直納米環(huán)柵器件領(lǐng)域獲得的最新進(jìn)展,該類型器件通過(guò)在垂直方向構(gòu)建晶體管結(jié)構(gòu),大大減少了器件占用面積,在3nm以下先進(jìn)集成電路制造工藝領(lǐng)域極具應(yīng)用潛力。

研究背景

GAA晶體管由于溝道由柵極完全包圍而具有更好的溝道控制和靜電性能而被產(chǎn)業(yè)界賦予厚望,行業(yè)集成電路制造龍頭都前后公布了相關(guān)技術(shù)的規(guī)劃。與傳統(tǒng)水平溝道的晶體管結(jié)構(gòu)相比,名為vertical GAA FET的垂直GAA晶體管器件(暫譯名)由于其溝道方向變?yōu)榇怪薄?/p>

在器件結(jié)構(gòu)設(shè)計(jì)時(shí),溝道長(zhǎng)度和源漏接觸區(qū)的面積占用不再那么難以解決,但是相應(yīng)的,要實(shí)現(xiàn)這樣的結(jié)構(gòu)對(duì)制造工藝提出了嚴(yán)峻的挑戰(zhàn),例如通過(guò)刻蝕時(shí)間來(lái)控制溝道長(zhǎng)度的過(guò)程變得更加復(fù)雜了,在實(shí)現(xiàn)路徑上,缺乏一種成熟的技術(shù)手段來(lái)實(shí)現(xiàn)從柵極自對(duì)準(zhǔn)到精準(zhǔn)控制溝道長(zhǎng)度的過(guò)程,而這對(duì)于提升芯片性能和可制造性至關(guān)重要。

在GAA晶體管發(fā)揮作用的領(lǐng)域,器件制造工藝需要原子尺寸級(jí)別的大小控制和精確定位排布,原子層刻蝕(ALE,下同)技術(shù)眾多技術(shù)路徑中最具潛力實(shí)現(xiàn)原子尺度工藝控制的技術(shù)之一,但面臨工藝時(shí)間長(zhǎng)等挑戰(zhàn)。

2016年,中科院微電子所集成電路先導(dǎo)工藝研發(fā)中心(以下簡(jiǎn)稱“先導(dǎo)中心”)團(tuán)隊(duì)提出并設(shè)計(jì)了一種“三明治”結(jié)構(gòu)的垂直場(chǎng)效應(yīng)管(vertical sandwich GAA-FETs,簡(jiǎn)稱VSAFETs,下同),并在2019年發(fā)表了首個(gè)具有自對(duì)準(zhǔn)柵極的VSAFET*;

2020年,報(bào)道了鍺硅準(zhǔn)原子層刻蝕法(qALE,下同)的研究成果*,具有各向同性、對(duì)硅選擇性等特點(diǎn)。原子層刻蝕法是一種以過(guò)氧化氫(H202)和緩沖氧化物刻蝕劑(BOEs)分別作為氧化劑和氧化物去除劑的濕法化學(xué)刻蝕工藝。SiGe的qALE具有操作簡(jiǎn)單、成本低的優(yōu)點(diǎn),適用于集成電路制造。

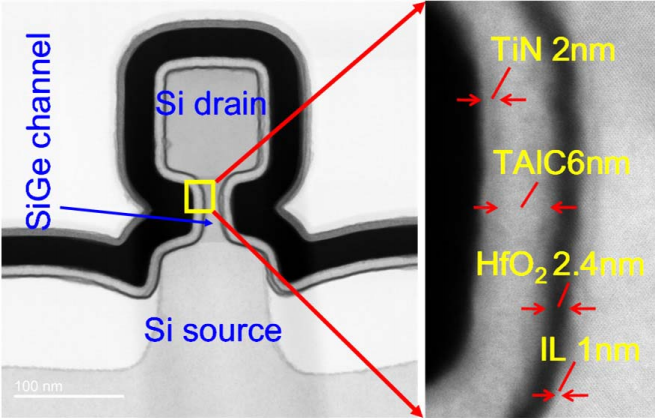

在前述研究基礎(chǔ)上,先導(dǎo)中心團(tuán)隊(duì)采用與先進(jìn)CMOS器件集成技術(shù)相兼容的工藝制備了VSAFETs,測(cè)試了器件性能,并討論比較了與器件性能相關(guān)的溝道鍺摻雜比例、金屬硅化物工藝、Si-Cap、高溫?zé)崽幚淼扔绊懸蜃樱匦抡{(diào)整了VSAFETs的閾值電壓。

相關(guān)成果以以“Vertical Sandwich GAA FETs With Self-Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process”發(fā)表于IEEE Transactions on Electron Devices六月刊,先導(dǎo)中心高級(jí)工程師張永奎為該文第一作者,與朱慧瓏研究員為共同通訊作者。

*原子層刻蝕,由自限制表面改性和選擇性去除改性層兩大步驟組成的重復(fù)循環(huán)的工藝,具有材料表面平坦、深度均勻和原子級(jí)的粗糙度可控等優(yōu)勢(shì)。

*首個(gè)具有自對(duì)準(zhǔn)柵極的VSAFET:X. Yin et al., IEEE Electron Device Lett., vol. 41, no. 1, pp. 8–11, Jan. 2020. DOI: 10.1109/LED.2019.2954537.

*qALE技術(shù)研究成果:X. Yin et al., ECS J. Solid State Sci. Technol., vol.9, no.3, Mar. 2020, Art. no.034012, DOI: 10.1149/2162-8777/AB80AE.

研究?jī)?nèi)容

先導(dǎo)中心團(tuán)隊(duì)提出并制備了具有自對(duì)準(zhǔn)高K金屬柵、且精確控制有效柵長(zhǎng)的pVSAFET器件,系統(tǒng)性研究了各向同性qALE工藝,并將其用于pVSAFET的制備;針對(duì)器件樣品,研究了VSAFET的特性,以及金屬硅化物工藝、Si-Cap、溝道Ge含量和熱處理過(guò)程等器件性能影響因素:發(fā)現(xiàn)較高的熱預(yù)算*會(huì)導(dǎo)致硼離子從漏源區(qū)擴(kuò)散到溝道,導(dǎo)致電性能差;而較低的溝道Ge含量、Si-Cap和TiAlC功函數(shù)層有助于提高晶體管閾值電壓。

*熱預(yù)算,thermal budget,表示高溫工藝下半導(dǎo)體中某些離子發(fā)生擴(kuò)散的位移長(zhǎng)度。

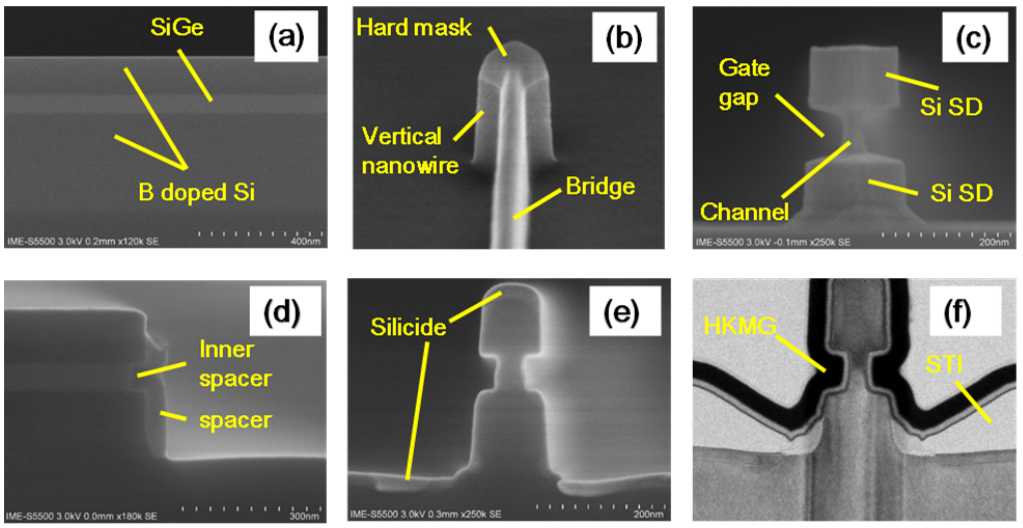

器件形貌圖(a-e為SEM圖像,f為TEM圖像):

(a)外延生長(zhǎng)后;(b)RIE后傾斜視角3D結(jié)構(gòu);(c)qALE后;

(d);隔離層成型后;(e)金屬硅化物工藝后;(f)HKMG沉積后。

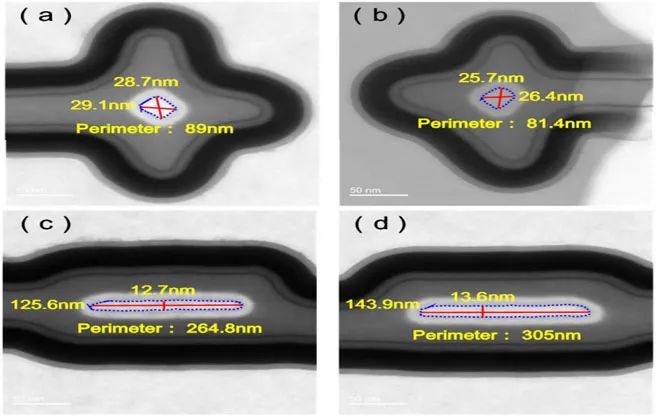

圖(1)為納米線和納米片器件TEM俯視圖圖

(2)為納米片器件TEM橫截面圖

前景展望

垂直納米環(huán)柵器件由于在垂直方向上具有更大的集成自由度和更小的面積占用,通過(guò)全新布線方式可以進(jìn)一步增加晶體管,對(duì)于2納米及以下CMOS邏輯器件和高密度DRAM存儲(chǔ)芯片的制造工藝方面具有很大的應(yīng)用前景,先導(dǎo)中心團(tuán)隊(duì)在制造工藝上持續(xù)研發(fā),逐漸探明工藝、材料等性能影響因素,加快先導(dǎo)工藝研究進(jìn)程,推動(dòng)了原型技術(shù)驗(yàn)證,豐實(shí)了產(chǎn)業(yè)端的技術(shù)儲(chǔ)備庫(kù),也祝愿產(chǎn)業(yè)鏈其他環(huán)節(jié)早日實(shí)現(xiàn)突破,提供良好的技術(shù)落地土壤,共同助力建設(shè)自主化的集成電路產(chǎn)業(yè)鏈。

團(tuán)隊(duì)介紹

朱慧瓏,中國(guó)科學(xué)院微電子研究所研究員、博士生導(dǎo)師,微電子所集成電路先導(dǎo)工藝研發(fā)中心首席科學(xué)家。1988年獲北京師范大學(xué)理論物理學(xué)博士學(xué)位,畢業(yè)后曾先后任職于美國(guó)阿貢國(guó)家實(shí)驗(yàn)室、UIUC材料研究實(shí)驗(yàn)室、DEC公司、英特爾以及IBM半導(dǎo)體研究和開(kāi)發(fā)中心。

歸國(guó)后先后擔(dān)任“22納米關(guān)鍵工藝技術(shù)先導(dǎo)研究與平臺(tái)建設(shè)”及“16-14納米基礎(chǔ)技術(shù)研究”項(xiàng)目首席專家。曾獲國(guó)家科技重大專項(xiàng)02專項(xiàng)2010年度“個(gè)人突出貢獻(xiàn)獎(jiǎng)”、IBM半導(dǎo)體研究和開(kāi)發(fā)中心2008年度杰出發(fā)明家等多項(xiàng)殊榮,獲授權(quán)中美發(fā)明專利超過(guò)300件,發(fā)表科技論文50余篇。

中國(guó)科學(xué)院微電子研究所,前身為原中國(guó)科學(xué)院109廠,成立于1958年,1986與中科院半導(dǎo)體體、計(jì)算技術(shù)所與大規(guī)模集成電路部分合并,2003年9月,正式更名為中國(guó)科學(xué)院微電子研究所。

微電子所是國(guó)內(nèi)微電子領(lǐng)域?qū)W科方向布局最完整的綜合研究與開(kāi)發(fā)機(jī)構(gòu),是國(guó)家科技重大專項(xiàng)集成電路裝備及工藝前瞻性研發(fā)牽頭組織單位,是中國(guó)科學(xué)院大學(xué)微電子學(xué)院的依托單位,是中國(guó)科學(xué)院集成電路創(chuàng)新研究院的籌建依托單位。現(xiàn)擁有2個(gè)基礎(chǔ)研究類中國(guó)科學(xué)院重點(diǎn)實(shí)驗(yàn)室、4個(gè)行業(yè)服務(wù)類研發(fā)中心、5個(gè)行業(yè)應(yīng)用類研發(fā)中心、4個(gè)核心產(chǎn)品類研發(fā)中心。

中科院微電子所集成電路先導(dǎo)工藝研發(fā)中心,國(guó)家級(jí)研發(fā)中心,擁有一條完整的8吋集成電路先導(dǎo)工藝研發(fā)線,并兼容硅基光子器件、硅基MEMS器件等集成技術(shù)研發(fā);在02專項(xiàng)支持下,先后實(shí)現(xiàn)了22納米CMOS、高 k柵介質(zhì)/金屬柵工程、16/14納米技術(shù)節(jié)點(diǎn)的FinFETs、5納米及以下納米線和堆疊納米片器件等關(guān)鍵技術(shù)的突破,科研成果首次實(shí)現(xiàn)了向國(guó)內(nèi)大型集成電路制造與裝備企業(yè)的專利技術(shù)轉(zhuǎn)移和轉(zhuǎn)化,科研水平邁入世界前列。

論文原文鏈接:

https://ieeexplore.ieee.org/document/9417199

編輯:jq

-

CMOS

+關(guān)注

關(guān)注

58文章

5724瀏覽量

235707 -

靜電

+關(guān)注

關(guān)注

1文章

507瀏覽量

36418 -

晶體管

+關(guān)注

關(guān)注

77文章

9707瀏覽量

138496

原文標(biāo)題:科研前線 | 翻轉(zhuǎn)90°的電子世界,微電子所新型GAA結(jié)構(gòu)研究獲進(jìn)展

文章出處:【微信號(hào):ICxpjm,微信公眾號(hào):芯片揭秘】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FF將發(fā)布FX品牌最新進(jìn)展

揭秘超以太網(wǎng)聯(lián)盟(UEC)1.0 規(guī)范最新進(jìn)展(2024Q4)

Qorvo在射頻和電源管理領(lǐng)域的最新進(jìn)展

小鵬汽車圖靈芯片及L4自動(dòng)駕駛新進(jìn)展

芯片和封裝級(jí)互連技術(shù)的最新進(jìn)展

方正微電子:2025年將實(shí)現(xiàn)16.8萬(wàn)片/年車規(guī)SiC MOS產(chǎn)能

高燃回顧|第三屆OpenHarmony技術(shù)大會(huì)精彩瞬間

5G新通話技術(shù)取得新進(jìn)展

廣東的5G-A、信號(hào)升格和低空經(jīng)濟(jì),又有新進(jìn)展!

百度首席技術(shù)官王海峰解讀文心大模型的關(guān)鍵技術(shù)和最新進(jìn)展

一種基于3D螺旋熱電Bi?Te?薄膜的柔性復(fù)合雙參數(shù)溫度-壓力傳感器

從原子到超級(jí)計(jì)算機(jī):NVIDIA與合作伙伴擴(kuò)展量子計(jì)算應(yīng)用

四個(gè)50億+,多個(gè)半導(dǎo)體項(xiàng)目最新進(jìn)展!

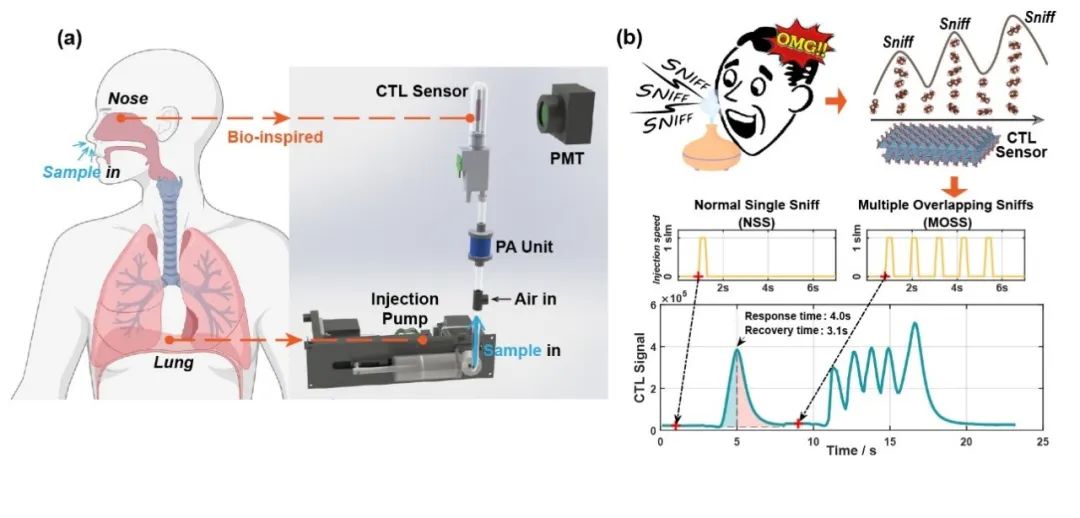

清華大學(xué)在電子鼻傳感器仿生嗅聞方向取得新進(jìn)展

淺談垂直納米環(huán)柵器件領(lǐng)域獲得的最新進(jìn)展

淺談垂直納米環(huán)柵器件領(lǐng)域獲得的最新進(jìn)展

評(píng)論