作者:包莉娜,周立豐,王匡,張明

數字衛星接收芯片(DVB_s)是準基帶采樣變換到MPEG-2碼流的完全解決方案的集成芯片?主要用于衛星傳輸的數字電視?數字語音的壓縮編碼的數字解調與信道解碼?此傳輸系統基于前向糾錯編碼(FEC)技術和QPSK調制技術,可保證傳輸業務的可靠性?

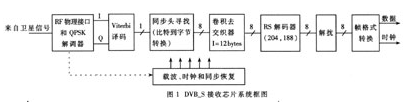

DVB-S系統功能模塊如圖1所示?包括物理接口?QPSK解調?Viterbi譯碼?同步頭尋找?去交織?RS解碼?解擾以及幀格式轉換?經過幀格式轉換后的數據稱為TS流,輸出的時鐘為占空比近似為1:1的均勻時鐘?TS數據和時鐘送給解碼芯片進行信源解碼?

1 幀格式轉換

幀格式轉換位于信道傳輸的最前端(或最末端),完成信道傳輸與信源MPEG-2編(解)碼的相應數據格式的轉換以及產生相應的時鐘?在發送端,該部分將信源MPEG-2的數據包格式轉換成信道傳輸的數據包格式,并產生信道傳輸編碼部分的時鐘?相應地,接收端部分將信道傳輸的數據包格式轉換成信源MPEG-2的包格式,同時也產生信源MPEG-2的時鐘?

1.1 進行數據格式轉換的原因

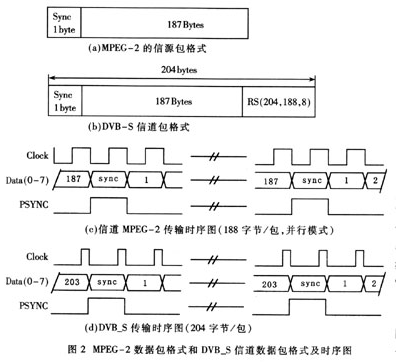

進行數據格式轉換是由于DVB-S信道幀格式與MPEG-2的信源幀格式不同?信源MPEG-2編(解)碼數據包格式是按段組織的,每一個數據段包括1個字節的段同步和187個字節的數據,這種幀結構稱為信源數據包格式?而本方案信道傳輸的RS編(解)碼是按每個段進行的,即(204,188,16)碼,也就是每段187個字節信息數據外又增加16個糾錯校驗位? MPEG-2數據包格式和DVB信道數據包格式及時序如圖2所示?

這里主要討論接收端的格式轉換,即將DVB_S信道格式轉換為MPEG-2信源格式?接收端數據格式轉換主要包括兩部分:(1)去掉校驗字節;(2)將時鐘變為占空比1?1?去除校驗字節子部分將由RS編譯碼引入的冗余校驗字節去掉,使每包的數據恢復為188字節?為防止信號畸變,保證數據正確地采樣,時鐘占空比應展寬為1:1?目前市場上的解碼芯片支持并行和串行兩種模式?以上討論的并行模式輸出(以字節形式輸出)?串行模式輸出以比特形式輸出?

1.2 幀格式轉換設計

1.2.1 并行模式

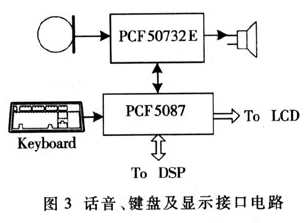

該部分將去除由DVB-S的RS編碼引入的冗余校驗字節,使每包的數據恢復為MPEG-2格式的188字節?其結構框圖如圖3所示?其核心部分為數據緩沖區的設計和讀時鐘的產生?

(1)數據緩沖區

從信道數據包格式和信源包格式可以看出,相對信源包而言,信道包每包多出了16個RS碼校驗字節?信道數據按如下規則寫入緩沖區,讀端也按照一定規則讀出數據:16個字節的RS校驗碼不寫入緩沖區,其他數據按地址順序寫入緩沖區;在讀出時,按照順序讀出緩沖區的內容,每幀為188字節的數據?其中數據寫入緩沖區時,使用信道的時鐘,而從緩沖區讀出數據時,使用信源時鐘? 為了保證讀出數據的正確性,只能讀已經寫入的數據,也就是讀操作滯后于寫操作?這里一個存儲單元為1個字節 ?設計時采用SRAM作為數據緩沖區?

(2)讀時鐘以及信源時鐘的產生

參考時鐘的產生

為了減少整個系統的復雜度(主要為減少芯片外圍電路),前級時鐘恢復(Clock Recovery)模塊采用了內插算法,引起了符號時鐘周期的不確定性,進一步導致了字節時鐘周期的不確定性,即傳輸給幀格式轉換模塊的字節時鐘是很不均勻的?

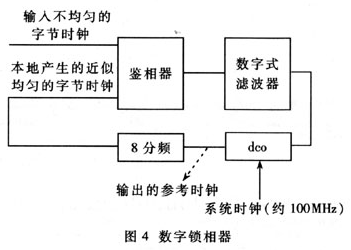

為了得到近似均勻的字節時鐘,幀格式轉換模塊采用數字鎖相法產生一個近似均勻的參考時鐘,如圖4所示?

圖4中,本地產生的近似均勻的字節時鐘頻率與輸入的不均勻字節時鐘的頻率保持一致,而輸出的參考時鐘頻率是輸入字節時鐘的8倍,且近似均勻?之所以要8分頻而不是2分頻或是4分頻,主要考慮到在DVB_S系統中符號頻率是2MHz-45MHz,折算到字節頻率為0.25MHz-5.5125MHz(如果Viterbi譯碼的刪節模式是1/2,字節頻率=符號頻率×1/4×Viterbi譯碼的刪節模式),當符號頻率很低時,如采用2分頻或4分頻數字鎖相器穩定較慢,而8分頻符合設計要求?

讀時鐘產生以及信源時鐘的生成

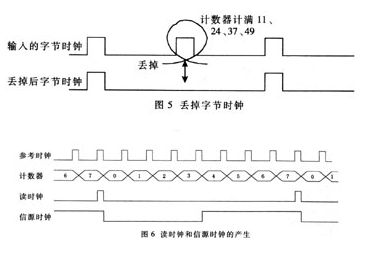

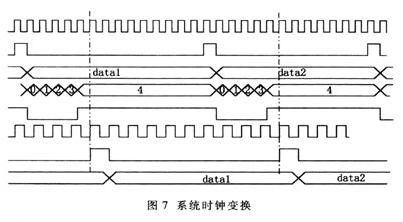

由于信源格式的每個包只有188字節,因此首先把信道格式的每包204字節使能去掉16個,采用丟時鐘的方法,在204中丟掉16次使能,即51中丟掉4次?故采用一個51計數器?當計數到11?24?37?49時丟掉輸入的字節時鐘,得到丟掉后的每包只有188個字節時鐘(如圖5)?把丟掉后的字節時鐘傳輸給上面的參考時鐘產生模塊,得到較均勻的參考時鐘? 由新的較均勻的參考時鐘8分頻即可得到較均勻的讀時鐘(每包188個),以及信源時鐘(占空比約為1:1)?在設計時用一個模8計數器即可?如圖6,讀時鐘和信源時鐘是對齊的?

1.2.2 串行模式

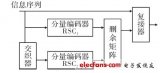

根據解碼芯片的要求,串行模式的輸出工作在60MHz系統時鐘上,而本設計中的數字衛星信道接收芯片工作在90MHz系統時鐘上?因此首先需要系統時鐘的變換,然后進行并行模式的處理,最后再并/串變換?

系統時鐘的變換是關鍵,其設計可分為三步,如圖7所示?

(1)把工作在90MHz上的字節時鐘展寬,這時可用一個3bit的計數器實現,Verilog代碼如下:

always @ (posedge sys_clk)

begin

if(rst | byt_clk)

sys_cnt 《= 3'd0;?

else if(~sys_cnt[2])?

sys_cnt 《= sys_cnt + 3'd1;?

end

assign 展寬的字節時鐘 = sys_cnt[2]??

(2)用60MHz的系統時鐘采樣展寬的字節時鐘的上跳沿,產生工作在60MHz上的字節時鐘? (3)以60MHz的系統時鐘為采樣時鐘,工作在60MHz上的字節時鐘為使能信號,采樣輸入的數據,得到工作在60MHz上的數據?這樣,就不會出現多采或者漏采現象?

然后把60MHz的系統時鐘?工作在60MHz上的字節時鐘及數據送給并行模塊?從并行模塊出來的是信源的字節時鐘,其每一個字節時鐘周期中均有8個參考時鐘,因此可以把這8個參考時鐘作為串行輸出的比特時鐘,每一個字節數據在一個字節時鐘周期內變為8個比特的數據,按照比特時鐘輸出?

2 ASIC實現

選擇的硬件描述語言是Verilog HDL綜合庫,synthesis library 選用UMC 0.18μm工藝?綜合之后此模塊的總面積為6000門左右?此方案已經應用到DVB-S芯片的設計中,并且在FPGA上已經調試成功?

本文所講述的幀格式轉換處于DVB-S芯片中的最后一個模塊,其主要功能是將數據和時鐘從信道格式轉變為信源格式?其輸出連到解碼芯片,解碼芯片能否正常工作此模塊起著非常關鍵的作用?

責任編輯:gt

-

芯片

+關注

關注

455文章

50851瀏覽量

423904 -

電視

+關注

關注

15文章

2486瀏覽量

75656 -

衛星

+關注

關注

18文章

1716瀏覽量

67070

發布評論請先 登錄

相關推薦

DVB-C標準及相關測量技術

DVB開發技術基礎培訓

DVB-S/DVB-S2信號發生器 (DVB-S/S2 Si

GX1101是國產首款支持DVB-S標準的衛星數字電視信道解

GX3001 面向DVB-C/DVB-S/DVB-T市場推出

GX3002 面向DVB-C/DVB-S/DVB-T推出的高

GX6102 面向DVB-S推出的高性能衛星數字電視接收與解

Turbo碼在DVB-S系統中的應用研究

采用AD9789與FPGA相結合實現全數字QPSK射頻調制的方案

基于FEC技術和QPSK調制技術實現DVB-S芯片的幀格式轉換設計

基于FEC技術和QPSK調制技術實現DVB-S芯片的幀格式轉換設計

評論