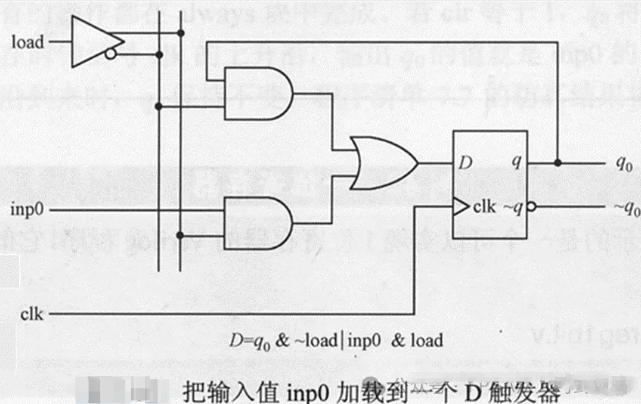

對于寄存器,如果沒有明確指定其初始值,Vivado會根據(jù)其類型(FDCE/FDRE/FDPE/FDRE)設(shè)定合適的初始值。有些工程師喜歡使用復(fù)位信號,對所有的寄存器進行上電復(fù)位,使其在處理數(shù)據(jù)之前達(dá)到期望初始狀態(tài)。但這會有一個不利之處就是復(fù)位信號的扇出很大,從而消耗了大量的布線資源,甚至造成布線擁塞。那么能不能讓寄存器在上電之后不用通過復(fù)位就輸出期望值呢?答案是肯定的。

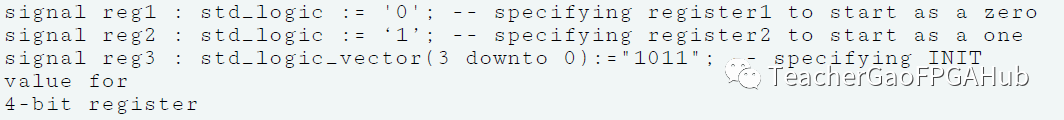

Xilinx也建議對于同步元件,最好設(shè)定其初始值。這里我們以最常用的寄存器為例。如果使用的是VHDL,可以采用下面的方法設(shè)定寄存器初始值,如下圖所示。

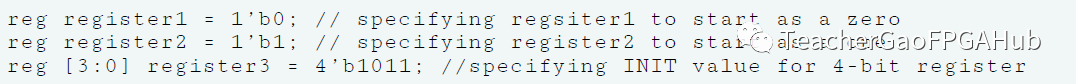

如果使用的是Verilog,可以采用下面的方法設(shè)定寄存器初始值,如下圖所示。

此外,對于Verilog,也可通過initial設(shè)定初始值,如下圖所示。

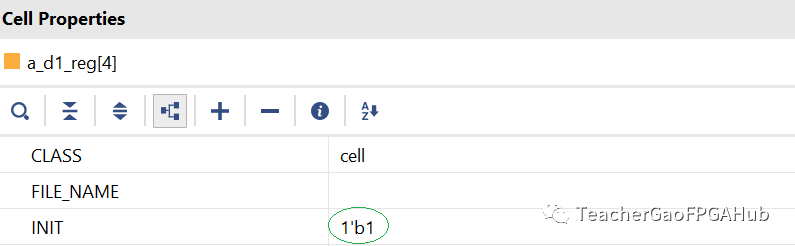

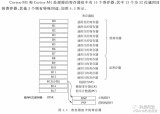

采用這種方法的好處是:綜合工具是支持的,這樣生成bit文件時這些初始值會被寫入配置文件中,上電即可生效,避免了使用復(fù)位造成的扇出過大;同時在仿真時,也能跟實際業(yè)務(wù)相匹配。 為了驗證這個方法是否生效,只需要打開綜合后的.dcp,找到相應(yīng)的寄存器,在其Property窗口中查看屬性INIT的值,如下圖所示。

編輯:jq

-

寄存器

+關(guān)注

關(guān)注

31文章

5343瀏覽量

120427 -

上電復(fù)位

+關(guān)注

關(guān)注

1文章

39瀏覽量

15807 -

init

+關(guān)注

關(guān)注

0文章

16瀏覽量

3433

原文標(biāo)題:如何設(shè)定寄存器的初始值?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ads124s08把AIN0端口接入的采集電壓斷開或者接通,芯片的寄存器所有配置值都變成默認(rèn)的初始值了,為什么?

AFE4404沒有接外部時鐘,4404寄存器的為初始值,能夠通過IIC修改寄存器值嗎?

使用ADS1256的8個Single-Ended輸入去采集壓力傳感器數(shù)據(jù),壓力傳感器空載時AIN0-AIN7 8個通道初始值不是直線,為什么?

Modbus協(xié)議的讀取保持寄存器值

TAS5733L按照初始化的寄存器配置,播放音樂無聲是怎么回事?

寄存器是什么意思?寄存器是如何構(gòu)成的?

寄存器尋址的實現(xiàn)方式

寄存器分為基本寄存器和什么兩種

干貨滿滿:ARM的內(nèi)核寄存器講解

loop指令執(zhí)行時,隱含的寄存器是

CPU的6個主要寄存器

TC275在內(nèi)存分段預(yù)警處理之后,設(shè)置的全局變量初始值不正確怎么解決?

個人對STM32 SysTick的總結(jié)(寄存器操作)

教你們怎么去設(shè)定寄存器的初始值

教你們怎么去設(shè)定寄存器的初始值

評論