數(shù)字信號(hào)處理就是用一些數(shù)學(xué)算法對(duì)數(shù)字信號(hào)進(jìn)行分析、變換、綜合、估值和識(shí)別。作為數(shù)字信號(hào)處理核心和標(biāo)志的數(shù)字信號(hào)處理器(DSP)芯片自問(wèn)世以來(lái)得到了快速的發(fā)展,廣泛應(yīng)用于通信系統(tǒng)、圖形/圖像處理、雷達(dá)聲納、醫(yī)學(xué)信號(hào)處理等實(shí)時(shí)信號(hào)處理領(lǐng)域。隨著人們對(duì)實(shí)時(shí)信號(hào)處理要求的不斷提高和大規(guī)模集成電路技術(shù)的迅速發(fā)展,數(shù)字信號(hào)處理器也發(fā)生著日新月異的變革。美國(guó)AD公司,繼16 b定點(diǎn)ADSP21xx和32 b浮點(diǎn)ADSP21xxx系列之后推出的ADSP Tiger SHARC系列處理器,是基于AD2106x的下一代高性能芯片。本文著重介紹Tig er SHARC系列中TS101S芯片的性能及結(jié)構(gòu)特點(diǎn),并將其應(yīng)用在雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)中。

1 Tiger SHARC DSP

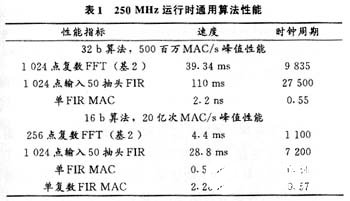

Tiger SHARC DSP是一款高性能的靜態(tài)超標(biāo)量數(shù)字信號(hào)處理器,該處理器專(zhuān)為大的信號(hào)處理和通信任務(wù)而在結(jié)構(gòu)上進(jìn)行了優(yōu)化。由于該處理器將非常寬的存儲(chǔ)帶寬和雙運(yùn)算模塊結(jié)合在一起,從而建立了數(shù)字信號(hào)處理器性能的新標(biāo)準(zhǔn)。Tiger SHARC 靜態(tài)超標(biāo)量結(jié)構(gòu)使DSP 每周期能夠執(zhí)行多達(dá)4 條指令、24 個(gè)16 b定點(diǎn)運(yùn)算和6個(gè)浮點(diǎn)運(yùn)算。該Tiger SHARC DSP 器件在3條相互獨(dú)立的128 b寬度的內(nèi)部數(shù)據(jù)總線中,每條可連接3個(gè)2 Mb 內(nèi)部存儲(chǔ)器 中的1個(gè),并可提供4個(gè)字的數(shù)據(jù)、指令及I/O訪問(wèn)和12 GB/s的內(nèi)部存儲(chǔ)器帶寬。運(yùn)行在250 MHz時(shí),ADSPTS101S 的內(nèi)核指令周期為4 ns,同時(shí)可以提供20億次 的40 b MAC運(yùn)算或者500萬(wàn)次80 b MAC運(yùn)算。

Tiger SHARC DSP器件的主要性能如下:

(1)最高運(yùn)行速度為300 MHz,指令周期為3.3 ns。

(2)帶有6 Mb片內(nèi)SRAM,分為了3個(gè)2 Mb的存儲(chǔ)塊M0,M1和M2,每一個(gè)存儲(chǔ)塊都能夠 單獨(dú)存儲(chǔ)程序、數(shù)據(jù)或同時(shí)存儲(chǔ)程序和數(shù)據(jù)。

(3)帶有雙運(yùn)算模塊,每個(gè)運(yùn)算塊有1個(gè)64 b ALU,1個(gè)乘法器,1個(gè)64 b移位器和1個(gè) 由32個(gè)寄存器構(gòu)成的寄存器組,可執(zhí)行定點(diǎn)和浮點(diǎn)的算術(shù)邏輯等通用運(yùn)算。

(4)3條內(nèi)部地址/數(shù)據(jù)總線,每條總線都連接到3個(gè)內(nèi)部存儲(chǔ)器塊中的1個(gè)。3條總線都 是128 b寬,可以在任一周期使用任一條總線傳送多達(dá)4條指令或4個(gè)對(duì)齊的數(shù)據(jù)。這樣TS10 1S內(nèi)核可以在任一周期并行訪問(wèn)3個(gè)存儲(chǔ)塊,1個(gè)取指令,2個(gè)訪問(wèn)數(shù)據(jù)。

(5)4個(gè)鏈路口支持點(diǎn)對(duì)點(diǎn)的高帶寬數(shù)據(jù)傳送,可通過(guò)單個(gè)鏈接口以250 Mb/s 的速率進(jìn)行 數(shù)據(jù)傳輸。4個(gè)鏈路口為處理器與處理器之間的通訊提供了一個(gè)良好的途徑,總吞吐量多達(dá) 1 Gb/s。

(6)多處理器特性,當(dāng)單個(gè)DSP芯片組成的系統(tǒng)不能滿(mǎn)足處理要求時(shí),TS101S通過(guò)外部口或鏈路口與其他TS101S相連構(gòu)成多處理器系統(tǒng)。TS101S的外部總線支持多達(dá)8個(gè)DSP外加Host處理器的并行總線連接。在構(gòu)成多處理器系統(tǒng)時(shí),處理器之間無(wú)論是采用共享總線方式,還是采用鏈路口互連方式,都不需任何外加控制,實(shí)現(xiàn)無(wú)縫連接,在并行總線上可以80 0 Mb/s的速率進(jìn)行數(shù)據(jù)傳輸。

(7)有DMA和SDRAM控制器,擁有14個(gè)DMA通道,提供了在處理器核不干預(yù)條件下的零 開(kāi)銷(xiāo)數(shù)據(jù)傳輸,SDRAM的地址、數(shù)據(jù)引腳可以與Tiger SHARC的直接相連,另外,Tiger SHAR C提供專(zhuān)用的尋址空間支持SDRAM。

TS101S的主要性能指標(biāo)如表1所示。

2 信號(hào)處理系統(tǒng)的實(shí)現(xiàn)

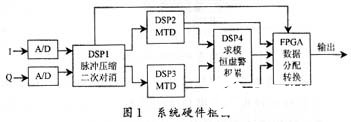

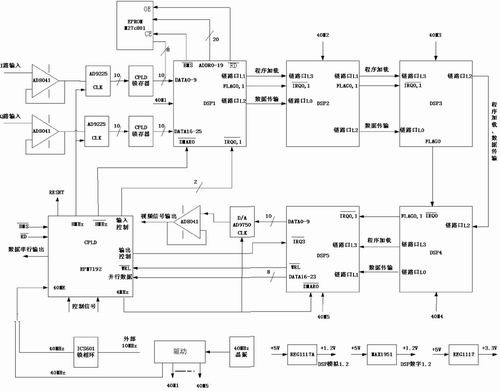

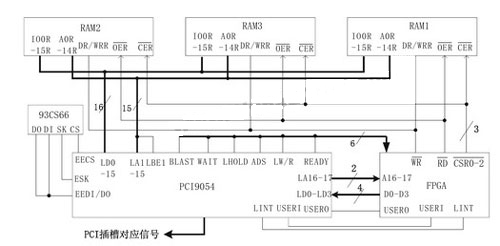

圖1所示是一個(gè)雷達(dá)信號(hào)處理系統(tǒng)的硬件框圖。為了簡(jiǎn)化系統(tǒng)硬件,減少DSP片間連線,該系統(tǒng)的4個(gè)DSP以松耦合的鏈路方式進(jìn)行連接,并共用一片FPGA。

首先由DSP1通過(guò)外部DMA方式讀入中頻解調(diào)后的I、Q路數(shù)據(jù),并由DSP1對(duì)讀入數(shù)據(jù)進(jìn)行脈沖壓縮(匹配濾波),脈沖壓縮后進(jìn)行二次對(duì)消,以消除固定雜波。設(shè)計(jì)總距離單元數(shù)為2000,需做2 048點(diǎn)復(fù)數(shù)FFT,當(dāng)2 048點(diǎn)復(fù)數(shù)FFT完成后,還必須和預(yù)先存儲(chǔ)好的匹配濾波器 系數(shù)H(k)相乘,一般需要做2 048個(gè)復(fù)數(shù)乘法,相乘結(jié)果還需做2 048點(diǎn)復(fù)數(shù)IFFT以獲得 脈沖壓縮結(jié)果。Tiger SHARC DSP做2 048點(diǎn)復(fù)數(shù)FFT和IFFT大約需要200 μs(工作在250 MHz ),利用Tiger SHARC DSP的雙運(yùn)算塊和單指令多數(shù)據(jù)(SIMD)特點(diǎn)同時(shí)進(jìn)行兩個(gè)距離單元的復(fù) 數(shù)乘法,完成2 048個(gè)復(fù)數(shù)乘法僅需25 μs。二次對(duì)消對(duì)于每個(gè)距離單元都需要做2次減法和1次加法,2 000個(gè)距離單元的二次對(duì)消大約需要50 μs。DSP完成上述運(yùn)算大約要300 μs。

DSP2和DSP3完成動(dòng)目標(biāo)檢測(cè)功能。在使用窄帶多譜勒濾波器組時(shí),為了降低旁瓣可在系統(tǒng) 中采用滑窗加權(quán)FFT的方法,在距離單元數(shù)為2 000時(shí)大約需要640 μs處理時(shí)間,用2片DSP 并行處理即可實(shí)現(xiàn)。

求模采用近似算法,每個(gè)距離單元只用做1次比較和1次加法。恒虛警處理先進(jìn)行選大單 元平均運(yùn)算,再對(duì)被檢單元進(jìn)行比較判決,從而降低

虛警率。積累采用簡(jiǎn)單累加求平均的方 式完成。以上3種運(yùn)算由DSP4實(shí)現(xiàn)。

FPGA在電路中起輔助作用,在數(shù)據(jù)量較大的情況下進(jìn)行數(shù)據(jù)寄存和分配,同時(shí)也能擔(dān)負(fù)DS P4的工作,如果需要的話(huà)還能進(jìn)行數(shù)據(jù)的并/串轉(zhuǎn)換工作。

3 Tiger SHARC DSP的使用

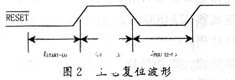

為保證Tiger SHARC DSP能正常工作,上電復(fù)位信號(hào)的設(shè)計(jì)非常重要。上電復(fù)位波形要求 如圖2所示,但應(yīng)注意tSTARTLO在供電穩(wěn)定之后必須至少大于1 ms,tPULSE1HI必須大于50個(gè)系統(tǒng)時(shí)鐘周期,同時(shí)小于100個(gè)系統(tǒng)時(shí)鐘周期,tPULSE2LO必須大于100個(gè)系統(tǒng)時(shí)鐘周期,在DSP上電后,如需正常復(fù)位,其低電平持續(xù)時(shí)間必須大于100個(gè)系統(tǒng)時(shí)鐘周期。

Tiger SHARC DSP有3個(gè)電源,其中數(shù)字3.3 V為I/O供電,數(shù)字1.2 V為DSP內(nèi)核供電,模擬1.2 V為內(nèi)部鎖相環(huán)和倍頻電路供電。Tiger SHARC DSP要求數(shù)字3.3 V和1.2 V應(yīng)同時(shí)上電。若無(wú)法嚴(yán)格同步,則應(yīng)保證內(nèi)核電源1.2 V先上電,I/O電源3.3 V后上電。本系統(tǒng)在數(shù)字3.3 V輸入端并聯(lián)了一個(gè)大電容,而在數(shù)字1.2 V輸入端并聯(lián)了一個(gè)小電容,其目的就是為了保證3.3 V充電時(shí)間大于1.2 V充電時(shí)間,以便很好地解決電源供電的先后問(wèn)題。

Tiger SHARC DSP內(nèi)核最大電流為1.277 A,該電流是DSP進(jìn)行單指令多數(shù)據(jù)(SIMD) 方式下,4個(gè)16 b定點(diǎn)字乘加與2個(gè)4字讀取并行操作以及進(jìn)行由外部口到內(nèi)部存儲(chǔ)器DMA操作所需的電流。實(shí)際上,DSP 內(nèi)核電流大小還和內(nèi)核工作頻率有關(guān),因此,供給DSP 內(nèi)核電流可根據(jù)不同的并行處理任務(wù)和內(nèi)核工作頻率來(lái)確定,最大內(nèi)核功耗為1.534 W。外部口的功耗(對(duì)VDDIO)主要是輸出引腳(例如數(shù)據(jù)線的某個(gè)位由高到低,或由低到高)轉(zhuǎn)換的功 率消耗,而且該功耗與系統(tǒng)無(wú)關(guān),一般為0.45 W。由此可估算出該信號(hào)處理系統(tǒng)的功耗大 約為10 W。

4 結(jié)語(yǔ)

本文介紹了多片Tiger SHARC DSP在雷達(dá)信號(hào)處理系統(tǒng)中的應(yīng)用,該系統(tǒng)充分利用了TS101 S高速的運(yùn)算能力及數(shù)據(jù)吞吐量,對(duì)不同的距離單元段進(jìn)行并行處理。文中分析了系統(tǒng)的運(yùn) 算量、所需時(shí)間以及完成算法所需的DSP數(shù),并且討論了DSP應(yīng)用過(guò)程中需注意的幾個(gè)問(wèn)題, 具有很強(qiáng)的實(shí)用性。該系統(tǒng)外接計(jì)算機(jī)總線,預(yù)留鏈路口,按信號(hào)處理通用板的模式設(shè)計(jì), 也就是說(shuō),當(dāng)單板資源不夠時(shí),通過(guò)增加板子的數(shù)量就可成倍地增加信號(hào)處理能力,這對(duì)于 各種新型號(hào)雷達(dá)的開(kāi)發(fā)研制起到了事半功倍的作用,大大縮短了研發(fā)周期,具有廣泛的 應(yīng)用價(jià)值。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19348瀏覽量

230267 -

dsp

+關(guān)注

關(guān)注

554文章

8030瀏覽量

349359 -

雷達(dá)

+關(guān)注

關(guān)注

50文章

2949瀏覽量

117676

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

哪位有ADSP TS101S 芯片的Cadence原理圖封裝啊 跪求 ..

一種基于TS101的SAR回波信號(hào)模擬器設(shè)計(jì)

如何采用ADSP-TS101實(shí)現(xiàn)高速信號(hào)處理系統(tǒng)的設(shè)計(jì)?

ICS554在軟件高頻雷達(dá)上的接口實(shí)現(xiàn)

基于DSP和DSP/BIOS的實(shí)時(shí)雷達(dá)信號(hào)采集與處理系統(tǒng)

基于ADSP-TS101S的多芯片數(shù)字信號(hào)處理系統(tǒng)的實(shí)現(xiàn)方案

采用ADSP-TS201S芯片的圖像采集處理系統(tǒng)設(shè)計(jì)

多片TS101S的加載引導(dǎo)設(shè)計(jì)分析及實(shí)現(xiàn)

一種雷達(dá)組網(wǎng)融合實(shí)時(shí)處理系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

基于TS101的圖像采集和處理系統(tǒng)設(shè)計(jì)

雷達(dá)通用信號(hào)處理系統(tǒng)的實(shí)現(xiàn)與應(yīng)用

基于FPGA的雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)

地面脈沖多普勒雷達(dá)信號(hào)處理系統(tǒng)方案

采用FPGA與高性能DSP芯片的雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)

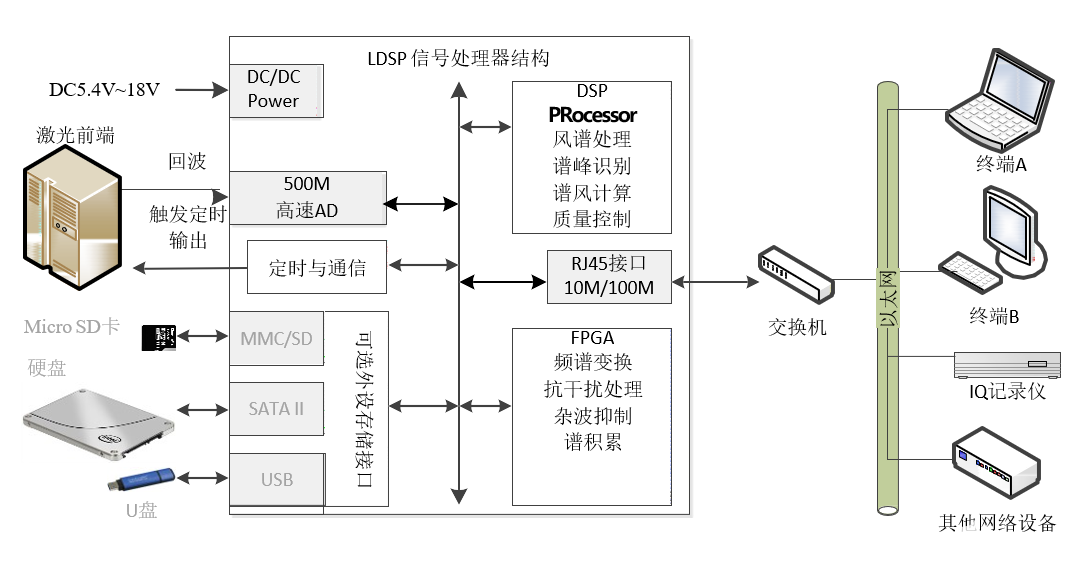

激光雷達(dá)信號(hào)處理系統(tǒng)

基于TS101S芯片實(shí)現(xiàn)雷達(dá)信號(hào)處理系統(tǒng)的應(yīng)用設(shè)計(jì)

基于TS101S芯片實(shí)現(xiàn)雷達(dá)信號(hào)處理系統(tǒng)的應(yīng)用設(shè)計(jì)

評(píng)論