作者:張蓉,曲晶,王志華,柳春笙,陳國慶

1 數字音頻廣播(DAB)發射系統及信道編碼器

DAB是繼調幅和調頻廣播之后的第三代廣播體系。與模擬廣播相比它不僅可以提供高質量的聲音信號(CD音質),也可以提供數據、圖像等多種其他附加服務。它可以保證在高速移動接收時的聲音質量,具有很強的抗干擾能力,在同樣的頻帶寬度和環境下,DAB可以提供高質量的多種多樣的廣播節目。

DAB的發射系統主要包括處于節目提供商位置的信源編碼器,處于廣播臺演播室位置的復接器和處于發射機內部的COFDM(編碼正交頻分復用)編碼調制器。其中COFDM可分為信道編碼、OFDM調制和數字上變頻。本文主要討論使用FLEX10K系列FPGA來實現信道編碼的功能。

DAB的信道編碼部分主要包括能量擴散、卷積編碼和刪除、時間交織等,輸入為來自復接器的ETI(業務群傳輸接口Ensemble Transport Interface)幀,輸出為DAB傳輸幀。能量擴散的作用是通過對二進制序列的隨機化處理使頻譜擴散,減少連‘0’和連‘1’的出現,以保證接收端比特按時恢復。對于信號的傳輸來說,由于卷積編碼引入了大量的冗余比特,因此DAB的信道編碼采用刪除型的卷積編碼。DAB發射機使用時間交織技術來糾正突發性的塊差錯。它按照既定的規則打亂數據排列順序,使得信道中成塊的錯誤分散在不同幀中,再結合卷積編碼的點糾錯能力,可以使接收機能夠糾正移動傳輸中經常出現的塊差錯。

2 FLEX10K系列特點

FLEX10K系列是Altera公司生產的一種嵌入式可編程邏輯器件PLD-Programmable Logic Device 。Flex可更改邏輯單元陣列采用可重構的CMOS SRAM單元,其結構集成了實現通用多功能門陣列所需的全部特征。FLEX10K系列器件容量可達25萬門,能夠高速度、高性能地將整個數字系統集成于單個器件中。FLEX10K系列的高密度和易于在設計中實現復雜宏函數與存儲器,使其可以適應系統級設計的要求。

FLEX10K器件可通過Altera的MAX PLUS II 系統來開發,它具有強大的功能,支持原理圖、硬件描述語言(VHDL,AHDL,verilogHDL)等多種輸入方式。用FPGA來實現DAB信道編碼器,大大簡化了系統結構。而且VHDL描述語言的使用縮短了開發時間,增強了系統的可讀性,便于后續產品的升級。如果想改變軟件設計,只要修改程序、重新編譯、下載即可,十分方便。即使要改變硬件設計,也可通過重新分配FPGA管腳實現,不需大規模改動原有的硬件。從信道編碼器的的功能特點看,大部分是比特操作。如果使用DSP或單片機,每個指令周期只能處理一個字節中的一比特,效率相當低。而FPGA可以對多個比特同時并行操作,大大提高了處理效率。由于FPGA的最高工作頻率在100MHz以上,所以可以通過提高FPGA的工作頻率來提高其處理數據的速度。

本設計中所用的FLEX10K100A FPGA是FLEX10K系列中的一種,它的等效門數為10萬門,內建24K字節RAM,可用的I/O管腳達到189個,核心電壓3.3V,支持5V輸入輸出。設計中采用原理圖和VHDL語言混合輸入的方法。

3 用FPGA實現信道編碼功能

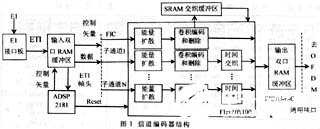

DAB信道編碼技術包括ETI解復接、能量擴散、卷積編碼和刪除和時間交織。其中ETI解復接和系統控制由一片DSP ADSP2181來實現,核心部分能量擴散、卷積編碼刪除時間交織全部由一片FLEX10K100A實現。一個ETI幀中主要包括幀頭信息本幀及幀內各子通道的相關信息和主業務流數據MST包括音頻數據碼流和快速數據通道(FIC)。圖1是信道編碼的硬件實現示意圖。

來自復接器的碼流(ETI)經E1接口板,解出ETI幀,存入輸入雙口RAM緩沖區。在每幀(24ms)開始時,控制器2181從輸入緩沖區讀入ETI幀并根據幀頭信息計算得一組控制矢量,并將其寫回到輸入緩沖區,然后啟動FPGA。FPGA首先讀入控制矢量,然后根據其描述讀入ETI幀中MST域的各子通道數據并進行能量擴散、卷積編碼和刪除、時間交織的處理,結果輸出到輸出緩沖區給OFDM調制器。其中SRAM交織緩沖區是用來存放用于交織的6幀數據的。

信道編碼的控制器由adsp2181實現,控制整個信道編碼過程的全部動作,其中主要包括啟動編碼模塊FPGA開始編碼、控制FPGA從外部存儲器的相應地址讀取數據、為編碼模塊提供進行卷積編碼所需的全部參數、為編碼后數據提供存儲地址等。

下面詳細介紹用FPGA實現信道編碼的過程。當DSP計算完控制信息后,啟動FPGA。FPGA首先讀入計算所得控制矢量的前幾位幀特征字節,根據這幾個字節確定了包括FIC通道在內的子通道個數和輸入數據的起始地址,然后分別讀入各子通道特征字節,并根據其描述對各子通道進行處理。

3.1 能量擴散

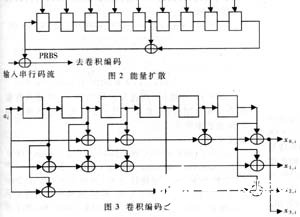

能量擴散采用原理圖輸入的方法,由9個D觸發器和邏輯門實現。在FPGA中,首先按字節讀入數據,然后進行并/串轉換,將串行輸入碼流與生成多項式為 Px=x9+x5+1、初始狀態全‘1’的偽隨機比特序列(PRBS)模二相加處理的順序是串行輸入的第0比特與PRBS序列的第0比特異或,就得到能量擴散的輸出碼流。將輸出的串行碼流送入卷積編碼器。圖2是能量擴散的實現原理圖。

3.2 卷積編碼

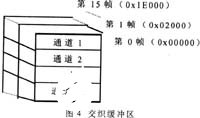

卷積編碼器也是采用原理圖輸入的方法,如圖3所示,通過移位寄存器和其不同抽頭的組合來實現的。[/td][/tr][tr][td=2,1]寄存器的初始化狀態為全‘0’,每輸入一個比特會產生4個比特的輸出。當有效數據送完時,還要繼續送入6個‘0’以使全部寄存器清零。若輸入長度I的序列,則輸出序列為。輸出序列也可表示為U=(u0 u1 u2?…?u4i+23?其中ui=x(i=0,1,2,...,4I+23),其中R、Q分別是i/4的余數和商。

3.3 卷積編碼的刪除

卷積編碼輸出的前4I個比特被分成連續的比特塊,每塊128比特。每塊又被分為32比特的4個子塊,這4個子塊使用同一個刪除模式,刪除模式由PI決定,表1是刪除模式表的一部分。卷積編碼的輸出與刪除模式表中的刪除矢量V相與,剩下的比特壓入一個堆棧中。當16比特的堆棧中堆積的比特數>8時,編碼器將刪除結果按字節輸出到16幀長度的交織緩沖區暫存。原始數據的讀入、能量擴散、卷積編碼和刪除是同時進行的。當一個子通道(或FIC)的數據讀完時,能量擴散也同時停止,但編碼和刪除并不停止,還要進行最后24比特的編碼和刪除,這24比特使用固定的刪除矢量VT=(1100 1100 1100 1100 1100 1100)進行刪除。對于有填充字節(Pad)的還要加入填充,最后輸出一個字節。

PI是根據輸入碼流的比特率、保護級(P)和保護方式(EEP/UEP)決定的。在UEP(非平衡差錯保護)中,把整個幀的碼流(某個子通道)分為3或4塊(L1~L4),然后查表即得到相應塊的PI和填充比特數。表2是此保護級模式表的一部分。對于EEP(平衡差錯保護),有A和B兩類保護模式表,分別對應輸入碼率是8Kbits/s的整數倍和32Kbits/s的整數倍,每幀中一個子通道分為2塊。一般的刪除處理是通過查表進行的,而這里查表的工作由控制器完成,查表結果存在控制矢量字節中。FPGA可直接根據結果編碼,有效降低了FPGA的復雜度。

3.4 時間交織

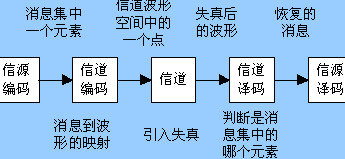

交織開始時,FPGA已經將卷積編碼刪除的結果順序地寫入交織緩沖區,然后按照交織規則亂序地讀出數據,完成交織深度為16幀的時間交織。這個緩沖區是一片容量128K字節的SRAM,分為16個8K的塊,每塊用來存儲一幀的卷積編碼結果。SRAM的地址組織如圖4(括號內是各幀的起始地址)。

表3所示的交織規則對應于128K的交織緩沖區,其中r是輸入幀的序號,r'是輸出幀的序號,i表示比特的序號,R(i/16)表示i除以16的余數,r‘(r i)表示輸出第r’幀第i比特應該對應輸出第r幀第i比特。Ram_addr表示在交織緩沖區中此幀的起始地址。

為符合DAB發射系統下級OFDM調制器需要的碼元格式,交織后的結果按字節寫入輸出雙口RAM緩沖區時要符合傳輸幀的數據結構。根據DAB傳輸幀的要求,這里的輸出緩沖區可容納4個邏輯幀的數據,其片選邏輯也是每96ms變化一次,輸出RAM緩沖區內的數據結構如圖5。

如上所述,DAB信道編碼器可由單片FLEX10K系列FPGA(adsp2181做控制器)完全實現。這一方法易于實現、工作穩定、速度快、易于升級,可以作為今后集成專用ASIC芯片研制的核心技術基礎。

責任編輯:gt

-

FPGA

+關注

關注

1638文章

21861瀏覽量

610063 -

嵌入式

+關注

關注

5115文章

19355瀏覽量

311588 -

存儲器

+關注

關注

38文章

7579瀏覽量

165425

發布評論請先 登錄

相關推薦

信道編碼——引言

跳頻通信系統信道編碼的DSP實現

基于FPGA的數字音頻廣播信道編碼器的實現

Real BCH的聯合信源信道編碼系統構建

遙測同步和信道編碼系統及FPGA實現

帶你了解什么是信道編碼

信道編碼推動著現代人類通信

如何使用FPGA實現信道編碼

評論