高速PCB設(shè)計完成后,一般都要經(jīng)過評審才會發(fā)出去做板。硬件組在評審的過程中,一般都會在各個方面給出修改的建議,比如EMC,貼片,信號完整性等方面。下面匯總一些以前PCB評審時,硬件組給出的一些修改建議。

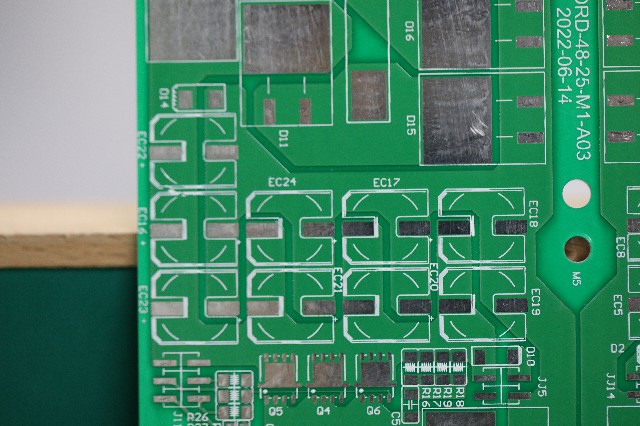

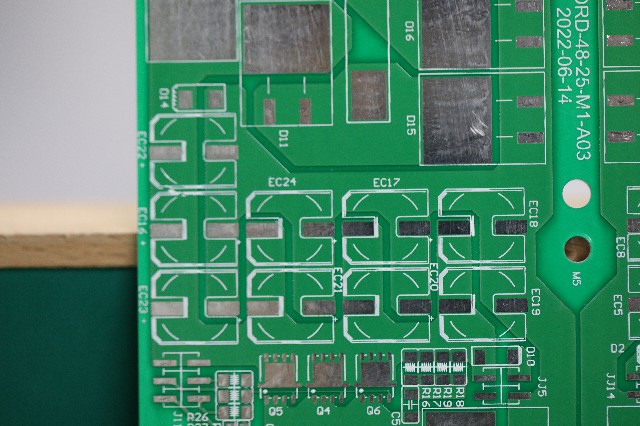

1.多層板在設(shè)計時至少都會有一個地層,一個完整的地平面,但是在頂層和底層由于要擺放元器件,走線,地平面可能會被瓜分得零零碎碎的,有的呈現(xiàn)的是浮銅,有的呈現(xiàn)的是一條長條狀的銅箔。如果長條狀的地平面,端部又沒有過孔回到地層,這種情況在高速電路板上就會等效成一條天線,產(chǎn)生天線效應(yīng),造成嚴(yán)重的EMC問題。所以頂層和底層的地平面在設(shè)計高速PCB需要做合理的處理和優(yōu)化。這些情況如下圖所示。

2.優(yōu)化電源平面,能加寬的平面盡量加寬,有的電源平面雖然看起來很寬了,但是有可能中間打了幾個孔,把大部分的銅箔阻斷了,寬度實際上是變小了,寬度變小的地方阻抗可能就變大,電源紋波可能會增大。加寬電源平面還有一個好處,它和地平面的板級濾波效果會變好。這是從電源完整性方面去優(yōu)化PCB。

3.有些走線需要做好包地,比如時鐘線,這些線要做好包地設(shè)計,如果不包地設(shè)計,與其相鄰的走線就有可能會發(fā)生串?dāng)_現(xiàn)象,如果數(shù)字信號的線,那么就會發(fā)現(xiàn)數(shù)據(jù)通信錯誤的問題。因為高速電路的時鐘信號的上升時間和下降時間很快,與其相鄰的線就會被感應(yīng)出正脈沖或者是負(fù)脈沖,對數(shù)字信號來說,就是1或0,從而導(dǎo)致通信錯誤。

4.有些元器件或者是走線離板邊很近,會有問題。因為離得太近板邊,PCB的制作工藝可能會損壞焊盤或者走線。

5.有些線可以從美觀的角度優(yōu)化一下。

編輯:hfy

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關(guān)推薦

一站式PCBA智造廠家今天為大家講講高速PCB設(shè)計EMI有什么規(guī)則?高速PCB設(shè)計EMI九大關(guān)鍵規(guī)則。隨著電子產(chǎn)品信號上升沿時間的縮短和信號頻率的提高,電磁干擾(EMI)問題越來越受到

![的頭像]() 發(fā)表于

發(fā)表于 12-24 10:08

?127次閱讀

在前面各類設(shè)計的理論講解、設(shè)計實操講解、以及軟件操作的講解的過后,粉絲后臺反饋想結(jié)合前面三種類型進行整體學(xué)習(xí)—模塊設(shè)計,本期推出第一章HDMI模塊的PCB設(shè)計,后續(xù)會繼續(xù)更新各類模塊的PCB設(shè)計教學(xué),以及PCB設(shè)計理論、設(shè)計技巧

![的頭像]() 發(fā)表于

發(fā)表于 10-22 14:16

?662次閱讀

如今,可以認(rèn)為大多數(shù)PCB存在某種類型的信號完整性問題的風(fēng)險,這種問題通常與高速數(shù)字設(shè)計相關(guān)。高速PCB設(shè)計和布局專注于創(chuàng)建不易受信號完整性、電源完整性和EMI/EMC問題影響的電路板

![的頭像]() 發(fā)表于

發(fā)表于 10-18 14:06

?852次閱讀

專業(yè)PCB設(shè)計,高速PCB設(shè)計,PCB設(shè)計外包, PCB Layout,PCB Design,

發(fā)表于 10-13 15:48

電子發(fā)燒友網(wǎng)站提供《PCle Gen 5的高速PCB布局.pdf》資料免費下載

發(fā)表于 09-05 11:04

?3次下載

在PCB設(shè)計中,坐標(biāo)原點是一個非常重要的概念,它決定了PCB布局的起始位置和方向。 一、坐標(biāo)原點的定義 坐標(biāo)原點的概念 在PCB設(shè)計中,坐標(biāo)原點是一

![的頭像]() 發(fā)表于

發(fā)表于 09-02 14:45

?2562次閱讀

一站式PCBA智造廠家今天為大家講講PCB設(shè)計與PCB制板有什么關(guān)系?PCB設(shè)計與PCB制板的關(guān)系。PCB設(shè)計和制板是

![的頭像]() 發(fā)表于

發(fā)表于 08-12 10:04

?552次閱讀

是否滿足ESD或者EMI防護設(shè)計要求,撇開原理圖設(shè)計,PCB設(shè)計一般需要我們從PCB布局和PCB布線兩個方面進行審查,接下來為大家介紹關(guān)于

![的頭像]() 發(fā)表于

發(fā)表于 06-12 09:49

?651次閱讀

的區(qū)別,包括設(shè)計原則、材料選擇、制造工藝和性能特點等方面。 一、設(shè)計原則 1. 信號完整性(Signal Integrity,SI):高速PCB設(shè)計需要關(guān)注信號完整性,以確保信號在傳輸過程中的穩(wěn)定性

![的頭像]() 發(fā)表于

發(fā)表于 06-10 17:34

?1907次閱讀

板)設(shè)計是一個至關(guān)重要的環(huán)節(jié)。一個優(yōu)秀的PCB設(shè)計不僅能夠保證電子產(chǎn)品的穩(wěn)定運行,還能提高產(chǎn)品的外觀和性能。然而,很多設(shè)計師在PCB設(shè)計中會遇到一些常見的問題,這些問題可能會導(dǎo)致設(shè)計延

![的頭像]() 發(fā)表于

發(fā)表于 05-23 09:13

?944次閱讀

建議采用多層PCB設(shè)計,以提供更多的布線層和地層。這有助于降低電阻、電感和噪聲,并提高PCB的抗干擾能力。在儲能系統(tǒng)中,信號的穩(wěn)定傳輸是至關(guān)重要的,因此合理的PCB層次結(jié)構(gòu)設(shè)計非常必要

發(fā)表于 05-14 11:25

?1133次閱讀

cadence原理圖、Allegro PCB設(shè)計。Aundefined

1.根據(jù)客戶要求代畫原理圖和PCB。

2.原理圖和PCB的修改。

3.單板、雙層板、多層板均可。

支持軟件: c

發(fā)表于 05-09 01:38

更好的阻抗控制和電磁兼容性。然而,對于多層PCB設(shè)計來說,過孔是一個不可忽視的關(guān)鍵步驟。過孔的質(zhì)量和設(shè)計的合理性對于PCB的整體性能和可靠性至關(guān)重要。接下來深圳PCBA公司將為大家介紹多層PC

![的頭像]() 發(fā)表于

發(fā)表于 04-15 11:14

?1030次閱讀

PCB設(shè)計的這16個原則你一定要知道

![的頭像]() 發(fā)表于

發(fā)表于 03-12 11:19

?2963次閱讀

設(shè)計PCB的過程中,很多人都會犯一些常見的錯誤,這些錯誤如果不能及時糾正,就會極大地影響產(chǎn)品質(zhì)量。本文將針對 PCB 設(shè)計過程中經(jīng)常會犯的這些錯誤進行分析,希望能夠給大家提供一些有幫助的建議。

![的頭像]() 發(fā)表于

發(fā)表于 02-21 09:32

?600次閱讀

關(guān)于高速PCB設(shè)計的5個修改建議

關(guān)于高速PCB設(shè)計的5個修改建議

評論