經過了這些年的厚積薄發,先進封裝行業已進入最令人興奮的階段。

在摩爾定律放慢的時代,當先進的節點不再能帶來理想的成本效益,并且對新光刻解決方案和7nm以下節點的器件的研發投資大幅增加時,先進封裝代表著增加產品價值的機會(以更低的成本獲得更高的性能)。

在我們看來,先進封裝無論是在擴展路線圖,還是在功能路線圖方面均具有優勢。在摩爾定律放緩的前提下,為了達到更好的集成,先進封裝進入了越來越多的應用領域,當中包括大數據驅動器(如大數據,人工智能,5G,高性能計算(HPC),物聯網(包括工業物聯網),智能汽車,工業4.0和數據中心。

在Yole 看來,支持這些大趨勢所需的電子硬件需要高計算能力,高速,高帶寬,低延遲,低功耗,更多功能,更多內存,系統級集成,各種傳感器,最重要的是低成本。為此這些新趨勢將給各種封裝平臺創造商機,而先進的封裝技術非常適合滿足各種性能要求和復雜的異構集成需求。

Yole指出,先進封裝已成為半導體創新的關鍵,其對于彌合芯片與PCB之間的差距至關重要。他們指出,半導體行業正在開發用于縮放路線圖和功能路線圖的產品。他們表示,即使在7nm工藝以下,只有三個參與者,并且他們的步伐已經放慢,但縮放路線圖也有望繼續(7納米及以下)。其中,使用異構集成并得到先進封裝技術支持的功能路線圖變得更加突出。

實際上,據我們觀察得知,先進的半導體封裝可通過增加功能并保持/提高性能,同時降低成本來增加半導體產品的價值。

Yole表示,當前很多正在開發的高端、低端芯片都在采用各種各樣的多芯片封裝(multi-die packaging :系統級封裝)。在他們看來,這些設計將滿足與異構集成有關的功能性能和更緊迫的生產需求。

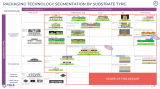

鑒于每個客戶要求的定制程度不斷提高,這給封裝供應商帶來了巨大壓力。為了滿足下一代硬件性能要求,高級封裝必須推動工藝、材料和設備的創新。從他們的介紹我們可以看到,先進的封裝加速了對基板制造、封裝組裝和測試工程中突破性技術的需求。投資于下一代制造工具的開發,例如die到die/die到wafer的混合鍵合,熱壓鍵合(thermo compression bonding :TCB),激光輔助粘合(laser assisted bonding:LAB),面板級工具和基板UV通孔等技術,將有助于推動高級封裝的整體增長。其I / O密度與封裝尺寸的高級封裝技術路線圖如下圖所示。

die到die和die到硅片的混合鍵合(Cu-Cu直接鍵合)是用于2.5D / 3D堆疊和異構集成的關鍵新興技術,它將實現超細間距(小于10um)的互連,消除底部填充、UBM和焊料電鍍,大大降低了外形尺寸(高度)。主要參與者已經在內部開發了該技術(例如,TSMC的SoIC)或通過許可XPERI的DBI混合和DBI超混合鍵合技術(SK Hynix,UMC,Tower Semiconductor等)來實現相關功能。在材料方面,這些參與者希望開發新的介電材料,模塑料,底部填充,焊料互連和TIM,以滿足下一代硬件所要求的嚴格性能和可靠性要求。

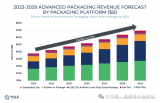

2025年后,先進包裝收入將超過傳統包裝收入

2019年總的IC封裝市場規模約為680億美元。其中先進的包裝(AP)約為290億美元。據Yole預測,這個市場在2019到2025年間將有望以6.6%的CAGR 成長,那就意味著到2025年,先進封裝的市場規模將達到420億美元。與此同時,傳統的封裝市場將以1.9%的CAGR成長。并且整個封裝市場將以4%的復合年增長率(CAGR 2019-2025)增長,并分別達到430億美元和850億美元。

據介紹,如果統計2014年到2025年的復合年增長率,則變為6.1%,為此他們預測,先進封裝市場的收入將增加一倍以上,從2014年的200億美元增加到到2025年的420億美元。這幾乎是傳統封裝市場預期增長的三倍,估計2014-2025年的復合年增長率為2.2%。

由于受到Covid-19的影響,預計2020年AP市場將同比下降6.8%。但是,Yole預計該市場將在2021年反彈,同比增長約14%。隨著大批量產品進一步滲透市場,預計2.5D / 3D TSV IC,ED(in laminate substrate)和扇出市場將分別保持21.3%,18%和16%的年復合增長率。當中表現出色的市場包括移動,網絡和汽車領域的FO;AI / ML,HPC,數據中心,CIS和3D NAND中的3D堆疊;,以及在汽車,移動和基站中使用ED。

按收入細分,移動和消費市場占2019年高級封裝總收入的85%,并將以5.5%的復合年增長率增長,到2025年占AP收入的80%。電信和基礎設施收入是增長最快的細分市場(約為13%)在AP市場中,

在各種先進封裝技術中,倒裝芯片在2019年約占收入的83%。但是,到2025年,其市場份額將降至約77%,而3D堆疊和扇出的份額將從約5%開始增長。到2025年,這一比例將在2019年分別提高到10%和7%。3D堆疊和扇出將繼續以令人印象深刻的CAGR增長,分別是21%和16%,并且它們在各種應用中的采用率將進一步提高。

據Yole預測,3D堆棧市場的增長主要由3D內存(HBM和3D DDR DRAM)、基于2.5D中介層的裸片分區和異構集、3D SoCFoveros、3D NAND和堆疊式CIS所推動。隨著來自不同商業模式的參與者進入市場,扇出封裝市場也有望呈現強勁增長。扇入式WLP主要由移動設備主導,其在2019年至2025年期間的復合年增長率約為3.2%,

分析OSAT財務狀況

查看前25名OSAT的2019年財務狀況,發現前8名與其余參與者之間的差距越來越大。投入大量資金的頂級OSAT與其他產品形成了差距。如果沒有差異化的技術或知識產權用于合并或收購戰略,那么處于尾部的公司將面臨更高的風險。

在2019年,ASE成為絕對領先的OSAT,在完成SPIL收購后以137億美元的收入領先于同行,而在與Amkor和JCET等其他OSAT相比,USI在2019年的收入增長使并沒有受到影響。

據Yole報道,ASE在2019年的資本支出約為18億美元。與JCET($ 503M)和Amkor($ 472)相比,ASE的指出是其三倍以上,由此可見,彌合差距并非易事。從上述數據可以看到,臺積電封裝方面的營收排名第四,收入約為28美元。這主要是因為他們增強了針對HPC和5G部署的CoWoS和InFO-x產品。

隨著日月光以創紀錄的收入和能力上升到新的高度,臺灣公司在2019年繼續以55%的市場份額贏得OSAT市場的份額。OSAT總收入從2018年的279億美元增至2019年的281億美元,其中ASE占OSAT總收入的近50%。而ASE,Amkor和JCET占OSAT總收入的74%。

盡管2019年上半年需求疲軟,但2019年OSAT研發支出從12.9億美元微升至13.1億美元。2019年OSAT的資本支出也保持在2018年水平,約為55億美元。其中前六名的指出都超過 5,000萬美元。由此也可以看到。參與者與其他參與者之間的研發支出存在巨大差距。

ASE是唯一一家在研發方面支出超過5億美元的公司。而其中有10家企業的研發支出少于1000萬美元。Yole認為,要保持競爭優勢,就需要不斷創新技術。從長遠來看,研發投入較小的參與者將無以為繼。他們的選擇有限:要么加大研發投入,要么為收購或者被收購做好準備。

來自不同業務模式的參與者正在進入高級封裝業務

Yole表示,封裝/組裝業務發生了范式轉變,傳統上這是OSAT和IDM的領域。但現在。其他商業模式(晶圓廠,基板/ PCB供應商,EMS / ODM)的參與者正在進入這個市場,蠶食OSAT的份額(圖4)。先進封裝(AP)正在從封裝基板平臺轉移到硅片,這一轉變為臺積電,英特爾和三星等巨頭提供了在AP領域展示實力的機會,成為新AP技術的關鍵創新者。尤其是臺積電,在開發創新的先進封裝平臺(從扇出(InFO)到2.5D Si中介層(CoWoS)到3D SoIC)方面已成為領導者。

根據目前的封裝收入排名,臺積電在OSAT中排名第四。UMC,SMIC,Global Foundries和XMC等其他代工廠也正在投資先進的封裝技術。同時,其他頂級OSAT(例如ASE / SPIL,Amkor和JCET)正在投資各種先進的SiP和扇出技術,以評估它們的競爭并增加其先進封裝的市場份額。

SEMCO,Unimicron,AT&S,Shinko等IC基板和PCB制造商正通過面板級扇出封裝和有機基板中的嵌入式die(和無源芯片)進入高級封裝領域。像Google,Microsoft,Facebook,阿里巴巴等軟件公司正在設計自己的處理器,以控制系統級集成和定制以及供應鏈直至組裝和封裝級。富士康和捷普等EMS廠商正在投資組裝和封裝能力,以將價值鏈上移至更高利潤的業務。

頂尖的OSAT正在投資于IC測試能力以占領測試市場領域。另一方面,諸如KYEC和Sigurd Microelectronics之類的純測試公司正在通過并購或投資于研發為他們的服務產品增加封裝/組裝能力。

責任編輯:tzh

-

芯片

+關注

關注

456文章

50967瀏覽量

424891 -

半導體

+關注

關注

334文章

27527瀏覽量

219950 -

封裝

+關注

關注

127文章

7948瀏覽量

143116

發布評論請先 登錄

相關推薦

什么是先進封裝中的Bumping

先進封裝成為AI時代的核心技術發展與創新

先進封裝技術- 6扇出型晶圓級封裝(FOWLP)

中國半導體產業:面臨關鍵時刻的抉擇

Altair成為三星SAFE EDA合作伙伴

喜訊 | MDD辰達半導體榮獲藍點獎“最具投資價值獎”

半導體先進封裝技術

Yole:先進封裝已成為半導體創新的關鍵

Yole:先進封裝已成為半導體創新的關鍵

評論