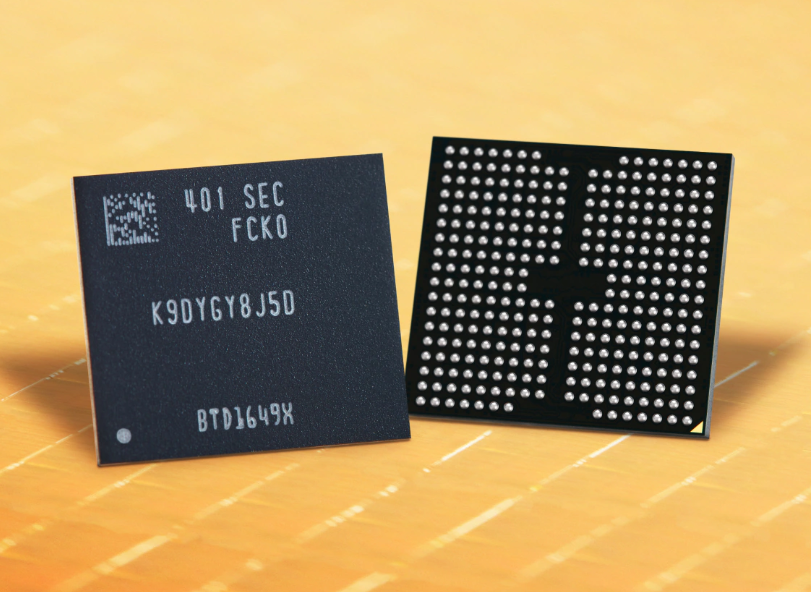

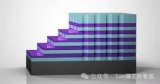

依托于先進(jìn)工藝的 3D NAND,氧化層越來越薄,面臨可靠性和穩(wěn)定性的難題,未來的 3D NAND 將如何發(fā)展?如何正確判斷一款 3D NAND 的總體效率?

在 2020 年的閃存峰會上,TechInsights 高級技術(shù)研究員 Joengdong Choe 發(fā)表了相關(guān)演講,詳細(xì)介紹了 3D NAND 和其他新興存儲器的未來。TechInsights 是一家對包括閃存在內(nèi)的半導(dǎo)體產(chǎn)品分析公司。

3D NAND 路線圖:三星最早入局,長江存儲跨級追趕

Choe 介紹了 2014-2023 年的世界領(lǐng)先存儲公司的閃存路線圖,包括三星、鎧俠(原東芝存儲)、英特爾、美光、SK 海力士和長江存儲等公司的 3D NAND 技術(shù)發(fā)展路線。

Choe 給出的路線圖顯示,三星電子最早在 3D NAND 開拓疆土,2013 年 8 月初就宣布量產(chǎn)世界首款 3D NAND,并于 2015 年推出 32 層的 3D NAND,需要注意的是,三星將該技術(shù)稱之為 V-NAND 而不是 3D NAND。

之后,三星陸續(xù)推出 48 層、64 層、92 層的 V-NAND,今年又推出了 128 層的產(chǎn)品。

SK 海力士稍晚于三星,于 2014 年推出 3D NAND 產(chǎn)品,并在 2015 年推出了 36 層的 3D NAND,后續(xù)按照 48 層、72 層 / 76 層、96 層的順序發(fā)展,同樣在今年推出 128 層的 3D NAND 閃存。

美光和英特爾這一領(lǐng)域是合作的關(guān)系,兩者在 2006 年合資成立了 Intel-Micron Flash Technologies(IMFT)公司,并聯(lián)合開發(fā) NAND Flash 和 3D Xpoint。不過,兩者在合作十多年之后漸行漸遠(yuǎn),IMFT 于 2019 年 1 月 15 日被美光以 15 億美元收購,之后英特爾也建立起了自己的 NAND Flash 和 3D Xpoint 存儲器研發(fā)團(tuán)隊。

另外,在路線圖中,長江存儲于 2018 年末推出了 32 層的 3D NAND,2020 年推出了 64 層的 3D NAND。

從路線圖中可以發(fā)現(xiàn),從 90 多層跨越到 100 多層時,時間周期會更長。

相較于其他公司,國內(nèi)公司 3D NAND 起步較晚,直到 2017 年底,才有長江存儲推出國產(chǎn)首個真正意義上的 32 層 3D NAND 閃存。不過長江存儲發(fā)展速度較快,基于自己的 Xtacking 架構(gòu)直接從 64 層跨越到 128 層,今年 4 月宣布推出 128 層堆棧的 3D NAND 閃存,從閃存層數(shù)上看,已經(jīng)進(jìn)入第一梯隊。

近期,長江存儲 CEO 楊士寧也在 2020 北京微電子國際研討會暨 IC World 學(xué)術(shù)會議上公開表示,長江存儲用 3 年的時間走過國際廠商 6 年的路,目前的技術(shù)處于全球一流水準(zhǔn),下一步是解決產(chǎn)能的問題。

值得一提的是,在中國閃存市場日前公布的 Q3 季度全球閃存最新報告中,三星、鎧俠、西部數(shù)據(jù)、SK 海力士、美光、英特爾六大閃存原廠占據(jù)了全球 98.4% 的市場份額,在剩下的 1.6% 的市場中,長江存儲 Q3 季度的收入預(yù)計超過 1%,位列全球第七。

層數(shù)并未唯一的判斷標(biāo)準(zhǔn)

盡管在各大廠商的閃存技術(shù)比拼中,閃存層數(shù)的數(shù)量是最直接的評判標(biāo)準(zhǔn)之一。

不過,Choe 指出,大眾傾向于將注意力集中在閃存層數(shù)上可能是一種誤導(dǎo),因為字線(帶有存儲單元的活動層)的實際數(shù)量會有很大的不同,例如可以將其他層作為偽字線,以幫助緩解由較高層數(shù)引起的問題。

Choe 表示,判斷 3D NAND 工作效率的一種標(biāo)準(zhǔn)是用分層字線的總數(shù)除以總層數(shù),依據(jù)這一標(biāo)準(zhǔn),三星的擁有最優(yōu)秀的設(shè)計,不過三星也沒有使用多個層或堆棧,不像其他廠商當(dāng)前的閃存那樣使用 “串堆棧”。

一種提高 3D NAND 總體效率的方法是將 CMOS 或控制電路(通常稱為旁路電路)放置在閃存層下面。這一方法有許多名稱,例如 CuA(CMOS-under-Array)、PUC (Periphery-Under-Cell), 或者 COP (Cell-On-Periphery)。

長江存儲的設(shè)計有些特別,因為它有一些電路在閃存的頂部,而 CMOS 在連接到閃存之前,是在更大的工藝節(jié)點中制造的。Choe 認(rèn)為這種技術(shù)有潛力,但目前存在產(chǎn)量問題。

另外,各個公司使用工藝也不盡相同,比較典型的就是電荷擷取閃存技術(shù)(Charge trap flash,簡稱 CTF)和傳統(tǒng)浮柵存儲器技術(shù)(Floating gate,簡稱 FG)。

CTF 使用氮化硅來存儲電子,而不是傳統(tǒng) FG 中典型的摻雜多晶硅。具體而言,F(xiàn)G 將電子存儲在柵極中,瑕疵會導(dǎo)致柵極和溝道之間形成短路,消耗柵極中的電荷,即每寫入一次數(shù)據(jù),柵極電荷就會被消耗一次,當(dāng)柵極電荷被消耗完時,該閃存就無法再存儲數(shù)據(jù)。而 CTF 的電荷是存儲在絕緣層之上,絕緣體環(huán)繞溝道,控制柵極環(huán)繞絕緣體層,理論而言寫入數(shù)據(jù)時,電荷未被消耗,可靠性更強(qiáng)。

Choe 指出在當(dāng)前的存儲芯片公司中,英特爾和美光一直使用的是傳統(tǒng)的浮柵級技術(shù),而其他制造商則依靠電荷擷取閃存設(shè)計。美光直到最近發(fā)布 176 層才更換新的技術(shù),英特爾的 QLC 在使用浮柵技術(shù)的情況下,可以保持更好的磨損性能,但這也會影響其閃存的耐用性、可靠性、可擴(kuò)展性以及其他性能優(yōu)勢。

下一個十年將指向 500 層

Choe 在演講中提到,鎧俠未來將用到的分離柵結(jié)構(gòu)或分離單元結(jié)構(gòu)技術(shù)也很有趣,它可以使存儲器的密度直接增加一倍,并且由于分離單元結(jié)構(gòu)的半圓形形狀而擁有特別堅固的浮柵結(jié)構(gòu),具有更強(qiáng)的耐用性。

Choe 預(yù)計,隨著平臺或堆棧數(shù)量的增加(目前最多為兩個),閃存層數(shù)將繼續(xù)增加,每個閃存芯片的存儲量也會相應(yīng)增加。Choe 認(rèn)為,這與其他技術(shù),例如,硅通孔(TSV),疊層封裝(PoP / PoPoP)以及向 5LC / PLC 的遷移一樣,都在下一個十年指向 500 層以上和 3 TB 裸片。

另外,Choe 詳細(xì)說明了閃存的成本是按照每 GB 多少美分來計算的,這意味著未來 3D 閃存的架構(gòu)將越來越便宜,不過 2D 閃存的價格依然昂貴,甚至比 3D 閃存貴很多倍。

談到尖端閃存技術(shù)的推進(jìn),Choe 認(rèn)為尖端閃存總是首先進(jìn)入移動和嵌入式產(chǎn)品,例如 5G 手機(jī)是當(dāng)下的主要驅(qū)動力。他還指出,2D 平面閃存仍然有一些應(yīng)用市場,通常將其視為低延遲 SLC 用作 3D XPiont 的存儲類內(nèi)存(SCM)的替代品,如 Optane 或美光最近發(fā)布的 X100,盡管 X100 在消費市場并不常見。

目前,100 層以上的 3D 閃存產(chǎn)品,目前已經(jīng)發(fā)布了 SK 海力士 128L Gold P31 和三星 128L 980 PRO,美光最近也基于 176L flash 發(fā)布了 Phison E18 的硬盤原型。另外,西部數(shù)據(jù)和鎧俠的 BiCS5 和英特爾的 144 層產(chǎn)品將在明年發(fā)布。

更好的控制器需要更高密度的閃存,未來幾年閃存將向更快和更大容量的方向發(fā)展。

責(zé)任編輯:PSY

-

閃存

+關(guān)注

關(guān)注

16文章

1789瀏覽量

114944 -

NAND

+關(guān)注

關(guān)注

16文章

1682瀏覽量

136177 -

3D

+關(guān)注

關(guān)注

9文章

2882瀏覽量

107579

發(fā)布評論請先 登錄

相關(guān)推薦

預(yù)期提前,鎧俠再次加速,3D NAND準(zhǔn)備沖擊1000層

3D NAND的發(fā)展方向是500到1000層

【半導(dǎo)體存儲】關(guān)于NAND Flash的一些小知識

3D打印技術(shù)應(yīng)用的未來

安寶特產(chǎn)品 安寶特3D Analyzer:智能的3D CAD高級分析工具

裸眼3D筆記本電腦——先進(jìn)的光場裸眼3D技術(shù)

中興通訊與中國移動發(fā)布全球首創(chuàng)AI裸眼3D新品,引領(lǐng)3D科技新浪潮

3D NAND閃存來到290層,400層+不遠(yuǎn)了

裸眼3D頻頻“出圈” 電信積極布局并發(fā)力裸眼3D領(lǐng)域

3D HMI應(yīng)用場景和發(fā)展趨勢

三星將推出GDDR7產(chǎn)品及280層堆疊的3D QLC NAND技術(shù)

未來的3D NAND將如何發(fā)展?如何正確判斷一款3D NAND的總體效率?

未來的3D NAND將如何發(fā)展?如何正確判斷一款3D NAND的總體效率?

評論