基于FPGA的音樂蜂鳴器設計

設計背景

蜂鳴器是一種一體化結構的電子訊響器,采用直流電壓供電,廣泛應用于計算機、打印機、復印機、報警器、電子玩具、汽車電子設備、電話機、定時器等電子產品中作發聲器件。在一般設計中,可利用蜂鳴器檢測有些按鍵是否按下,或者有些功能是否正常等,當然如果足夠浪漫,也可以讓蜂鳴器演奏音樂。

設計原理

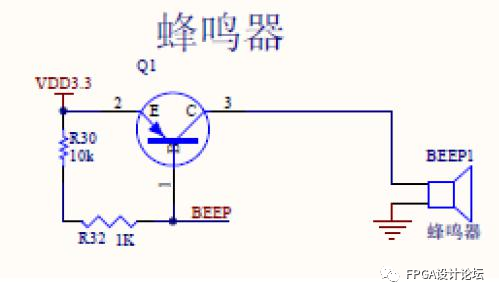

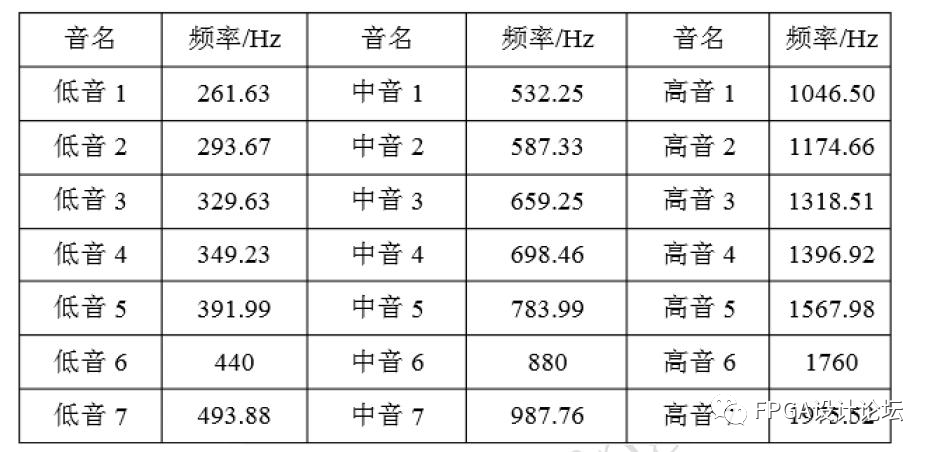

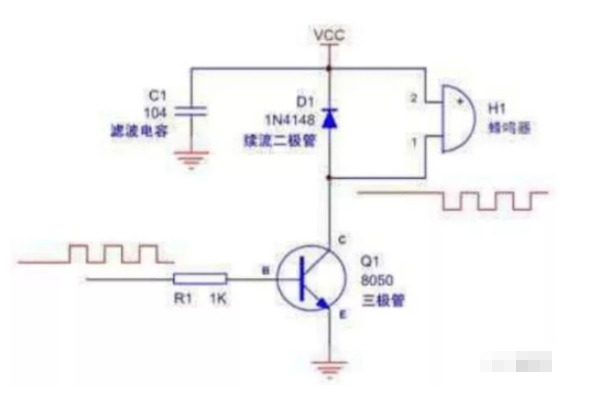

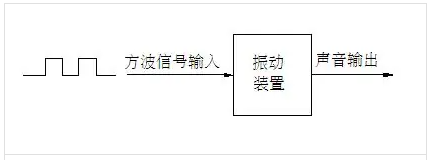

本設計使用的是無源蜂鳴器,也可稱為聲響器,原理電路圖如下所示。它沒有內部驅動電路,無源蜂鳴器工作的理想信號為方波,如果給直流,蜂鳴器是不響應的,因為磁路恒定,鉬片不能震動發音。根據電路圖可知,由于 FPGA 的驅動能力不夠,這里增加了一個三極管來驅動這個無源蜂鳴器。在驅動時,只需要向蜂鳴器發送一定頻率的方波,就可以使蜂鳴器發聲。那么應該發送怎樣的頻率呢?具體則可參考下表(音節頻率表)

樂曲能連續演奏所需要的兩個基本數據是:組成樂曲的每個音符的頻率值(音調)和每個音符持續的時間(音長)。因此只要控制 FPGA輸出到蜂鳴器的激勵信號頻率的高低和持續時間,就可以使蜂鳴器發出連續的樂曲聲。在本設計中,由于至芯開發板的晶振為 50MHz,所以我們需要一個一個分頻模塊(PLL)產生一個較低的基準頻率(1MHz)。還需要一個空間儲存樂譜,由于樂譜是固定的不需要更改,所以我們選擇 ROMIP 核進行存儲。基準頻率 1MHz 可分頻得到所有不同頻率的信號。最大的分頻比為1_000_000/262/2。既然是音樂,那么就需要節拍,一般采用 4 拍,即音長為 0.25s,所以還需設計一個模塊,控制每 0.25s,ROM 地址加 1,。如果需要發送一個低音 1 并維持 1 秒,則只需要在 ROM 的連續四個地址中寫入低音 1 的對應信息即可。在設計中為了方便在 ROM 中儲存數據,這里數據格式為 8’hAB,其中 A 暫時為三個值 1、2、4,分別表示低音、中音、高音。B 暫時為七個值 1、2、3、4、5、6、7。比如要產生一個低音 1,只需在 ROM中存儲 8’h11,如要產生一個高音 7,只需在 ROM中存儲 8’h47,以此類推即可。這時,就需要一個解碼模塊,將 ROM 中的數據還原成音樂發生器所需要的數據。

設計架構圖

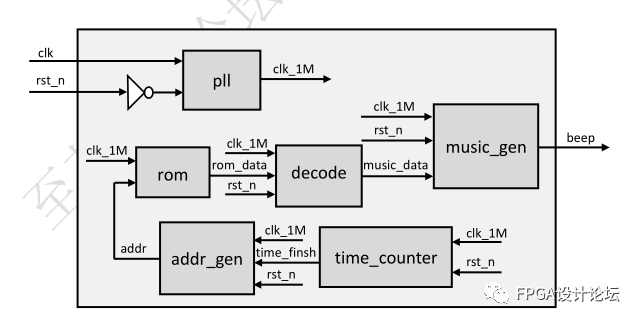

根據上述的分析,得到如下的架構圖

本設計包括 6 個模塊,PLL 模塊把 50MHz 的時鐘信號降到 1MHz,rom 模塊存儲音樂數據,time_counter 是一個計數模塊,產生節拍,每到 0.25s,輸出的 time_finsh 變為一個周期的高電平。并發送給addr_gen 模塊,產生 addr,讓 rom 輸出下一個地址的數據。rom 輸出的數據 rom_data 輸入到 decode 解碼模塊,將解碼后的數據music_data 輸入到 music_gen 模塊,通過計數器,如果計數器小于music_data 的值,則 beep 保持不變,否則,beep 取反,并且計數器

清 1,從而產生特定的方波頻率。

設計代碼

time_counter 模塊代碼如下:

addr_gen 模塊代碼如下:

decode 解碼模塊代碼如下:

music_gen 模塊代碼如下:

beep 頂層模塊代碼如下:

仿真圖

仿真結果如下:

由仿真圖可知:當 rom 輸出 rom_data 為 8’h16 時,代表輸出低音6,解碼后結果 music_data 為 1136,輸出的 beep 頻率為 440Hz,與實際低音 6 的音節頻率表的值一致;當 rom 輸出 rom_data 為 8’h22時,代表輸出中音 2,解碼后結果 music_data 為 851,輸出的 beep頻率為 563Hz,與實際中音 2 的音節頻率表的值相差 24Hz,存在一定的誤差,但是不影響樂曲的播放。如果想提高 beep 頻率的精度,減小誤差,則可以將 1MHz 的基準頻率提高。

責任編輯:lq

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604322 -

ROM

+關注

關注

4文章

575瀏覽量

85835 -

蜂鳴器

+關注

關注

12文章

892瀏覽量

46003

原文標題:FPGA入門課程 音樂蜂鳴器設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

蜂鳴器電壓范圍怎么判斷

測量蜂鳴器電壓的工具和方法

蜂鳴器需要串聯多大的電阻

蜂鳴器電路電阻的作用是什么

multisim中蜂鳴器怎么連接

buzzer蜂鳴器在Multisim的使用

蜂鳴器的功能和作用有哪些

如何讓蜂鳴器發出不同頻率的聲音

有源蜂鳴器與無源蜂鳴器的發聲原理是什么

無源蜂鳴器和有源蜂鳴器的對比分析

無源蜂鳴器和有源蜂鳴器的聲音區別

無源蜂鳴器怎么才會響 蜂鳴器驅動電路原理圖

請問用蜂鳴器播放音樂的時候如何同時播放兩段音樂?

蜂鳴器的發聲原理 蜂鳴器電路圖分享

基于FPGA的音樂蜂鳴器設計

基于FPGA的音樂蜂鳴器設計

評論