重點

●用于GF 12LP+解決方案的DesignWare IP核產品組合包括USB4、PCIe 5.0、Die-to-Die HBI以及112G USR/XSR、112G Ethernet、DDR5、LPDDR5、MIPI、OTP NVM等

●新思科技與GF的長期合作,成功實現了DesignWare IP核從180nm到12nm的開發,并可應用于廣泛領域

新思科技(Synopsys)近日宣布與GLOBALFOUNDRIES(GF)開展合作,開發用于GF 12LP+ FinFET解決方案的廣泛DesignWare IP核產品組合,該IP核產品組合包括USB4/3.2/DPTX/3.0/2.0、PCIe 5.0/4.0/2.1、Die-to-Die HBI、112G USR/XSR、112G Ethernet、DDR5/4、LPDDR5/4/4X、MIPI M-PHY以及模擬到數字轉換器和一次性可編程(OTP)非易失性存儲器(NVM)IP核。經優化的DesignWare IP核可滿足GF 12LP+解決方案中云計算和AI芯片對高帶寬內存吞吐量和高性能連接的需求。此次合作是兩家公司長期成功合作中的又一重要里程碑。

作為GF最先進的FinFET解決方案,12LP+以GF成熟的14nm/12LP平臺為基礎。該平臺現已成功出貨超過一百萬片晶圓。相較于12LP,12LP+的性能得到了提升:SoC水平邏輯性能提高了20%并且邏輯晶片尺寸方面改進了10%。

“我們的12LP+解決方案經專門設計,集性能、功率和面積的出色表現于一體,可滿足高性能計算、云計算和邊緣AI加速器、存儲的特定需求。通過與領先的IP核提供商新思科技合作,共同開發可用于GF12LP +解決方案的一系列高質量DesignWare IP核,為我們的共同客戶提供更大的差異化優勢和更高的價值,同時在最大程度上降低他們的開發成本并加快產品上市時間。借助Die-to-Die IP核,我們可以為那些轉向小芯片架構并尋求更低產品成本和更高配置靈活性的客戶提供支持。”

——Mark Ireland

生態系統和設計解決方案副總裁 GF

“作為值得信賴的IP核提供商,新思科技將繼續加強與GF這樣的重要晶片代工廠合作,以提供融合最新工藝技術的高品質DesignWare IP核,讓開發者可以獲益于性能、功率和尺寸方面的改進。數十年來,我們與GF開展長期合作,為開發者提供了包括12LP+解決方案在內的基于GF技術的業內最廣泛IP核組合,協助其集成包括快速增長的高性能計算、云計算和邊緣AI加速器以及存儲等應用市場所需的最新一代IP核。”

——John Koeter

責任編輯:xj

原文標題:用于GF 12LP+解決方案的DesignWare IP核產品組合來啦!

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

IP核

+關注

關注

4文章

329瀏覽量

49536 -

GF

+關注

關注

0文章

19瀏覽量

28742 -

DesignWare

+關注

關注

0文章

10瀏覽量

10300

原文標題:用于GF 12LP+解決方案的DesignWare IP核產品組合來啦!

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

康普推出全新RUCKUS Pro AV產品組合

高通推出面向AI時代的全新工業物聯網產品組合

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

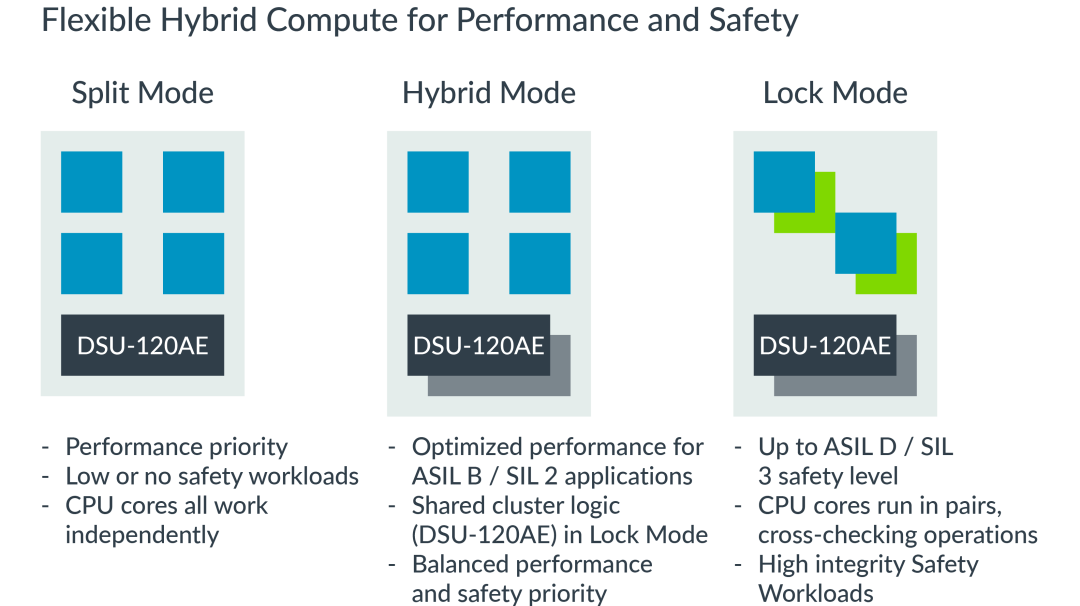

采用Arm AE IP產品組合實現SDV功能安全

英飛凌宣布擴展其藍牙產品組合

Cadence 擴充系統 IP 產品組合,推出 NoC 以優化電子系統連接性

Microchip擴大旗下藍牙低功耗產品組合 幫助客戶快速啟動產品開發

新思科技與臺積公司深度合作,推動芯片設計創新

關于FPGA IP核

新思科技收購Intrinsic ID,持續拓展全球領先的半導體IP產品組合

新思科技收購Intrinsic ID,強化半導體IP產品組合

恩智浦推出全新面向工業與物聯網應用的MCX微控制器產品組合

新思科技將開發廣泛DesignWare IP核產品組合

新思科技將開發廣泛DesignWare IP核產品組合

評論