新的模數轉換器(ADC)技術使首次實現單芯片100 Gbps相干接收器的設計成為可能。它使用65 nm CMOS技術,可以滿足長距離光學系統的性能和功率要求。它為短途和更高速率的應用提供了未來,并提供了設計僅能解決部分問題的合適ADC的能力。

一個100Gbps相干接收器需要四個56GSa / s模數轉換器(ADC)和一個僅耗散數十瓦功率的tera-OPS DSP。本文討論了推動單芯片CMOS解決方案的力量。本文還介紹了富士通超快CMOS ADC,它為使用相干接收器的100Gbps以太網和OTU-4傳輸系統提供了使能技術。

為了提供長距離的100 Gbps光傳輸網絡,以提供最大的覆蓋范圍和對非理想光纖的免疫力,業界已將雙極化,正交,相移鍵控(DP-QPSK)作為一種調制方法。這意味著需要一個相干的接收器。該決定所帶來的最大實施挑戰是對低功耗,超高速ADC的需求。他們的技術要求定義了這種接收器的實現方式。

沒有合適的ADC,尤其是沒有足夠低功耗的ADC,就不可能生產出對商用光網絡有用的100 Gbps相干接收器(與僅適用于實驗室演示的原型系統相反)。而且,將來,對于高速短途鏈路,將需要此類ADC,在低功耗和低成本中,由于短途鏈路比遠程鏈路多得多,因此低功耗和成本變得更加重要。

這些ADC需要至少56 Gbps的采樣率和6位或更高的分辨率。每個功率消耗必須不超過幾瓦,以適應系統施加的功率限制。直到最近,人們仍認為需要諸如非常先進的SiGe或超小型幾何CMOS(40 nm或更小)之類的技術來滿足這些要求,并且對于高達15 GHz或更高的輸入信號仍具有足夠的動態范圍。根據ADC設計的歷史性進展推斷,到2008年底,合適的ADC將在2013年前面世。

朝著單芯片CMOS ADC DSP的驅動

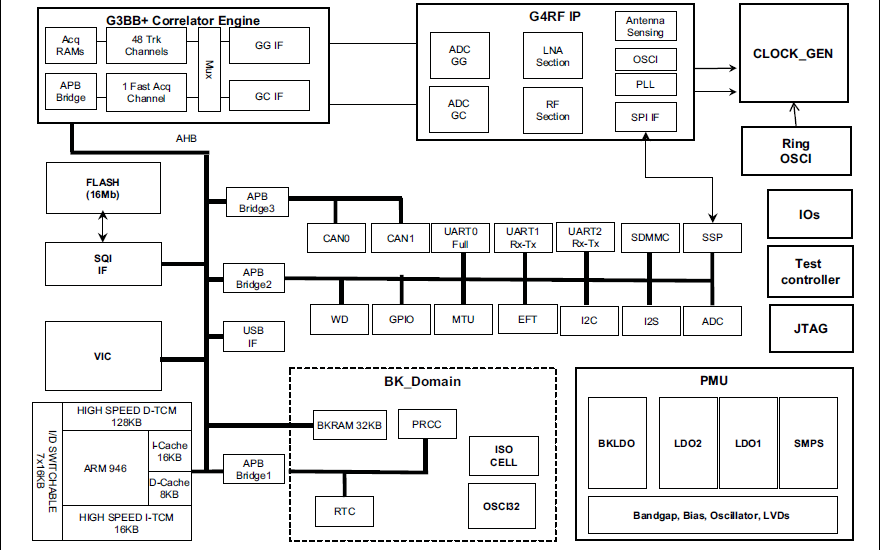

一個DP-QPSK相干接收機需要四個ADC通道(圖1),因為存在兩個光偏振。每個通道需要兩個ADC來數字化I / Q信號。為了達到100Gbps的凈線路速率,波特率至少應為28Gbaud / s,以允許開銷,這需要56GSa / s ADC。系統SNR要求意味著通常需要6位分辨率或更高分辨率,以留出一定的余量以增加噪聲和失真。因此,對于四個ADC,DSP的輸出數據速率為1.3Tb / s –或如果使用8位分辨率以允許ADC后有更多裕量和/或數字AGC,則為1.8Tb / s。

如果ADC未與DSP集成在一起,則必須在芯片之間傳輸大量數據,這不僅難以實現(大量通道和高數據速率),而且會消耗大量功率用于序列化,反序列化和傳輸。即使對于11Gbps通道(ADC發送+ DSP接收)使用100mW / ch的樂觀數字,這也意味著每個ADC僅需要3-4W即可傳輸數據。對于原型或演示者,這是可接受的,但對于生產解決方案,這是不可接受的。

編輯:hfy

-

CMOS

+關注

關注

58文章

5724瀏覽量

235685 -

接收器

+關注

關注

14文章

2473瀏覽量

71988 -

模數轉換器

+關注

關注

26文章

3208瀏覽量

126877 -

光傳輸

+關注

關注

3文章

91瀏覽量

23880

發布評論請先 登錄

相關推薦

MACOM 100 Gbps 光互連的解決方案

MICRF002是單芯片ASK / OOK(ON-OFF鍵控)RF接收器IC

AG7220代理|AG7220設計方案|AG7220方案應用|HDMI2.0RE驅動方案

IT66021FN是單端口HDMI接收器,

Broadcom推出GPS接收器

ADI推出單芯片寬帶IF接收器子系統AD6676,可減少接收器設計的復雜性

STA8089FG單芯片獨立定位接收器芯片的數據手冊免費下載

STA8090FG單芯片獨立定位接收器IC的數據手冊免費下載

單芯片100 Gbps相干接收器的設計方案

單芯片100 Gbps相干接收器的設計方案

評論