本應用筆記的目的是讓讀者了解PIC32MZ器件系列中的 1 級(L1)CPU 緩存實現(xiàn),讓讀者了解緩存系統(tǒng)中可能發(fā)生的危險,并描述解決這些問題的方法。對于高級用戶,還討論了 microAptiv? 內核中管理緩存以獲得最佳性能的特殊指令。

本文檔不打算全面討論緩存體系結構或實現(xiàn),也不涉及緩存管理的每個細節(jié)。從未使用過具有 L1 緩存的嵌入式控制器的開發(fā)人員,或希望了解 PIC32MZ 器件中 L1 緩存實現(xiàn)的開發(fā)人員,應閱讀本文檔。

CPU 緩存是一個單獨的內存塊,用于補償主內存的訪問時間。被描述為一級緩存的緩存使用與 CPU 一樣快的內存,因此只要 CPU 正在訪問緩存,它就永遠不必等待指令或數據。2 級和 3 級高速緩存與 1 級高速緩存結合使用,其內存訪問時間大于 CPU,但小于主內存。

該PIC32MZ器件系列僅采用1級高速緩存。L1緩存分為兩部分,指令緩存和數據緩存。CPU 可以直接訪問內存或通過緩存訪問內存。高速緩存的使用對于實現(xiàn)PIC32MZ器件系列的最大性能至關重要。與通過系統(tǒng)總線進行訪問時的多個時鐘周期相比,對高速緩存的內存訪問發(fā)生在單個時鐘周期內。

PIC32MZ 架構

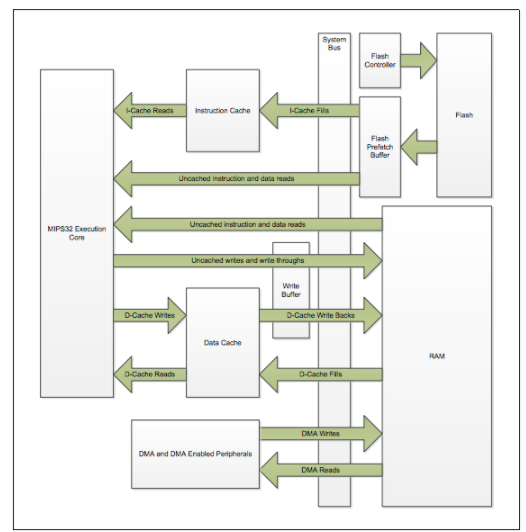

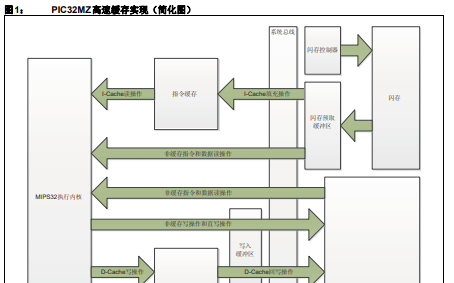

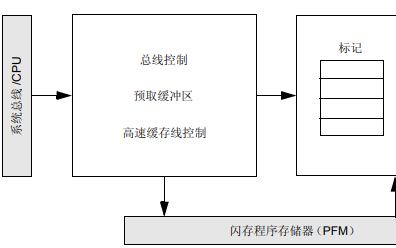

以下部分介紹了PIC32MZ架構的 L1 緩存和其他兩個部分,它們對其操作和配置至關重要。

閃存預取模塊

Flash Prefetch 模塊用于隱藏 Flash 等待狀態(tài)。它通過使用 128 位數據路徑(是 32 位 CPU 總線寬度的四倍)獲取程序閃存來實現(xiàn)。它是預測性的,假設下一個需要的數據是下一行地址。只要代碼不分支,下一條指令總是可用的。加載新行時,分支會導致停頓。該模塊中的寄存器確定閃存等待狀態(tài)以及預取是應用于指令訪問、數據訪問、兩者還是兩者都不進行。

內存映射單元

在所有 PIC32 架構中,CPU 對存儲器和外設的訪問都是通過虛擬地址空間完成的。虛擬地址空間分為五個段,分別命名為 KSEG0 到 KSEG3 和 KUSEG。物理到虛擬 KSEG0 到 KSEG1 地址的映射是固定的,所有內部存儲器都存在于 KSEG0 和 KSEG1 段中。KSEG1 從不緩存,而 KSEG0 是可緩存的段。

PIC32MZ 架構引入了基于轉換后備緩沖器(TLB)的存儲器映射單元(MMU)。TLB 可以配置為對 KUSEG、KSEG2 和 KSEG3 執(zhí)行虛擬內存到物理內存的轉換。這些段的可緩存性屬性是在使用 CPU 協(xié)處理器 0 (CP0) EntryLo0 和 EntryLo1 寄存器配置 TLB 時定義的。

L1 指令和數據緩存

如圖 1 所示,CPU 可以直接訪問系統(tǒng) RAM,也可以通過緩存訪問。同樣,對 Flash 的訪問可以直接發(fā)生,也可以通過緩存發(fā)生。DMA 訪問總是直接通過 RAM 進行。除了 CPU 和緩存之間的訪問之外,所有訪問都涉及系統(tǒng)總線。

在復位時,代碼執(zhí)行從 KSEG1 使用非緩存訪問發(fā)生。這是必要的,因為緩存在被啟動代碼初始化之前無法使用。一旦緩存被初始化,代碼執(zhí)行就可以從 KSEG0 開始,它利用緩存來獲得最佳性能。

當 CPU 使用緩存進行訪問時,系統(tǒng)將檢查所需的數據是否已存在于緩存中。如果數據存在于緩存中,則不執(zhí)行任何操作。這稱為緩存命中。如果沒有,硬件會使用內存內容填充指令或數據緩存。這稱為緩存未命中。緩存未命中會導致性能損失,而緩存命中則不會。

緩存的大小是閃存或 RAM 大小的一小部分。它可以在初始化時以多種方式進行配置以優(yōu)化性能。MPLAB 開發(fā)工具將 PIC32MZ 緩存配置為“四路關聯(lián)”,因為這將是大多數應用的最佳配置。四路關聯(lián)配置將緩存分為四個相等的部分,稱為路。其中每一個都分布在整個內存地址范圍內。每個緩存路被分成緩存線,這些緩存線代表可以在緩存和閃存或 RAM 之間傳輸的最小數據量。每行數據都包含將其與物理內存相關聯(lián)并跟蹤其狀態(tài)的標簽。因此,每個內存位置都可以在四個高速緩存路之一的高速緩存行中表示。

PIC32MZ 緩存實現(xiàn)

編輯:hfy

-

存儲器

+關注

關注

38文章

7514瀏覽量

164004 -

cpu

+關注

關注

68文章

10880瀏覽量

212212 -

PIC32MZ

+關注

關注

2文章

14瀏覽量

4290

發(fā)布評論請先 登錄

相關推薦

PIC32MZ中斷代碼錯誤怎么回事

Microchip 32位PIC32MZ EF單片機系列喜添新成員 部分器件可支持擴展級溫度范圍

Microchip 32位PIC32MZ EF單片機系列喜添新成員, 部分器件可支持擴展級溫度范圍

PIC32MZ EF系列處理器主要特性及開發(fā)板框圖

PIC32MZ嵌入連接MCU主要特性和框圖分析

PIC32MZ器件系列中使用L1CPU高速緩存實現(xiàn)的風險和解決方法

PIC32 FRM帶L1CPU高速緩存的器件上的預取模塊特性和操作中文概述

使用PIC32MZ設計的20msps示波器資料說明

使用MPLAB Harmony v3基于PIC32MZ MCU在運行時使用高速緩存維護操作處理高速緩存一致性問題

如何使用PIC32MX/PIC32MZ/PIC32MM器件上的DMA CRC生成器

PIC32MZ器件系列中的 1 級(L1)CPU 緩存實現(xiàn)

PIC32MZ器件系列中的 1 級(L1)CPU 緩存實現(xiàn)

評論