1 引 言

在當今普遍使用的手持式移動設備中,如何降低嵌入式系統的功耗、延長電池使用的時間等問題一直是困擾開發人員的一個難題。大量的功耗不僅導致移動設備的待機時間縮短,還會導致芯片熱量增加,降低可靠性,而且也會增加散熱系統的成本。待機時間問題雖然可以通過提高電池容量解決,但實際情況是嵌入式系統的功耗增長超過電池技術的發展,因此單純依靠電池技術的發展是不可能在短期內解決現在正遇到的功耗問題。

CMOS邏輯電路被認為是現今最通用的大規模集成電路技術,因為CMOS可以高度集成,并具有低功耗、輸入電流小等特性,而且從理論上,理想的CMOS電路的靜態功耗可以認為是零,是一種“理想”的邏輯器件。但實際的CMOS器件依然需要消耗功率,而且頻率越高,消耗的動態功耗越高。雖然芯片的封裝、使用散熱片和風扇能夠散掉芯片和系統所產生的熱量,然而隨著芯片和系統尺寸持續地增加,要提供充分的散熱就必須付出更多的代價,而且系統的尺寸也會增加,散熱系統的機械部分也會降低系統的可靠性。

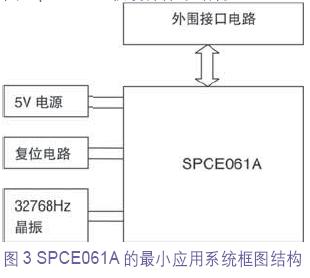

嵌入式系統由硬件和軟件共同組成,因此降低嵌入式系統功耗的方法也有硬件方法和軟件方法。本文以移植到凌陽16位處理器μ′nSPTM上的嵌入式實時操作系統μCOS-Ⅱ為例,使用凌陽公司提供的SPCE061A開發板,討論如何利用μCOS-Ⅱ給出的內核擴展接口,實現一個低功耗的嵌入式系統。

2 嵌入式系統的功耗

嵌入式系統的平均功耗和電池容量共同決定待機時間,平均功耗越小、電池容量越大則待機時間越長。而嵌入式系統的功耗可以分為靜態功耗和動態功耗,靜態功耗是由CMOS電路的漏電流形成,現在的技術已經使漏電流減少到盡可能小,因此靜態功耗一般占總功耗的比例很小;動態功耗是由CMOS電路的分布電容充放電形成,該功耗占總功耗的比例很大,因此也是主要的研究對象。動態功耗的大小可由式PD=CL×VDD2×f表示,CL是CMOS電路的分布電容,與芯片尺寸和工藝有關;VDD是電源電壓;f是系統的工作頻率,降低工作頻率有助于降低系統功耗,但會使系統工作速度下降。

由上述分析可知,降低嵌入式系統的功耗主要有兩種途徑。第一種是動態頻率調節(DFS),它可以改變不同電壓域上的時鐘頻率。雖然這種方法可以消除空閑等待的時間,但是卻不能減少能量的消耗。比如將一個任務以通常情況的一半頻率來運行,意味著完成這個任務要通常的兩倍時間。DFS有用的地方在于,它可以降低峰值功耗。第二種方式是動態地電壓和頻率調節(DVFS)。DVFS是建立在DFS基礎之上的,它既要降低頻率,又要降低電壓。由于電壓對動態功耗二次方的關系,DVFS確實能將能量的消耗節省下來。為此ARM公司的Faisal M.Goriawalla先生提出IEM(智能能量管理)方案,該方案采用步進策略、前瞻策略或平均數策略等算法調節系統的頻率和電壓,對于最終產品來說,則可以節省15%~20%的能量消耗(來源于ARM公司OEM合作伙伴的數據)。

3 實時操作系統μCOS-Ⅱ和凌陽處理器μ′nSPTM簡介

μCOS-Ⅱ是一個簡單、高效的嵌入式實時操作系統內核,具有可搶占的實時多任務調度系統功能。μCOS-Ⅱ提供很多系統服務,例如郵箱、消息隊列、信號量、塊大小固定的內存的申請與釋放、時間相關函數等。μCOS-Ⅱ2.5版本支持64個任務,每個任務一個特定的優先級。優先級越高,數字越小。系統占用了8個任務,保留優先級為0,1,2,3,OS LOWEST_PRIO-3,OS_LOWEST_PRIO_2,OS_LOWEST_PRIO_1,OS_LOWEST_PRIO_0。

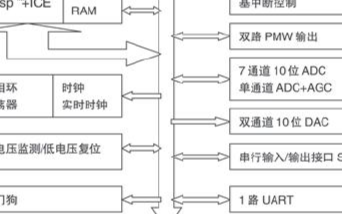

凌陽16位處理器μ′nSPTM被廣泛應用在家用電器控制器、儀器儀表、工業控制、娛樂和語音控制等場合。在功耗控制方面,μ′nSPTM采用CMOS制造工藝,同時增加了軟件激發的弱振方式、空閑方式和掉電方式,極大地降低了其功耗。可以通過對P SystemClock的設置進行選擇CPU的時鐘可以在O.32~49.152 MHz范圍內可編程調節。當系統處于備用狀態下(時鐘處于停止狀態),耗電僅為2μA@3.6 V。μ′nSPTM處理器滿足μCOS-Ⅱ實時操作系統移植的條件。

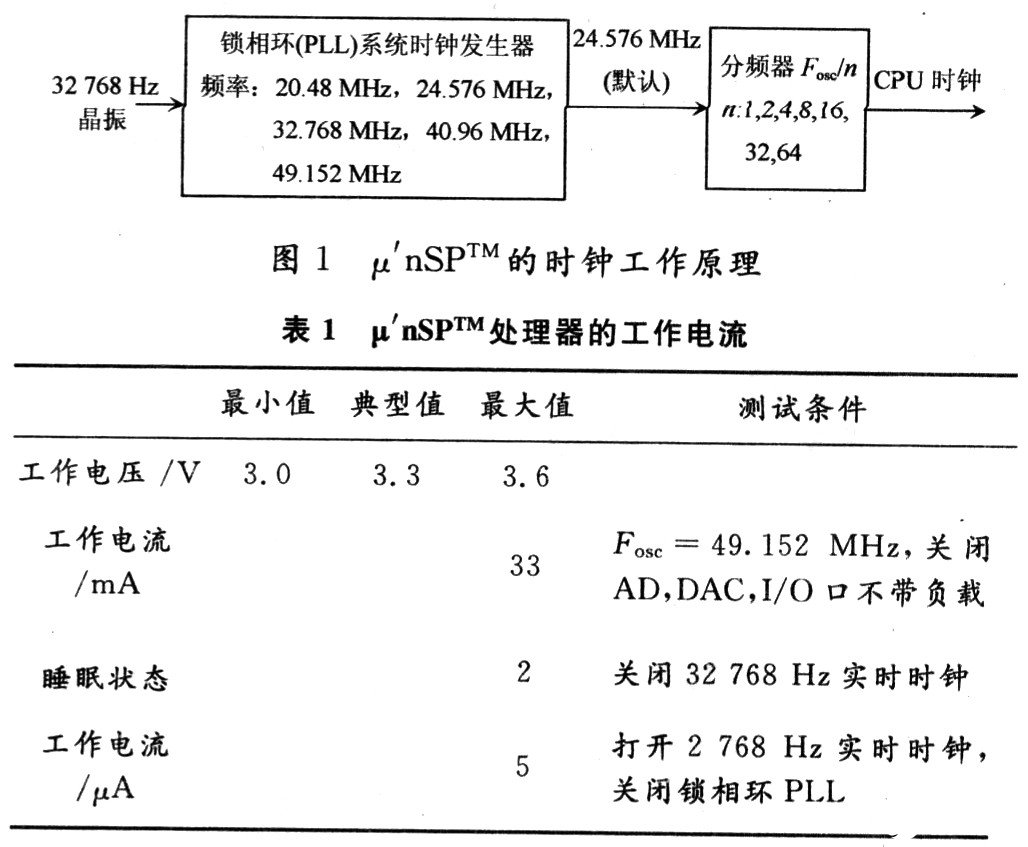

凌陽16位處理器μ′nSPTM的時鐘有多種選擇。系統采用32 768 Hz的實時時鐘,實時時鐘經過PLL倍頻電路以后,產生系統時鐘頻率FOSC,FOSC再經過分頻得到CPU時鐘頻率。其工作原理如圖1所示。

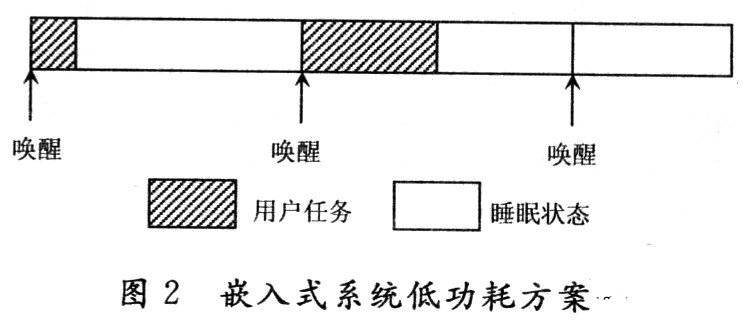

由圖1可知:μ′nSPTM的時鐘有多種選擇,從O.32~49.152 MHz范圍內可編程調節,另外還可以關閉32 768 Hz實時時鐘進入睡眠狀態。在3.6 V電源電壓下,處理器的工作電流見表1。

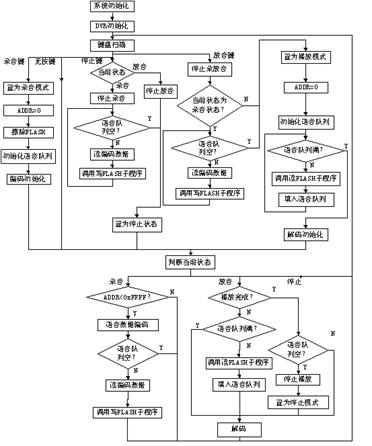

4 μCOS-Ⅱ實現低功耗的原理

μCOS-Ⅱ總是運行進入就緒狀態的優先級最高的任務。一旦優先級高的任務進入就緒態,就可以將CPU從低優先級任務中搶過來。在μCOS-Ⅱ初始化時,會建立一個優先級最低的任務——空閑任務,在沒有任務進入就緒態的時候,空閑任務就會開始運行。空閑任務會調用一個函數——OSTaskIdleHook()。這是留給用戶使用的內核擴展接口。空閑任務實際上并沒有什么事情可做,只是一個等待中斷的無限循環。因此用戶可以利用OSTaskIdleHook(),降低或者關閉系統時鐘,使CPU進入低功耗模式。在實際的測試中,可修改文件OS_CPU_A.ASM,添加控制實時時鐘的例程,然后在應用程序或函數OSTaskIdleHook()中調用,這樣更便于程序閱讀。

在本文中采用的具體方法有兩種:

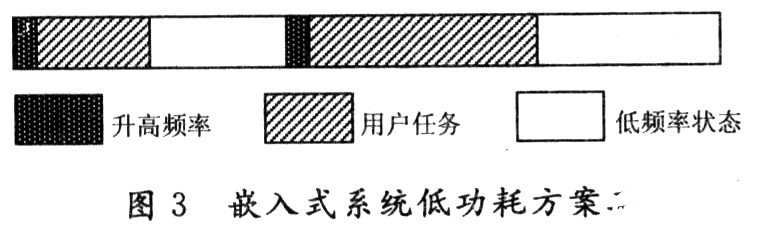

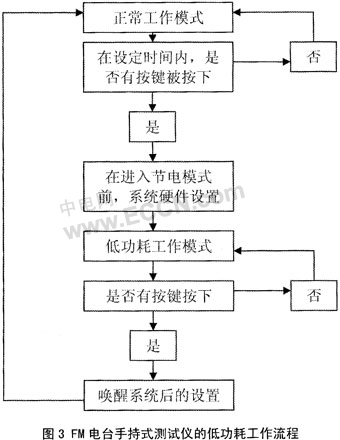

方案一:系統在空閑狀態下關閉實時時鐘,進入低功耗狀態。但這種方法會使操作系統停止運行而無法進行任務調度,故需要定時器周期性地喚醒CPU。CPU被喚醒之后重新判斷是否有任務處于就緒態,如果有就執行該任務;如果沒有則再次進入空閑狀態并關閉實時時鐘進入低功耗狀態。其工作時序見圖2。其中用戶任務工作在高功耗狀態,空閑任務則關閉實時時鐘,處于低功耗狀態。

方案二:系統在空閑狀態下不關閉實時時鐘,而是進入最低的工作頻率,此時處理器處于低功耗工作狀態,操作系統仍然可以進行任務調度。當有用戶任務時,由用戶任務先把實時時鐘頻率升高,然后再運行用戶代碼。其工作時序見圖3。其中每次進入用戶任務之前,先將實時時鐘頻率升高,用戶任務運行結束進入空閑狀態時,再將實時時鐘頻率降低。

1)測試和方案對比:

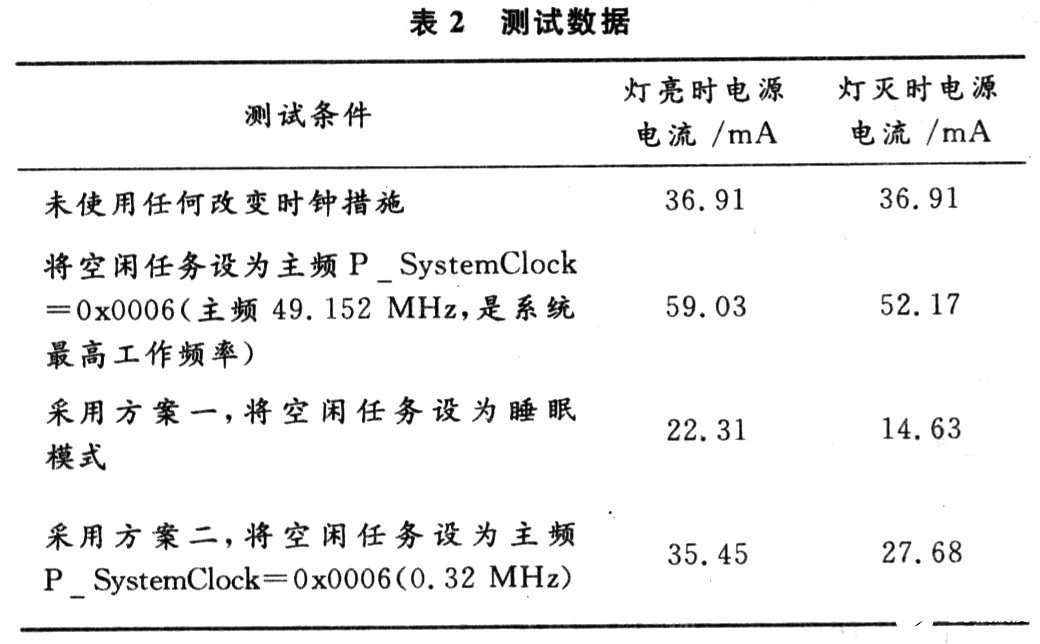

首先在處理器μ′nSPTM處理器上移植μCOS-Ⅱ實時操作系統。運行正常后測試用的用戶任務是以1 Hz的頻率點亮LED指示燈。表2是測試數據(外電源電壓4.82 V,穩壓后處理器電壓3.3 V)。

2)測試結論:

雖然以整機電流進行測試不能完全反映處理器的工作情況,但從以上數據可以知道,采用兩種方案確實可以降低系統功耗,而且方案一的效果更好,但需要占用一個定時器,在測試中發現當任務增加后功耗很快達到方案二水平,且有時不能正常喚醒;方案二很穩定,而且不需要定時器,用戶可以根據任務的運算量設定不同的時鐘頻率,如需要大的運算任務,可在進入用戶任務之前將時鐘頻率設置為較高值,反之設置為較低值。以上采用的方法只是動態地改變系統的頻率,沒有動態地改變電壓水平,因此在降低嵌入式系統功耗方面依然有進一步的潛力。但動態改變電壓水平需要更多硬件支持,在目前廣泛使用的中低端處理器中,通過擴展實時操作系統內核動態地改變系統的頻率對降低嵌入式系統功耗是大有裨益的。

5 結 語

在嵌入式系統設計中,由于普遍存在CPU高速運行功能和有限任務處理要求的巨大差異,會形成系統在時間與空間上巨大的無效操作。如果能夠根據系統的工作狀態自動地進行功耗管理,使系統工作于系統狀態相適應的功耗模式,故能極大地降低系統功耗,延長電池待機時間。這些工作對嵌入式開發有重大的意義。

責任編輯:gt

-

集成電路

+關注

關注

5389文章

11576瀏覽量

362387 -

嵌入式

+關注

關注

5087文章

19149瀏覽量

306233 -

低功耗

+關注

關注

10文章

2409瀏覽量

103787

發布評論請先 登錄

相關推薦

如何使用凌陽SPCE061A設計嵌入式應用系統?

用SPCE061A 設計的嵌入式語音通信平臺

SPCE061A在智能家居系統中的應用

使用凌陽SPCE061A的嵌入式應用系統設計

采用SPCE061A設計的SIO實現數碼錄音及播放

基于μC/OS-II操作系統在SPCE061A上的移植優化研研究

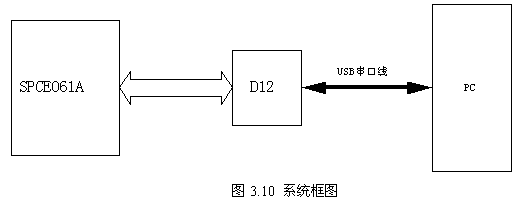

基于SPCE061A和PDIUSBD12USB接口芯片實現設備系統的設計

基于μCOS-Ⅱ在SPCE061A開發板上如何實現低功耗嵌入式系統的設計

基于μCOS-Ⅱ在SPCE061A開發板上如何實現低功耗嵌入式系統的設計

評論