FPGA(Field Programmable Gate Array)現(xiàn)場(chǎng)可編程門陣列,作為ASIC領(lǐng)域中的一種半定制電路而出現(xiàn)已有30年的歷史了,它既解決了定制電路的無(wú)法改變功能的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn),可應(yīng)用的場(chǎng)景也很廣泛。

就在2017年1月20日,騰訊云推出國(guó)內(nèi)首款高性能異構(gòu)計(jì)算基礎(chǔ)設(shè)施——FPGA云服務(wù),利用云服務(wù)的方式將只有大型公司才能長(zhǎng)期支付使用的FPGA服務(wù)推廣到了更多企業(yè)。企業(yè)可以通過(guò)FPGA云服務(wù)器進(jìn)行FPGA硬件編程,可將性能提升至通用CPU服務(wù)器的30倍以上。同時(shí),與已經(jīng)深入人心的高性能計(jì)算的代表GPU相比,F(xiàn)PGA具有硬件可編程、低功耗、低延時(shí)的特性,代表了高性能計(jì)算的未來(lái)發(fā)展趨勢(shì)。

而在人工智能(AI)里面火熱的深度學(xué)習(xí)領(lǐng)域,企業(yè)同樣可以將FPGA用于深度學(xué)習(xí)的檢測(cè)階段,與主要用于訓(xùn)練階段的GPU互為補(bǔ)充,F(xiàn)PGA還可應(yīng)用于金融分析、圖像視頻處理、基因組學(xué)等需要高性能計(jì)算的領(lǐng)域,是這類對(duì)效率要求高的行業(yè)應(yīng)用的最佳選擇。

基于此,InfoQ采訪了由騰訊云基礎(chǔ)產(chǎn)品中心、騰訊架構(gòu)平臺(tái)部組成的騰訊云FPGA聯(lián)合團(tuán)隊(duì),向讀者介紹FPGA的基本原理和設(shè)計(jì)初衷,應(yīng)用場(chǎng)景以及它給行業(yè)帶來(lái)的價(jià)值。

騰訊云FPGA的開(kāi)發(fā)歷史及背后的團(tuán)隊(duì)力量

隨著芯片制程逼近理論極限,可以預(yù)見(jiàn)通用處理器(CPU)性能提升空間越來(lái)越有限。而騰訊自己的業(yè)務(wù)隨著移動(dòng)互聯(lián)網(wǎng)的快速增長(zhǎng),數(shù)據(jù)體量的急劇膨脹,伴隨著對(duì)這些數(shù)據(jù)的計(jì)算需求也在迅猛上漲。騰訊在2013年開(kāi)始考慮如何解決計(jì)算需求的增長(zhǎng),而FPGA作為一種可編程的加速硬件彼時(shí)進(jìn)入了大家的視野。有了解決計(jì)算需求的想法后,需要通過(guò)實(shí)踐驗(yàn)證FPGA實(shí)際的能力。

騰訊的QQ、微信業(yè)務(wù),用戶每天產(chǎn)生的圖片數(shù)量都是數(shù)億級(jí)別,常用的圖片格式有JPEG格式、WebP格式等,WebP圖片格式比JPEG圖片格式存儲(chǔ)空間小30%。為節(jié)省存儲(chǔ)空間,降低傳輸流量,提升用戶的圖片下載體驗(yàn),通常采用WebP格式進(jìn)行存儲(chǔ)及傳輸分發(fā),而圖片轉(zhuǎn)碼所帶來(lái)的計(jì)算消耗需要上萬(wàn)臺(tái)CPU機(jī)器支撐。自然FPGA開(kāi)發(fā)落地的第一個(gè)切入點(diǎn)就是圖片轉(zhuǎn)碼:將JPEG圖片格式轉(zhuǎn)成WebP圖片格式。

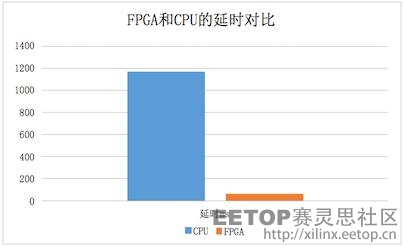

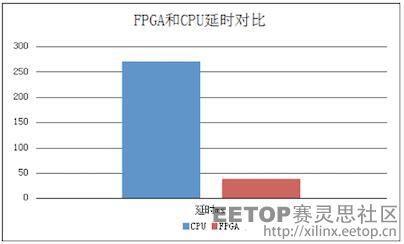

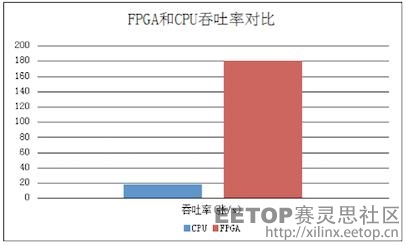

在圖片轉(zhuǎn)碼的實(shí)踐中,F(xiàn)PGA聯(lián)合團(tuán)隊(duì)取得了FPGA處理延時(shí)相比CPU降低20倍,F(xiàn)PGA處理性能是CPU機(jī)器的6倍,驗(yàn)證了FPGA能進(jìn)行計(jì)算加速的能力,同時(shí)也增強(qiáng)了FPGA聯(lián)合團(tuán)隊(duì)的自信心。

(圖1)圖片轉(zhuǎn)碼中FPGA和CPU延時(shí)對(duì)比

(圖2)圖片轉(zhuǎn)碼中FPGA和CPU吞吐率對(duì)比

圖片轉(zhuǎn)碼項(xiàng)目完成后,深度學(xué)習(xí)映入了FPGA聯(lián)合團(tuán)隊(duì)的眼簾,一方面深度學(xué)習(xí)需要密集的計(jì)算,另一方面深度學(xué)習(xí)在未來(lái)應(yīng)用上有著巨大的商業(yè)價(jià)值。深度學(xué)習(xí)基于深度神經(jīng)網(wǎng)絡(luò)理論,用在圖片分類的神經(jīng)網(wǎng)絡(luò)是其中的一個(gè)分支:卷積神經(jīng)網(wǎng)絡(luò)(CNN)。團(tuán)隊(duì)使用FPGA對(duì)CNN計(jì)算進(jìn)行加速,增強(qiáng)違規(guī)圖片檢測(cè)能力,最終在深度學(xué)習(xí)的實(shí)踐中取得了FPGA處理性能是CPU機(jī)器4倍的戰(zhàn)績(jī)。

騰訊云FPGA項(xiàng)目實(shí)踐的結(jié)果,見(jiàn)證了FPGA在數(shù)據(jù)中心里可以提供強(qiáng)大的計(jì)算能力和足夠的靈活性,來(lái)應(yīng)對(duì)數(shù)據(jù)中心對(duì)硬件加速的挑戰(zhàn)。經(jīng)過(guò)之前的FPGA實(shí)踐,F(xiàn)PGA聯(lián)合團(tuán)隊(duì)獲得了在數(shù)據(jù)中心使用FPGA的經(jīng)驗(yàn),未來(lái)也將在數(shù)據(jù)中心的計(jì)算、網(wǎng)絡(luò)、存儲(chǔ)三個(gè)方向進(jìn)一步探索,重構(gòu)數(shù)據(jù)中心基礎(chǔ)架構(gòu)。

云端的數(shù)據(jù)中心業(yè)務(wù)日新月異,更需要一種高性能、高靈活的底層硬件結(jié)構(gòu),所以FPGA聯(lián)合團(tuán)隊(duì)通過(guò)云端開(kāi)放FPGA計(jì)算服務(wù),從硬件層面加速云計(jì)算在各個(gè)場(chǎng)景中的應(yīng)用,降低企業(yè)的使用門檻和成本。

FPGA的特點(diǎn)解析

2016年3月,英特爾宣布正式停用“Tick-Tock”處理器研發(fā)模式,未來(lái)研發(fā)周期將從兩年向三年轉(zhuǎn)變。至此,摩爾定律對(duì)英特爾幾近失效。一方面處理器性能再無(wú)法按照摩爾定律進(jìn)行增長(zhǎng),另一方面數(shù)據(jù)增長(zhǎng)對(duì)計(jì)算性能要求超過(guò)了按“摩爾定律”增長(zhǎng)的速度。

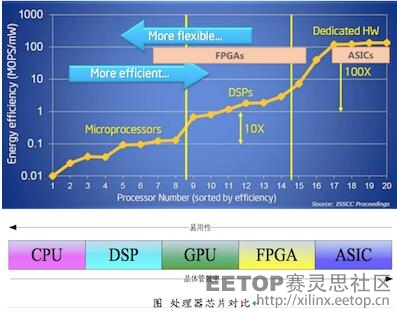

CPU本身無(wú)法滿足高性能計(jì)算應(yīng)用軟件的性能需求,導(dǎo)致需求和性能之間出現(xiàn)了缺口。在新的芯片材料等基礎(chǔ)技術(shù)沒(méi)有取得突破前,一種有效的解決方法就是采用專用協(xié)處理器的異構(gòu)計(jì)算方式來(lái)提升處理性能。現(xiàn)有的協(xié)處理器主要有FPGA,GPU和ASIC,F(xiàn)PGA由于其獨(dú)特的架構(gòu)擁有其他處理器無(wú)法比擬的優(yōu)勢(shì)。

FPGA(Field Programmable Gate Array)現(xiàn)場(chǎng)可編程門陣列,可以通過(guò)軟件重新配置芯片內(nèi)部的資源形成不同功能硬件,就像用樂(lè)高積木可以搭出航空母艦或變形金剛一樣。因此,F(xiàn)PGA不僅有了軟件的可編程性和靈活性,同時(shí)又有ASIC高吞吐和低延時(shí)的特性。而且,由于有豐富的IO,F(xiàn)PGA還非常適合用作協(xié)議和接口轉(zhuǎn)換的芯片。

FPGA在數(shù)據(jù)中心最大的特點(diǎn)就在高吞吐的同時(shí)能做到低延時(shí)。FPGA內(nèi)部的資源都是可以重配置的,因此它可以很容易進(jìn)行數(shù)據(jù)并行和流水并行,且易于在數(shù)據(jù)并行和流水并行之間平衡。而GPU幾乎只能做數(shù)據(jù)并行。

與ASIC相比,F(xiàn)PGA的可編程性體現(xiàn)出很大的優(yōu)勢(shì)。現(xiàn)在數(shù)據(jù)中心的各種算法每時(shí)每刻都在更新變化,沒(méi)有足夠穩(wěn)定的時(shí)間讓ASIC完成長(zhǎng)周期的開(kāi)發(fā)。比如在一種神經(jīng)網(wǎng)絡(luò)模型出來(lái)之后開(kāi)始把它做成ASIC,也許還未投片生產(chǎn),這個(gè)神經(jīng)網(wǎng)絡(luò)模型已經(jīng)被另一種神經(jīng)網(wǎng)絡(luò)模型所替代。不同的是,F(xiàn)PGA可以在不同的業(yè)務(wù)需求之間做平衡。比如說(shuō)白天用于為搜索業(yè)務(wù)排序的機(jī)器;在晚上請(qǐng)求很少的情況下,可以將這些FPGA重新配置成離線數(shù)據(jù)分析的功能,提供對(duì)離線數(shù)據(jù)進(jìn)行分析的服務(wù)。

另外由于FPGA有高速SERDES等豐富的接口,而且能靈活控制實(shí)現(xiàn)的粒度和操作數(shù)據(jù),因此非常適合進(jìn)行協(xié)議處理和數(shù)據(jù)格式的轉(zhuǎn)換。比如說(shuō)FPGA可以很方便的接入以太網(wǎng)數(shù)據(jù),并對(duì)以太網(wǎng)包進(jìn)行包過(guò)濾等處理。

和CPU、GPU、ASIC在設(shè)計(jì)上的區(qū)別

(圖3)處理器芯片對(duì)比

CPU/GPU 屬于馮·諾依曼結(jié)構(gòu),任務(wù)執(zhí)行需要經(jīng)歷取指、譯碼、執(zhí)行、訪存以及寫回等過(guò)程。CPU為達(dá)到足夠高的通用性,其指令流的控制邏輯相當(dāng)復(fù)雜。GPU使用SIMD單指令多數(shù)據(jù)流并行等方式進(jìn)行計(jì)算加速。

FPGA/ASIC在使用時(shí)硬件功能模塊已固定,無(wú)需分支判斷等復(fù)雜控制邏輯,同時(shí)大大降低了訪存次數(shù)。因此在能效上可以比 CPU 高出1到2個(gè)數(shù)量級(jí)。

ASIC是一種專用的芯片,是為了某種特定的需求而專門定制的芯片。ASIC與通用芯片相比,體積小、功耗低、計(jì)算效率高、芯片出貨量越大成本越低。但是缺點(diǎn)也很明顯:開(kāi)發(fā)周期很長(zhǎng),算法是固定的,一旦算法變化就可能無(wú)法重用。

而FPGA則是“軟硬件一體”的架構(gòu),軟件就是硬件。FPGA基本原理是在芯片內(nèi)集成大量的數(shù)字門電路以及存儲(chǔ)器,用戶可以通過(guò)燒入 FPGA 配置文件來(lái)來(lái)定義這些門電路以及存儲(chǔ)器之間的連線,進(jìn)而得到不同的硬件功能。

就開(kāi)發(fā)難度而言,ASIC 》 FPGA 》 GPU 》 CPU。目前主流的FPGA開(kāi)發(fā)語(yǔ)言是硬件描述HDL,需要開(kāi)發(fā)者具備一定的相關(guān)技能。隨著業(yè)界OPENCL、HLS等類C高級(jí)語(yǔ)言的推進(jìn),F(xiàn)PGA的開(kāi)發(fā)難度和周期也會(huì)有所改善。

FPGA 部署在哪里?與 CPU 之間如何通信?

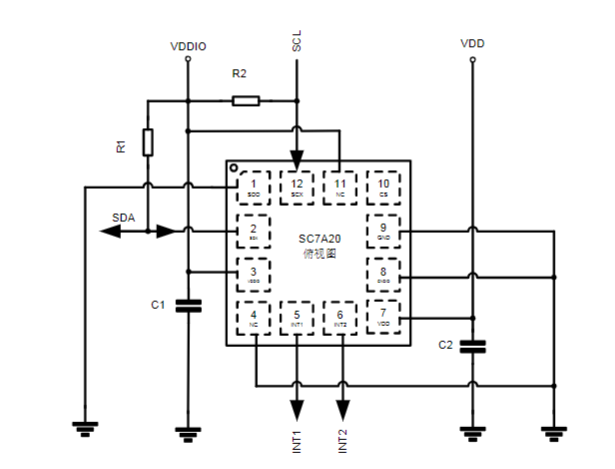

騰訊云的FPGA主要部署在數(shù)據(jù)中心的服務(wù)器中。騰訊云將FPGA芯片加上DDR內(nèi)存、外圍電路和散熱片,設(shè)計(jì)成PCIE板卡。這種FPGA板卡被安裝在服務(wù)器的主板上,用戶通過(guò)網(wǎng)絡(luò)遠(yuǎn)程訪問(wèn)服務(wù)器,開(kāi)發(fā)調(diào)試FPGA,并用其加速特定業(yè)務(wù)。

FPGA與CPU之間是通過(guò)PCIE鏈路通信的。CPU內(nèi)部集成了DDR內(nèi)存控制器和PCIE控制器。在FPGA芯片內(nèi)部也用可編程邏輯資源實(shí)現(xiàn)了PCIE控制器、DDR控制器和DMA控制器。一般通訊分三種情況:

(1)指令通道

CPU向FPGA芯片寫入指令,讀取狀態(tài)。CPU直接通過(guò)PCIE訪問(wèn)到FPGA芯片內(nèi)掛載的存儲(chǔ)器或內(nèi)部總線。

(2)數(shù)據(jù)通道

CPU讀寫FPGA板卡上DDR的數(shù)據(jù)時(shí),CPU通過(guò)PCIE配置FPGA芯片內(nèi)的DMA控制器,輸入數(shù)據(jù)的源物理地址和目的物理地址。DMA控制器控制FPGA卡上的DDR控制器和PCIE控制器,在FPGA卡上的DDR內(nèi)存和CPU連接的DDR內(nèi)存之間傳輸數(shù)據(jù)。

(3)通知通道

FPGA通過(guò)PCIE向CPU發(fā)送中斷請(qǐng)求,CPU收到中斷請(qǐng)求后保存當(dāng)前工作現(xiàn)場(chǎng),然后轉(zhuǎn)入中斷處理程序執(zhí)行,必要時(shí)會(huì)關(guān)閉中斷執(zhí)行中斷處理程序。CPU執(zhí)行完中斷處理程序后,會(huì)重新打開(kāi)中斷,然后重載到之前的工作現(xiàn)場(chǎng)繼續(xù)執(zhí)行。

目前FPGA行業(yè)面臨的問(wèn)題

在行業(yè)內(nèi),微軟在數(shù)據(jù)中心使用FPGA架構(gòu),Amazon也推出了FPGA的計(jì)算實(shí)例,那么是不是說(shuō)明整個(gè)行業(yè)對(duì)FPGA的使用比較廣泛呢?實(shí)際上,F(xiàn)PGA是個(gè)硬件芯片,它本身不能直接使用,也缺乏類似操作系統(tǒng)這樣的系統(tǒng)軟件支持。長(zhǎng)期以來(lái),F(xiàn)PGA行業(yè)在數(shù)據(jù)計(jì)算加速方向可以分為以下幾個(gè)參與方:

1. 芯片原廠:Xilinx和Altera(已被Intel收購(gòu))提供FPGA的芯片,直供或者給代理商分銷。

2. IP提供商:提供各種功能的IP,比如訪問(wèn)DDR內(nèi)存的IP,支持PCIE設(shè)備的IP,圖片編解碼的IP。一些共同的通用IP由芯片原廠提供。

3. 集成商:集成商提供硬件和軟件的支持。由于直接用戶缺乏硬件設(shè)計(jì)和制造能力,往往希望集成商提供成熟完善的硬件,并完成IP的集成,提供驅(qū)動(dòng)和使用方式,方便最終用戶的使用。

4. 用戶:最終使用者。在數(shù)據(jù)中心領(lǐng)域,用戶一般目的是希望使用FPGA對(duì)計(jì)算進(jìn)行加速。

在FPGA行業(yè),芯片原廠并不提供直接使用的硬件板卡,這個(gè)工作由集成商完成。由于硬件板卡使用量小和分擔(dān)設(shè)計(jì)、生產(chǎn)成本,硬件板卡價(jià)格往往高于芯片價(jià)格,甚至達(dá)到十倍之多。

IP提供商因?yàn)閾?dān)心產(chǎn)權(quán)泄露,通常不會(huì)迅速提供可用的可執(zhí)行文件(網(wǎng)表文件)給用戶,而是需要簽署一系列的協(xié)議和法律文件,甚至有的IP提供商根本不提供給用戶測(cè)試的機(jī)會(huì)。這樣就造成最終用戶很難得到可用的硬件板卡,更難以及時(shí)獲得使用最新工藝芯片的硬件板卡,造成用戶無(wú)法快速對(duì)不同IP進(jìn)行驗(yàn)證,從而挑選適合自身業(yè)務(wù)的IP。另外,F(xiàn)PGA的開(kāi)發(fā)使用硬件描述語(yǔ)言,缺乏軟件領(lǐng)域非常廣泛使用的框架概念,導(dǎo)致開(kāi)發(fā)周期漫長(zhǎng)。一般來(lái)說(shuō),F(xiàn)PGA開(kāi)發(fā)周期是軟件開(kāi)發(fā)的三倍左右。

綜上所述的這些問(wèn)題,決定了云對(duì)FPGA行業(yè)的顛覆和革命。

騰訊云FPGA平臺(tái)具體能解決哪些問(wèn)題

騰訊云FPGA平臺(tái)解決的是FPGA整個(gè)行業(yè)的一些問(wèn)題。FPGA用戶比較少,屬于一個(gè)相對(duì)封閉的圈子,F(xiàn)PGA開(kāi)發(fā)門檻高、開(kāi)源的優(yōu)質(zhì)IP比較缺乏、芯片價(jià)格昂貴等問(wèn)題一直為大家所詬病。

針對(duì)開(kāi)發(fā)者,騰訊云FPGA平臺(tái)提供了FPGA的底層硬件支撐平臺(tái),類似操作系統(tǒng)的部分功能,簡(jiǎn)化了開(kāi)發(fā)者對(duì)底層通用設(shè)備的訪問(wèn),比如DDR和PCIE這些通用設(shè)備,可以使開(kāi)發(fā)者更聚焦到業(yè)務(wù)功能的開(kāi)發(fā)。

FPGA 行業(yè)內(nèi)的IP提供者和使用者缺乏一個(gè)公開(kāi)的交易平臺(tái)和信用保證機(jī)制,IP交易環(huán)節(jié)冗長(zhǎng),價(jià)格不透明,很難達(dá)成交易,獲取 IP 后還需要搭建硬件平臺(tái)來(lái)驗(yàn)證IP性能,這些都嚴(yán)重影響產(chǎn)品上市進(jìn)程,經(jīng)常耗時(shí)幾個(gè)月之久。騰訊云提供了FPGA IP商店,IP開(kāi)發(fā)者和IP提供商可以通過(guò)FPGA IP商店為其他客戶無(wú)償或有償?shù)靥峁〧PGA IP和對(duì)應(yīng)的測(cè)試程序。這些IP都是基于騰訊云FPGA的標(biāo)準(zhǔn)硬件來(lái)開(kāi)發(fā)定制的,IP的驗(yàn)證和測(cè)試可以很方便地在云平臺(tái)上完成,一個(gè)IP的交易可以由幾個(gè)月縮短到一天之內(nèi),提高交易效率,也使得IP交易變得更加透明。

針對(duì)一些希望使用低延時(shí)的高質(zhì)量計(jì)算服務(wù)的小型公司而言,可以使用FPGA云計(jì)算加速服務(wù),不用耗費(fèi)大量人力進(jìn)行高性能計(jì)算方面的開(kāi)發(fā),很簡(jiǎn)單地就可以把高性能的云計(jì)算服務(wù)集成到自己的網(wǎng)絡(luò)平臺(tái),達(dá)到提升用戶體驗(yàn)的目的。比如:低延時(shí)的圖片格式轉(zhuǎn)換、基于深度學(xué)習(xí)的圖片分類等服務(wù),類似的服務(wù)后續(xù)還會(huì)進(jìn)一步豐富。

對(duì)于學(xué)校的FPGA教學(xué)而言,以前學(xué)校需要為每個(gè)學(xué)生購(gòu)買一個(gè)開(kāi)發(fā)板卡,有了騰訊云平臺(tái)之后可以節(jié)省學(xué)校購(gòu)買開(kāi)發(fā)板的成本,現(xiàn)在只需要給每個(gè)學(xué)生申請(qǐng)一個(gè)FPGA云平臺(tái)的賬戶即可,學(xué)生登錄上去直接可以根據(jù)demo進(jìn)行學(xué)習(xí)開(kāi)發(fā)即可。騰訊云平臺(tái)同時(shí)會(huì)為用戶提供便于學(xué)習(xí)的操作指導(dǎo)和實(shí)驗(yàn)課程方案,用戶學(xué)習(xí)的東西更接近企業(yè)的實(shí)際應(yīng)用場(chǎng)景,可以很好地跟將來(lái)的工作需要對(duì)接起來(lái)。

此外,大容量的FPGA芯片價(jià)格比較昂貴, 一個(gè)很重要的原因是FPGA芯片缺少量大的爆款產(chǎn)品,而騰訊云FPGA平臺(tái)可以聚集大量的客戶來(lái)使用騰訊的標(biāo)準(zhǔn)FPGA硬件設(shè)備,這樣會(huì)增大該FPGA芯片的供應(yīng)量,同時(shí)也便于芯片廠商降低成本,逐漸緩解FPGA芯片昂貴的問(wèn)題。

從這些可以看出FPGA云化意義重大,可以推動(dòng)整個(gè)FPGA行業(yè)的發(fā)展,給FPGA產(chǎn)業(yè)鏈的各方帶來(lái)收益。

FPGA在互聯(lián)網(wǎng)業(yè)務(wù)中的應(yīng)用優(yōu)勢(shì)

· 圖片轉(zhuǎn)碼

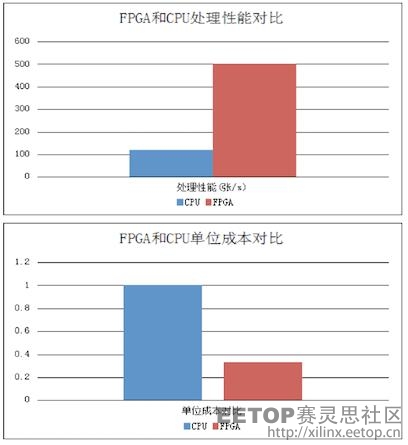

隨著移動(dòng)互聯(lián)網(wǎng)的發(fā)展,用戶每天上傳的圖片量越來(lái)越龐大,公司目前用于圖片轉(zhuǎn)碼的業(yè)務(wù)主要有QQ相冊(cè)、微信等,而業(yè)務(wù)中使用的圖片格式大都為JPEG格式、WebP格式等,而圖片轉(zhuǎn)碼所帶來(lái)的計(jì)算消耗需要上萬(wàn)臺(tái)CPU機(jī)器支撐。所以FPGA在互聯(lián)網(wǎng)業(yè)務(wù)中第一個(gè)應(yīng)用場(chǎng)景就是圖片轉(zhuǎn)碼:JPEG圖片格式轉(zhuǎn)成WebP圖片格式。項(xiàng)目取得了FPGA處理延時(shí)相比CPU降低了20倍,F(xiàn)PGA處理性能是CPU機(jī)器的6倍。

為了更進(jìn)一步提升圖片的壓縮率,同時(shí)隨著HEVC高性能編碼標(biāo)準(zhǔn)的發(fā)展,HEVC的I幀圖片壓縮率和之前的WebP/JPEG等編碼標(biāo)準(zhǔn)有了很大的提升,HEVC的I幀圖片壓縮率和WebP相比提高20~30%左右,和JPEG相比提高更多,平均能到50%左右,因此,無(wú)論從下載帶寬節(jié)省還是后臺(tái)存儲(chǔ)成本降低,以及用戶下載圖片體驗(yàn)等角度來(lái)看,HEVC標(biāo)準(zhǔn)都有很大優(yōu)勢(shì)。而采用HEVC的問(wèn)題在于HEVC 的幀壓縮計(jì)算復(fù)雜度非常高,采用CPU進(jìn)行轉(zhuǎn)碼成本很高,導(dǎo)致很難在業(yè)務(wù)中全面推廣。為了增強(qiáng)圖片轉(zhuǎn)碼能力,騰訊繼續(xù)使用FPGA對(duì)圖片轉(zhuǎn)碼進(jìn)行加速。

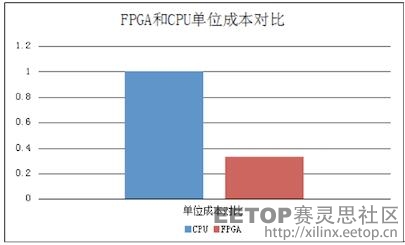

經(jīng)測(cè)試,完成WebP/JPEG格式圖片轉(zhuǎn)成HEVC格式圖片,測(cè)試圖片大小為1920x1080,F(xiàn)PGA處理延時(shí)相比CPU降低7倍,F(xiàn)PGA處理性能是CPU機(jī)器的10倍,F(xiàn)PGA機(jī)型單位成本是CPU機(jī)型的1/3。

· 圖片分類

深度學(xué)習(xí)近年來(lái)在語(yǔ)音識(shí)別、圖片分類和識(shí)別、推薦算法等領(lǐng)域發(fā)揮了越來(lái)越大的作用。在移動(dòng)互聯(lián)時(shí)代,為了增強(qiáng)圖片檢測(cè)的處理能力,降低圖片檢測(cè)成本,騰訊使用FPGA對(duì)CNN計(jì)算進(jìn)行加速。

研發(fā)團(tuán)隊(duì)使用FPGA完成CNN算法的Alexnet模型,F(xiàn)PGA處理性能是CPU機(jī)器的4倍,F(xiàn)PGA機(jī)型單位成本是CPU機(jī)型的1/3。

FPGA能讓開(kāi)發(fā)者/團(tuán)隊(duì)更“任性”

對(duì)于外部開(kāi)發(fā)者和開(kāi)發(fā)團(tuán)隊(duì)來(lái)說(shuō),首先,騰訊云FPGA提供統(tǒng)一的硬件平臺(tái)。開(kāi)發(fā)者無(wú)需關(guān)注 FPGA 基礎(chǔ)設(shè)施,免去了重復(fù)開(kāi)發(fā)硬件平臺(tái)面臨的問(wèn)題和挑戰(zhàn),快捷部署,幾分鐘就可以部署完畢一臺(tái)全新的FPGA平臺(tái)。FPGA芯片豐富的邏輯資源可以為開(kāi)發(fā)者“任性”實(shí)現(xiàn)功能提供保障。統(tǒng)一的平臺(tái)也便于開(kāi)發(fā)團(tuán)隊(duì)快速?gòu)椥詳U(kuò)展硬件平臺(tái),從而提高業(yè)務(wù)容災(zāi)可靠性。

其次,騰訊云FPGA提供完備的開(kāi)發(fā)環(huán)境,不需要專門人員開(kāi)發(fā)驅(qū)動(dòng)環(huán)境。開(kāi)發(fā)語(yǔ)言多樣性,HLS,OPENCL,RTL滿足不同類別的開(kāi)發(fā)人員需求,降低學(xué)習(xí)開(kāi)發(fā)門檻,簡(jiǎn)單易用。

再者,騰訊云FPGA提供豐富的IP功能,不僅有大量免費(fèi)IP和有償?shù)腎P服務(wù),而且交易流程透明、安全、可靠。加速開(kāi)發(fā)者開(kāi)發(fā)進(jìn)度的同時(shí)也為開(kāi)發(fā)團(tuán)隊(duì)提供一個(gè)將自己開(kāi)發(fā)的IP進(jìn)行交易的平臺(tái)。

最后,騰訊云FPGA提供專業(yè)安全防護(hù)。部署到云上,將享受與云服務(wù)器同等的云安全基礎(chǔ)防護(hù)和高防服務(wù)。免去傳統(tǒng)FPGA數(shù)據(jù)存儲(chǔ)和傳輸安全所帶來(lái)的困擾。

可以看到,傳統(tǒng)的FPGA開(kāi)發(fā)面臨的硬件平臺(tái)穩(wěn)定性、開(kāi)發(fā)語(yǔ)言門檻高、調(diào)試周期長(zhǎng)、驅(qū)動(dòng)軟件聯(lián)合調(diào)試等問(wèn)題都將得到改觀,開(kāi)發(fā)者和開(kāi)發(fā)團(tuán)隊(duì)能夠從繁雜和重復(fù)的工作中快速釋放出來(lái),有更多的時(shí)間和精力投入到創(chuàng)新的工作中去,這將為整個(gè)技術(shù)研發(fā)的氛圍增加更多的創(chuàng)新因子,創(chuàng)造更多的價(jià)值。

未來(lái),F(xiàn)PGA的行業(yè)價(jià)值

當(dāng)前AI火爆,得益于FPGA的高密度計(jì)算能力以及低功耗的特性,F(xiàn)PGA率先在深度學(xué)習(xí)在線預(yù)測(cè)方向(廣告推薦、圖片識(shí)別、語(yǔ)音識(shí)別等)得到了較大規(guī)模的部署。用戶也常常將FPGA與GPU進(jìn)行對(duì)比,GPU的易編程性、高吞吐與FPGA的低功耗、易部署等特性也各有千秋。相較于GPU以及ASIC,F(xiàn)PGA的低延時(shí)以及可編程性也是其核心競(jìng)爭(zhēng)能力。

對(duì)于行業(yè)來(lái)說(shuō),云是一種共享服務(wù)的思想,用戶不以占有的方式使用硬件和軟件,而是共享復(fù)用,因此大大降低了使用成本,提升了資源的使用效率。FPGA云服務(wù),可以讓行業(yè)參與方都獲得價(jià)值:

1. 芯片原廠:不需要經(jīng)過(guò)層層代理,增加成本,而是可以通過(guò)云提供硬件板卡復(fù)用的服務(wù)。因?yàn)橛布y(tǒng)一采購(gòu)和維護(hù),也大大提升了穩(wěn)定性和可靠性。

2. IP提供商:可以把IP放到云平臺(tái)的市場(chǎng)中去,最終用戶使用時(shí),云平臺(tái)完成部署和交付,用戶不需要接觸可執(zhí)行文件(網(wǎng)表文件),因此不存在產(chǎn)權(quán)泄露的風(fēng)險(xiǎn)。這將鼓勵(lì)I(lǐng)P提供商的服務(wù)方式,可以提供按時(shí)長(zhǎng)計(jì)費(fèi),買斷計(jì)費(fèi),乃至試用版免費(fèi)等方式,用戶也可以迅速驗(yàn)證。

3. 設(shè)計(jì)和開(kāi)發(fā):云提供框架方式,封裝了常用的系統(tǒng)級(jí)操作(DDR內(nèi)存的訪問(wèn)、DMA、PCIE設(shè)備控制等),可以支持硬件描述語(yǔ)言,也支持OPENCL以及類似C的高級(jí)語(yǔ)言。提供通用的驅(qū)動(dòng)和調(diào)用庫(kù),不需要用戶編程。對(duì)高階用戶而言,也可以使用OPENCL或者硬件描述語(yǔ)言實(shí)現(xiàn)自己的功能。

4. FPGA最初的應(yīng)用場(chǎng)景是在通信行業(yè),那么其高通信帶寬以及實(shí)時(shí)性處理能力可以為數(shù)據(jù)中心基礎(chǔ)架構(gòu)帶來(lái)什么改變呢?當(dāng)前,F(xiàn)PGA可以在IDC大顯神威的地方,例如低延時(shí)網(wǎng)絡(luò)架構(gòu)、網(wǎng)絡(luò)虛擬化、高性能存儲(chǔ)以及網(wǎng)絡(luò)安全等等。可喜的是,我們看到微軟以及亞馬遜等同行已經(jīng)使用FPGA在其公有云網(wǎng)絡(luò)中進(jìn)行了諸多積極嘗試,騰訊云當(dāng)前也在多個(gè)方向進(jìn)行積極的探索和實(shí)踐。

可以預(yù)見(jiàn)的是,借助于FPGA,我們的數(shù)據(jù)中心會(huì)更加的綠色高效。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605581

原文標(biāo)題:FPGA是如何實(shí)現(xiàn)30倍速度的云加速的?

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

云岑降壓型開(kāi)關(guān)充電CP2170規(guī)格書

加速度傳感器的工作原理

GPU加速云服務(wù)器怎么用的

使用LIS2DW12TR加速度傳感器可以計(jì)算物體重力方向運(yùn)動(dòng)的距離嗎

什么是AEC-Q102的恒定加速度測(cè)試?

FPGA加速深度學(xué)習(xí)模型的案例

TLV320AIC3109哪里有控制錄音速度的參數(shù)呢?

加速度傳感器的應(yīng)用

物聯(lián)網(wǎng)系統(tǒng)中加速度測(cè)試方案的實(shí)現(xiàn)_加速度傳感器分析

FPGA實(shí)現(xiàn)30倍速度云加速的方法

FPGA實(shí)現(xiàn)30倍速度云加速的方法

評(píng)論