作者:Kendall Castor-Perry

在一些關于驅動采樣ADC的文章中,談到了電阻和電容影響輸入端的穩定性。這個問題能被提出來是好事,但在我看來,處理方式似乎總是有點經驗主義,卻并沒解釋那些經驗從何而來。你們都想知道原因的,對吧?這里是我多年前做過的一些仿真試驗,相信可以對此作出一些解釋。

高速ADC將輸入電壓采樣到內部電容上,因此存在充電電流。在為電荷轉移保留的一小段采樣周期時間內,必須獲取快速變化的輸入電壓以實現高精確度。輸入端子和采樣開關之間通常沒有緩沖。因此,電荷流的時域性能由內部電容器和充電電流通路(包括芯片外部和內部)的阻抗之間形成的時間常數來確定。

充電過程不是由ADC設計人員或數據表編寫人員控制的。如果外部阻抗影響充電波形(讀數器亦如此)的穩定性,則可能阻礙輸入電壓在規定時間內達到足夠的精度。與電平和斜率相關的誤差也會隨之出現,甚至在低頻輸入信號上出現增益和線性問題。

這樣的ADC作為一個采樣數據系統卻不適合做連續瞬態分析——這真讓人驚訝!然而,采樣周期內的充電完全可以由等效輸入網絡對表示時鐘的電壓階躍輸入的響應來預測。用時鐘作為輸入信號,在時域中將組合的外部和內部網絡仿真為濾波器(嘿,想到這一點了嗎?),便可檢查外部元件的影響。這種方法在下一個時鐘邊緣之外是不準確的——但如果到那時系統還未穩定下來,那這個系統就會完全不準確。

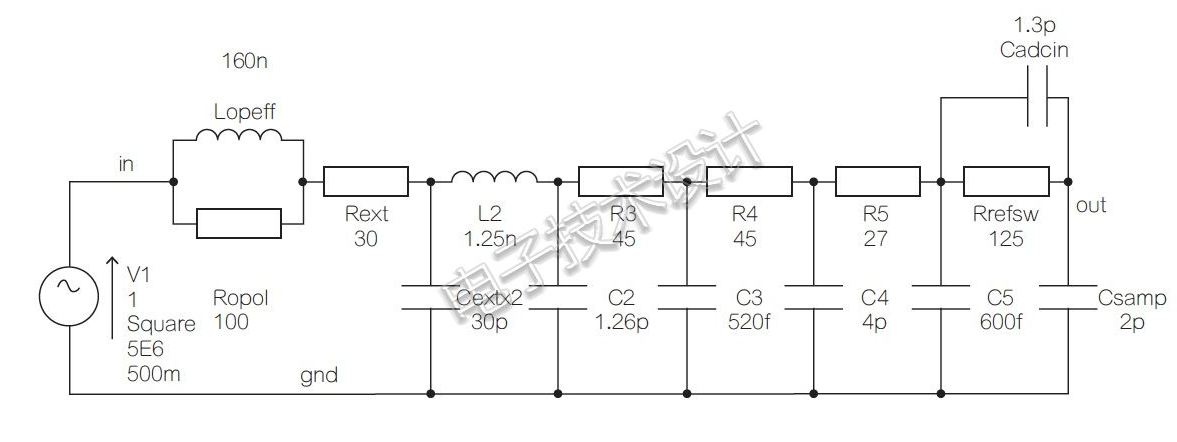

等效電路如圖1所示,它源自一款現在已經相當過時的Burr-Brown ADC的原理圖,其中有一個拓撲改變以方便仿真,即重新安排梯形電路的最后一個分支,讓2pF采樣電容接地;而且,整個電路是這個差分電路的單端等效電路。與外部元件相比,內部細節影響不大。

圖1:基本電路分析。

對于80MHz轉換器來說,輸入為5MHz方波是較慢的采樣速率,這說明外部元件值雖然看起來合理,但也可能導致不好的穩定性。文中的圖顯示了采樣電容器上電壓的穩定性。忽略三個時鐘周期中的第一個(仔細觀察它與其它周期的細微差別),我并沒有讓電路達到穩定狀態,好吧,這是我的錯。

這里展示了對三個參數的掃描:電容Cextx2、串聯電阻Rext和緩沖器Lopeff的有效電感(類似積分器的放大器噪聲增益帶寬將其輸出電阻Ropol轉換為電感)。

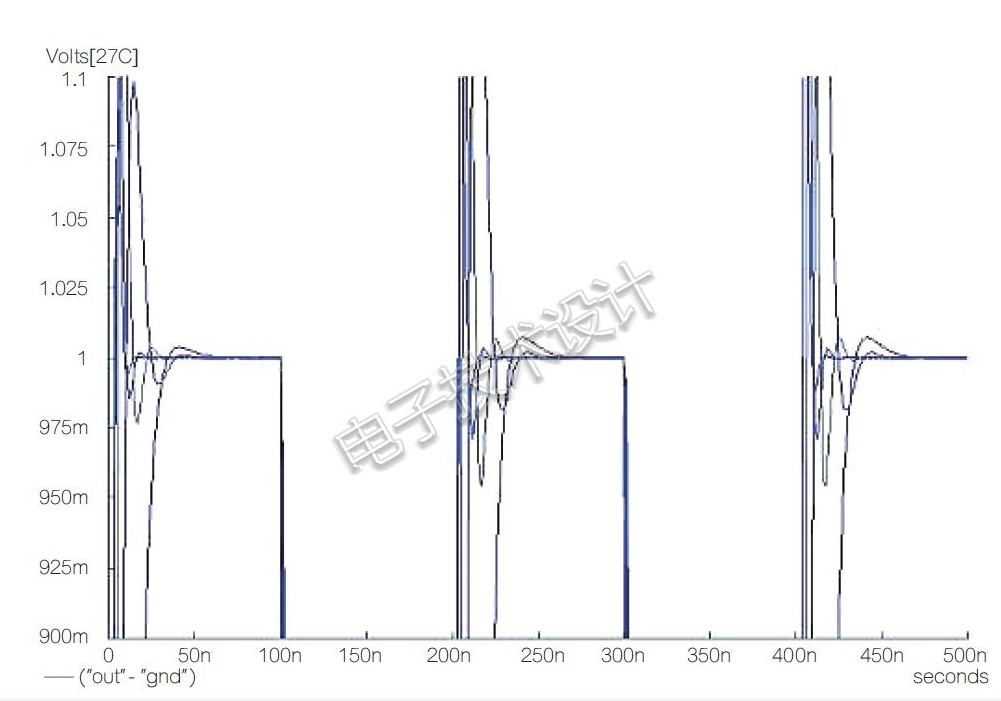

布局電感包括在內,但源阻抗的電感元件完全由驅動放大器的上升閉環輸出阻抗支配。改善這種系統的穩定性的主要原因是使用了寬帶放大器,而不是放大器輸出級能有效驅動ADC不良輸入阻抗這類略而不證的斷言。現在開始掃描。首先是電容Cextx2(圖2):

圖2:在3pF和300pF之間掃描輸入電容(最慢速度)。

隨著電容器數值的增加,波形受到的阻尼效果變得更好,但穩定所需的時間卻更長。這里,Rext=30Ω,Lopeff=160nH(對應具有100Ω開環Ropol和100MHz噪聲增益帶寬的放大器)。無論通過什么方法來改善實際波形,增大電容都將延長穩定時間。所以對于高速系統,應該使該電容盡可能小。接下來,我們掃描電阻Rext(圖3):

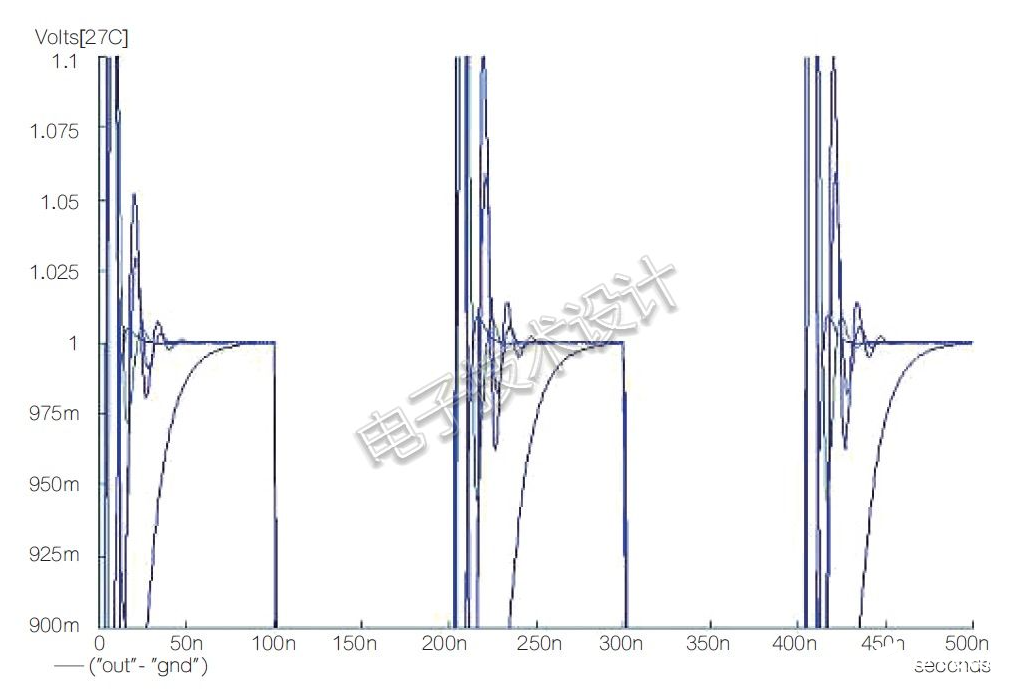

圖3:在3Ω和300Ω之間掃描外部電阻(最慢速度)。

掃描該電阻會改變外部RC時間常數,但由于串聯電壓下降,增大Rext比增大Cextx2具有更顯著的效果。這里Cextx2=30pF,Lopeff=160nH。增大電阻值改善了在輸入端形成的諧振電路阻尼,特別是當輸入電容值較小時,但這同時也降低了系統速度。由于源電感增加(即運算放大器的噪聲增益帶寬減小),電阻器數值也需要增大,以保持較好的采集波形。

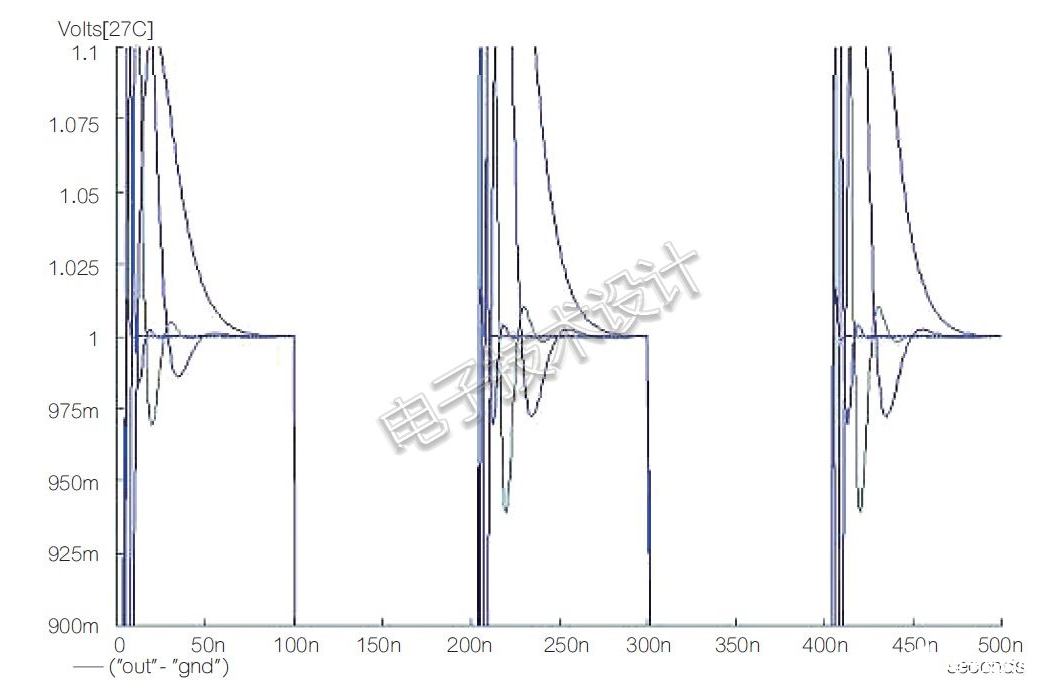

現在來看看電感——實際上我們是掃描放大器的GBW。圖4顯示了將放大器的噪聲增益帶寬從1000MHz降低到10MHz的影響,此時Rext=30Ω,Cextx2=30pF。如同所預料的,使用較慢的運算放大器顯著延長了穩定所需的時間。此外,較大的過沖可能會導致輸入極問題。

圖4:在16nH和1600nH之間掃描有效的源電感(最慢速度)。

隨著運算放大器GBW的降低,干凈采集時間(采用最恰當的Rext和Cextx2)也會增加,這表明較慢的緩沖放大器可能根本無法以所需的速度實現準確采集。波形的變化表明,如果三個主要外部元件中任意一個的值固定不變(比如運算放大器不能改變,或ADC有一個較大的Cin),就需要優化其他兩個元件來獲得良好的性能。值得注意的是,這個固定值的選擇有可能根本無法實現所需的穩定時間!

希望上面的分析能讓你明白問題可能出現在哪里,以及如何在系統中查找問題——親自嘗試一下吧!

編輯:hfy

-

電容器

+關注

關注

64文章

6224瀏覽量

99699 -

轉換器

+關注

關注

27文章

8707瀏覽量

147237 -

運算放大器

+關注

關注

215文章

4942瀏覽量

173001 -

adc

+關注

關注

98文章

6501瀏覽量

544756 -

波形

+關注

關注

3文章

379瀏覽量

31574

發布評論請先 登錄

相關推薦

影響BUCK電路占空比穩定性的因素

有源晶振與無源晶振穩定性比較:為何有源晶振更勝一籌?

三星貼片電容的封裝形式對穩定性影響大嗎?

鳳凰動力舵輪驅動輪的穩定性如何影響AGV的運行效率和穩定性

探討關于驅動采樣ADC的電阻和電容影響輸入端的穩定性

探討關于驅動采樣ADC的電阻和電容影響輸入端的穩定性

評論