SoC的全稱叫做:System-on-a-ChIP,中文意思是“把系統(tǒng)做在一個芯片上”,你可以想像成PC時代的電腦核心CPU,在智能終端時代,手機的核心就是這個SoC。

它包含了計算機上的大部分部件。顧名思義,這是一個在硅芯片上制造的整個系統(tǒng)。SoC的美妙之處在于它將所有組件集成在一個襯底上。在半導體中,襯底是用來制造集成電路的硅薄膜。與傳統(tǒng)主板相比,SoC將可更換部件集成到單個芯片上,從而減小了尺寸并提高了效率。與集成電路一起,SoC還包括用于集成的軟件和互連結(jié)構(gòu)。軟硬件集成方法使SoC體積更小,允許更少的功耗,并且比標準的多芯片系統(tǒng)更可靠。

是什么構(gòu)成了SoC

SoC可以分為以下類型:

1.圍繞微控制器構(gòu)建

2.圍繞微處理器構(gòu)建

3.針對特定應用構(gòu)建

一個SoC的組成包括:一個處理器,主、次存儲器和輸入/輸出端口。其他重要部件包括GPU、WiFi模塊、數(shù)字信號處理器(DSP)和各種外設(shè),如USB、以太網(wǎng)、串行外設(shè)接口(SPI)、ADC、DAC,甚至FPGA。通常,它有多個核。根據(jù)各種決定因素和偏好,核心可以是微控制器、微處理器、DSP,甚至是ASIP(應用程序特定指令集處理器)。ASIP有基于特定應用的指令集。

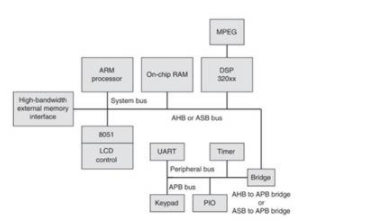

通常,SoC使用ARM體系結(jié)構(gòu),它屬于RISC,需要較少的數(shù)字設(shè)計,從而使其與嵌入式系統(tǒng)兼容。ARM架構(gòu)比8051這樣的處理器更節(jié)能,因為與使用CISC架構(gòu)的處理器相比,使用RISC架構(gòu)的處理器需要更少的晶體管。這也降低了散熱和成本。

下圖顯示了一個SoC框圖的示例。

處理器

SoC的核心是處理器。它通常有多個處理器核心。多核允許不同的進程同時運行,這提高了系統(tǒng)的速度,因為它使計算機可以同時執(zhí)行多個操作。基本上,操作系統(tǒng)將多個內(nèi)核視為多個cpu,從而提高了性能。當多個核心被安裝到同一個芯片上時,由于核心之間更快的通信,所以延遲就會更少。多核系統(tǒng)只有一個多核CPU插槽。

由于超線程,對于操作系統(tǒng),單核作為兩個邏輯單元出現(xiàn)。超線程允許在兩個cpu之間共享物理資源。

數(shù)字信號處理器(DSP)

DSP是一種針對數(shù)字信號處理的操作進行優(yōu)化的芯片。包括傳感器、執(zhí)行器、數(shù)據(jù)處理和數(shù)據(jù)分析的操作,它可用于圖像解碼。DSP的使用節(jié)省了其他處理任務的CPU周期,從而提高了性能。專用DSP更節(jié)能,這使得它們適合在SoC中使用。用于DSP核心的指令集是SIMD(單指令多數(shù)據(jù))和VLIW(超長指令字)。這種體系結(jié)構(gòu)的使用允許并行處理指令和超標量執(zhí)行。DSP用于執(zhí)行快速傅里葉變換、卷積、乘法累加等操作。

SoC上的內(nèi)存

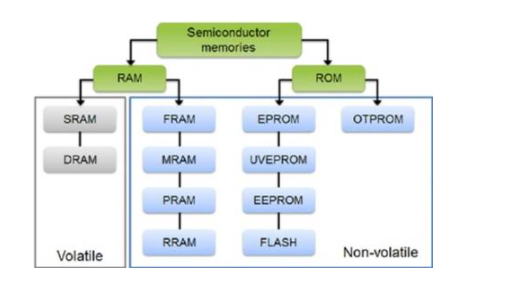

SoC有基于應用程序的內(nèi)存。這些存儲器是用于計算的半導體存儲器塊。半導體存儲器通常是指在單個硅片上制造的金屬氧化物半導體存儲器單元。內(nèi)存類型包括:

易失性存儲器:斷電后會丟失數(shù)據(jù)的存儲器。換句話說,它們需要恒定的電源來保存信息。易失性存儲器更快、更便宜,這也是被大眾所接受的原因。

RAM是一種易失性存儲器。最常用的RAM是SRAM和DRAM。SRAM由1、3或6個晶體管組成的存儲單元組成。相反,DRAM只有一個MOSFET和一個根據(jù)FET狀態(tài)進行充放電的電容。然而,DRAM容易受到電容泄漏電流的影響。DRAM的一個顯著優(yōu)點是它比SRAM便宜。如果一個SoC有一個緩存層次結(jié)構(gòu),SRAM被用于緩存,DRAM被用于主存儲器。這是因為與主存相比,高速緩存需要更快的內(nèi)存類型。

也有專為非易失性函數(shù)設(shè)計的RAM類型。例如FRAM,MRAM,它以磁性狀態(tài)存儲數(shù)據(jù),PRAM(參數(shù)隨機存取存儲器),它在Macintosh計算機中用于存儲系統(tǒng)設(shè)置,包括顯示和時區(qū)設(shè)置。除此之外,還有RRAM(電阻隨機存取存儲器),它有一個叫做記憶電阻的組件。記憶電阻是一種電阻,其電壓隨所施加的電壓而變化。

非易失性記憶:即使在沒有電源的情況下也能保留信息的記憶。ROM(只讀存儲器)是一種非易失性存儲器。ROM的類型包括EPROM(可擦可編程只讀存儲器),它是一組浮動柵晶體管。紫外線可擦可編程只讀存儲器(紫外線可擦可編程只讀存儲器),用紫外光擦除并重新編程數(shù)據(jù),EEPROM(電可擦可編程只讀存儲器)和閃存。

選擇的內(nèi)存類型取決于設(shè)計規(guī)范和應用程序。

片上通信

傳統(tǒng)上,總線體系結(jié)構(gòu)用于SoC的執(zhí)行單元之間的通信。然而,近年來,片上網(wǎng)絡互聯(lián)技術(shù)已經(jīng)成為一種取代總線架構(gòu)的趨勢。

總線通信的一個流行的例子是ARM的AMBA(高級微控制器總線體系結(jié)構(gòu))總線協(xié)議。總線體系結(jié)構(gòu)用于驅(qū)動組件之間的數(shù)據(jù)。片上總線體系結(jié)構(gòu)可分為共享總線、層次總線和環(huán)形拓撲結(jié)構(gòu)。不同的公司根據(jù)芯片的設(shè)計和應用設(shè)計了不同的架構(gòu)。例如Altera AVALON, IBM CORECONNECT, silicon ore Corporation的WISHBONE。

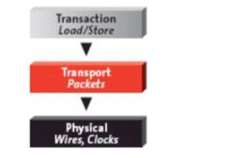

片上網(wǎng)絡采用系統(tǒng)級網(wǎng)絡技術(shù)進行片上流量管理。NOC是一種同構(gòu)、可擴展的交換結(jié)構(gòu)網(wǎng)絡,用于傳輸多用途數(shù)據(jù)包。這個體系結(jié)構(gòu)本質(zhì)上是通過用戶定義的技術(shù)分層。通信在三層通信方案上進行,即事務、傳輸和物理。

NOC互連結(jié)構(gòu)的目標是減少芯片上的線路路由擁塞,提供更好的時間閉合,對SoC設(shè)計進行各種IPs的標準化改變。NOC體系結(jié)構(gòu)已被證明更節(jié)能,并能滿足吞吐量要求。

外部接口

SoC接口會按預定的程序進行延遲。外部接口通常基于WiFi、USB、以太網(wǎng)、I2C、SPI、HDMI等通信協(xié)議。如果需要,可以添加模擬接口與傳感器和執(zhí)行器接口。

其他組件

對于一個功能完整的SoC來說,其他必要的組件包括時鐘、定時器、振蕩器、鎖相環(huán)系統(tǒng)、穩(wěn)壓器和電源管理單元等定時源。

SoC設(shè)計流程

SoC設(shè)計流程以架構(gòu)協(xié)同設(shè)計為目標,即同時設(shè)計硬件和軟件。設(shè)計流程必須考慮優(yōu)化目標和各種約束條件。下圖是一個從規(guī)范到制造的SoC設(shè)計流程示例,不同的團隊執(zhí)行制造SoC所涉及的每個步驟。

如今我們正在使用MOS技術(shù)制作SoC。最小的MOS技術(shù)是TSMC和三星共同開發(fā)的3nm技術(shù)。然而,今天的大多數(shù)器件都使用10nm技術(shù)。制作過程包括設(shè)計的網(wǎng)表生成,然后是物理設(shè)計流程。在整個過程中,需要特別注意靜態(tài)時序分析(STA),即數(shù)字電路中的時序計算。STA還用于驗證計時性能和檢查任何計時違反。當數(shù)字電路中的觸發(fā)器處于未知狀態(tài)(既不是1也不是0)時,時序違反會導致亞穩(wěn)態(tài)。

在制作步驟1中,分析設(shè)計規(guī)范,并生成執(zhí)行規(guī)范所需的IP列表。這些IP通常外包給第三方IP供應商。這些IP可以是軟核、硬核,這取決于更改參數(shù)的靈活性水平。IP也可以由同一家公司制作。

在步驟2中,集成IP,生成整個設(shè)計的RTL描述。RTL代表寄存器傳輸級別,它包括各種硬件描述語言的使用,如Verilog、System Verilog和VHDL。RTL是硬件寄存器之間的同步數(shù)字電路的型號。

在步驟3中,一個門級網(wǎng)表由SoC積分器生成。網(wǎng)關(guān)級的網(wǎng)表(netlist)包含有關(guān)標準單元的邏輯連接性的數(shù)據(jù):組合單元格、順序單元格和網(wǎng)絡。網(wǎng)絡是由兩個或多個相互連接的組件組成的一組。用于測試的設(shè)計(DFT)工具用于提高可測試性。

在步驟4中,根據(jù)物理設(shè)計流程將網(wǎng)關(guān)級網(wǎng)表轉(zhuǎn)換為布局。在這個階段也可以導入IP核。物理設(shè)計包括將設(shè)計的電路表現(xiàn)形式轉(zhuǎn)換成幾何形狀,從而在制造后使元件發(fā)揮作用。

在步驟5中,假設(shè)靜態(tài)時序分析和功率分析已經(jīng)完成,最終的布局將被開發(fā)并送往制造。

第6步,在組裝過程中檢查制作好的芯片。在此步驟之前,要徹底檢查芯片的邏輯正確性。這種檢查被稱為功能驗證,它占整個過程的很大一部分。為了執(zhí)行驗證,像SystemC、System Verilog這樣的語言越來越受歡迎,他們應對復雜性有自己的妙招。

重要的是,在制造后對芯片進行任何更改都是非常困難和昂貴的。因此,設(shè)計的仿真(原型)是在制造之前進行的。這通常使用FPGA來完成,因為它是可重新編程的,并且允許調(diào)試。

SoC的優(yōu)缺點

SoC的主要目標是最小化外部組件。因此,較之單板機有以下優(yōu)點:

1.大小:SoC的大小相當于一枚硬幣。由于MOS技術(shù)的不斷演進,SoC可以做得非常小,同時能夠執(zhí)行復雜的任務。尺寸不影響芯片的特性。

2.低功耗:SoC針對手機等低功耗設(shè)備進行了優(yōu)化。低功耗讓手機的電池容量更高。

3.靈活性:SoC很容易重新編程,這使得它們很靈活。它們允許IP的重用。

4.可靠性:SoC提供了更高的電路安全性,降低了設(shè)計復雜性。

5.成本效益:主要由于較少的物理組件和設(shè)計重用

6.更快的電路操作

但它也有一些缺點:

1.耗時:從設(shè)計到制造的整個過程可能需要6個月到1年。因此,市場需求的時間是非常高的。

2.設(shè)計驗證要求非常高,消耗了總時間的70%。由于SoC設(shè)計的日益復雜,設(shè)計驗證越來越繁瑣。此外,IP的可用性和兼容性起著非常重要的作用,可以增加上市時間。

3.制造成本呈指數(shù)增長。

4.對于小批量產(chǎn)品,SoC可能不是最佳選擇。

應用程序

今天,SoC最常見的應用是移動應用,包括智能手機、智能手表和平板電腦。其他應用包括信號語音處理,PC接口,數(shù)據(jù)通信。由于集成了LTE和無線網(wǎng)絡等通信模塊,SoC也被應用到個人電腦上。

目前市場上最受歡迎的當屬由高通生產(chǎn)的SoC,用于智能手機、智能手表和即將到來的5G網(wǎng)絡兼容。其他制造商包括英特爾科技、三星、蘋果、華為海思等。

編輯:hfy

-

soc

+關(guān)注

關(guān)注

38文章

4199瀏覽量

218995 -

無線網(wǎng)絡

+關(guān)注

關(guān)注

6文章

1443瀏覽量

66077 -

數(shù)字信號處理器

+關(guān)注

關(guān)注

5文章

470瀏覽量

27405 -

硅芯片

+關(guān)注

關(guān)注

0文章

91瀏覽量

17039

發(fā)布評論請先 登錄

相關(guān)推薦

SoC設(shè)計中什么構(gòu)成了良好的互聯(lián)?

SOC設(shè)計從Spec到流片:一窺全流程

SOC設(shè)計與驗證流程是什么?

SoC是什么意思

SoC芯片的開發(fā)流程有哪幾個階段

SoC設(shè)計流程相關(guān)資料下載

使用Arm DesignStart處理器核搭建SoC流程

SOC的多核啟動流程詳解

嵌入式SoC IC 的設(shè)計方法和流程

用于SoC驗證的(UVM)開源參考流程使EDA360的SoC

SoC系統(tǒng)知識與設(shè)計測試

如何搭建SoC項目的基本流程

SoC設(shè)計流程

什么構(gòu)成了SoC SoC設(shè)計流程步驟詳解

什么構(gòu)成了SoC SoC設(shè)計流程步驟詳解

評論