本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。

下面詳細介紹第二部分:不同邏輯電平之間的互連。

1、LVPECL的互連

1.1、LVPECL到CML的連接

一般情況下,兩種不同直流電平的信號(即輸出信號的直流電平與輸入需求的直流電平相差比較大),比較提倡使用AC耦合,這樣輸出的直流電平與輸入的直流電平獨立。

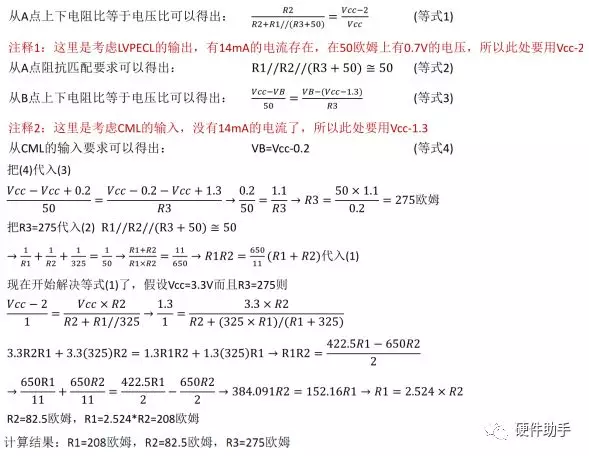

1.1.1、直流匹配

在LVPECL到CML的直流耦合連接方式中需要一個電平轉換網絡。該電平轉換網絡的作用是匹配LVPECL的輸出與CML的輸入共模電壓。一般要求該電平轉換網絡引入的損耗要小,以保證LVPECL的輸出經過衰減后仍能滿足CML輸入靈敏度的要求;另外還要求從LVPECL端看到的負載阻抗近似為50Ω。

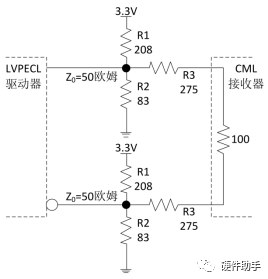

直流耦合

如果要連接LVPECL到CML,需要增加如上圖所示的電阻網絡來進行電平轉換,從而同時滿足LVPECL的輸出和CML的輸入要求。下一步計算同時滿足LVPECL的輸出和CML的輸入要求的R1、R2和R3的數值。

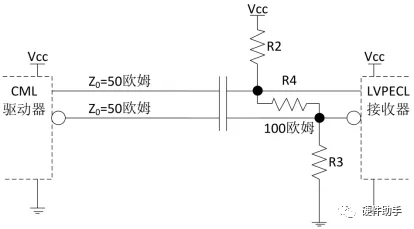

1.1.2、交流匹配

在LVPECL的兩個輸出端各加一個到地的偏置電阻,電阻值選取范圍可以從142Ω到200Ω。如果LVPECL的輸出信號擺幅大于CML的接收范圍,可以在信號通道上串一個25Ω的電阻,這時CML輸入端的電壓擺幅變為原來的0.67倍。(LVPECL輸出擺幅600-1000mV,CML輸入擺幅400-1000mV)

如果LVPECL輸出800mV>CML輸入400mV,需要用額外的電阻降低電壓幅度,此時需要R2≈50?。

交流耦合

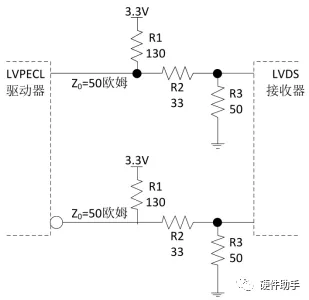

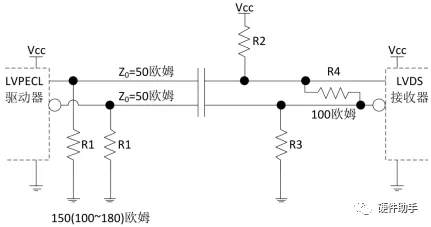

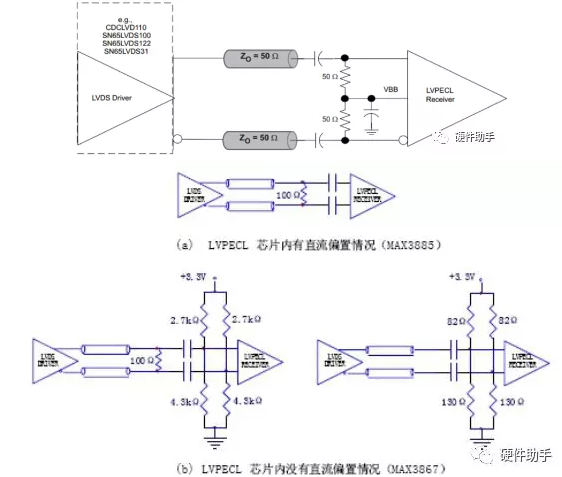

1.2、LVPECL到LVDS的連接

1.2.1、直流匹配

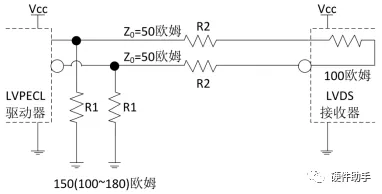

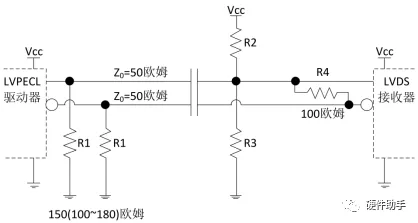

LVPECL到LVDS的直流耦合結構需要一個電阻網絡,設計該網絡時有這樣幾點必須考慮:首先,我們知道當負載是50Ω接到Vcc-2V時,LVPECL的輸出性能是最優的,因此我們考慮該電阻網絡應該與最優負載等效;然后我們還要考慮該電阻網絡引入的衰減不應太大,LVPECL輸出信號經衰減后仍能落在LVDS的有效輸入范圍內。注意LVDS的輸入差分阻抗為100Ω,或者每個單端到虛擬地為50Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等。

直流耦合

沿用130歐姆和83歐姆的模式,由于LVPECL的差分幅度一般大于LVDS的輸入要求,所以對83歐姆進行了分壓。這個電路既減少了交流擺幅到LVDS能承受的范圍,也把直流偏置電壓到LVDS需要的1.2V左右。

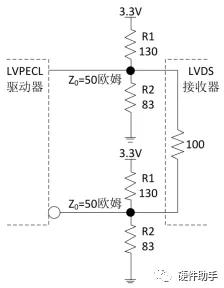

直流耦合

還有一種分壓方式如下,擺幅被壓縮了,但是直流偏置電壓依然是LVPECL的VCC-1.3V。

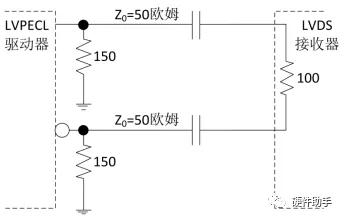

直流耦合

如果LVDS輸入端可以承受比較大得差分電壓(大部分LVDS接收器可以承受LVPECL輸出的信號幅度),而且能承受VCC-1.3V的直流偏置電壓,則不需要電阻分壓了。

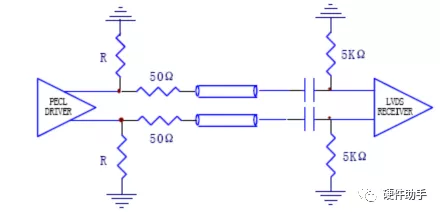

1.2.2、交流匹配

由于LVDS芯片一般內置100歐姆匹配和偏置,直接下拉后加電容即可。

交流耦合

如果LVDS接收端沒有內置偏置和匹配電阻,就需要外接提供100歐姆匹配和K級別電阻提供1.25V的直流偏置。

交流耦合

交流耦合

在LVPECL的兩個輸出端各加一個到地的偏置電阻,電阻值選取范圍可以從142Ω到200Ω。同時信號通道上一定要串接50Ω電阻,以提供一定衰減。LVDS的輸入端到地需加5KΩ電阻,以提供共模偏置。

交流耦合

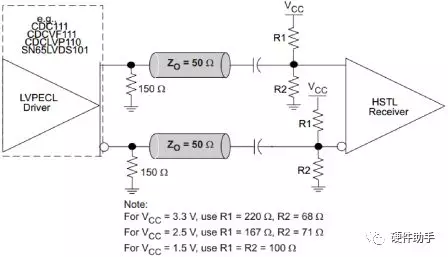

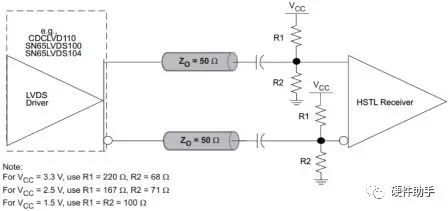

1.3、LVPECL到HSTL的連接

150?電阻用作LVPECL輸出的直流偏置(VCC-1.3V),也提供了一個源電流的直流通路。在HSTL接收端,R1和R2被用作戴維南端接,阻抗為50?(R1//R2),同時也設定了共模電壓(VCM=0.75V)。

2、CML的互連

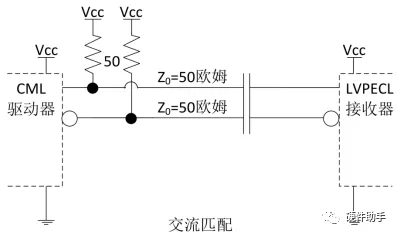

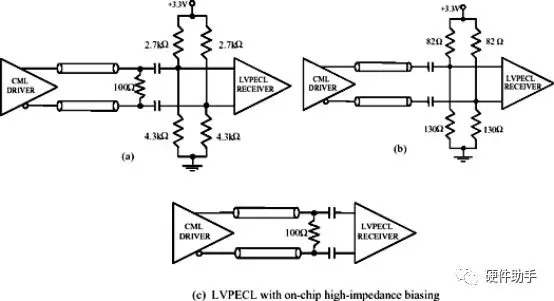

2.1、CML到LVPEL的連接

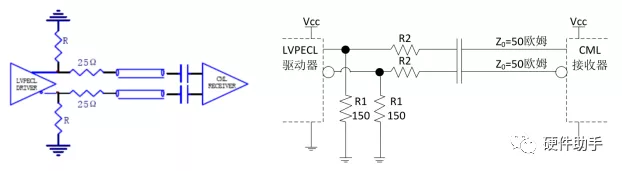

通常情況下,建議CML驅動LVPECL時采用交流匹配,不采用直流匹配。

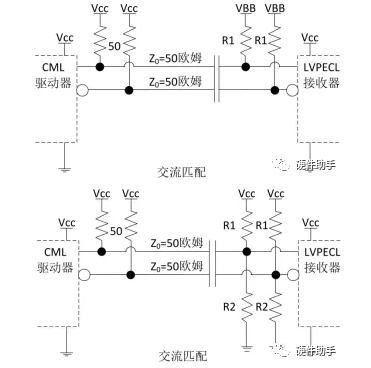

2.1.1、50歐姆上拉匹配

如果LVPECL接收器的輸入帶有偏置,則可以通過電容直連。CML輸出上拉50歐姆作為直流偏置。

2.1.2、50歐姆上拉+偏置

如果LVPECL接收器的輸入不帶有偏置,則需要用外部電阻提供偏置電壓。

推薦使用的交流匹配方式如下:

交流耦合

交流耦合

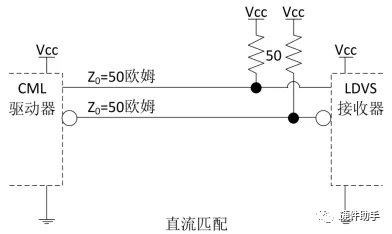

2.2、CML到LVDS的連接

2.2.1、直流匹配

LVDS的輸入側支持1.25±1V的直流電平,如果CML的輸出在這個范圍內則可以直接連接。

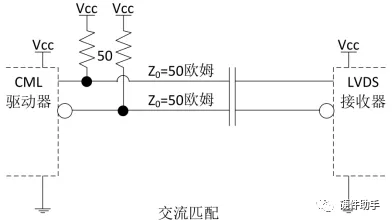

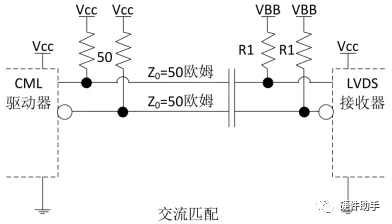

2.2.2、交流匹配

如果LVDS輸入內置直流偏置則如圖連接。

如果LVDS輸入沒有內置直流偏置則需要增加直流偏置。

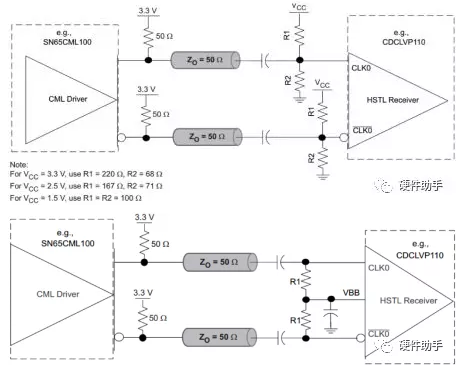

2.3、CML到HSTL

CML和HSTL的互連推薦采用交流耦合。

3、LVDS的互連

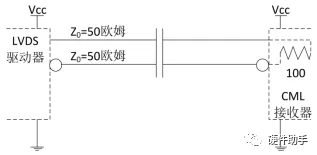

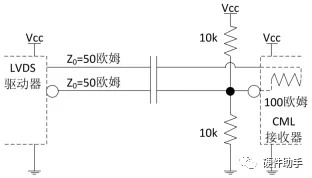

3.1、LVDS到CML的連接

一般情況下,不會存在LVDS與CML之間的對接,因為CML電平一般用在高速信號,如2.5G/10G等場合。而LVDS一般很難用在那么高的速率。

通常情況下,建議LVDS驅動CML時采用交流匹配。確保輸出的交流幅度是否落在輸入交流幅度之內。

CML一般都內置了匹配電阻。如果CML的輸入沒有直流偏置,則需要2個10K電阻。

交流耦合

交流耦合

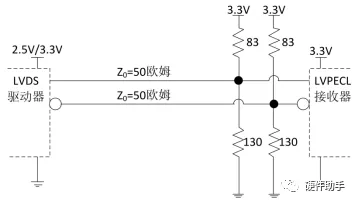

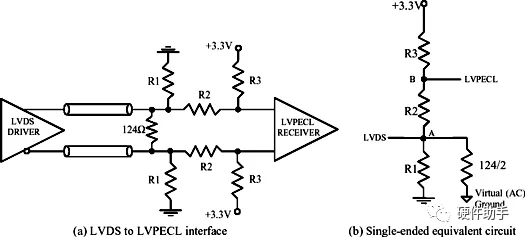

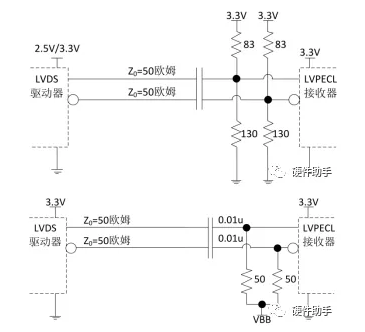

3.2、LVDS到LVPECL的連接

LVDS的輸出幅度比較小,如果后端LVPECL的輸入能夠接受才可以連接,否則要加轉換芯片。

3.2.1、直流匹配

LVDS到LVPECL的直流耦合結構中需要加一個電阻網絡,該電阻網絡完成直流電平的轉換。LVDS輸出電平為1.2V,LVPECL的輸入電平為Vcc-1.3V。LVDS的輸出是以地為基準,而LVPECL的輸入是以電源為基準,這要求考慮電阻網絡時應注意LVDS的輸出電位不應對供電電源敏感;另一個問題是需要在功耗和速度方面折中考慮,如果電阻值取的較小,可以允許電路在更高的速度下工作,但功耗較大,LVDS的輸出性能容易受電源的波動影響;還有一個問題就是要考慮電阻網絡與傳輸線的匹配。

直流耦合

直流耦合

3.2.1、交流匹配

接收端電阻網絡中間接入一電容到地,這樣可以消除差分線上的共模噪聲。

交流耦合

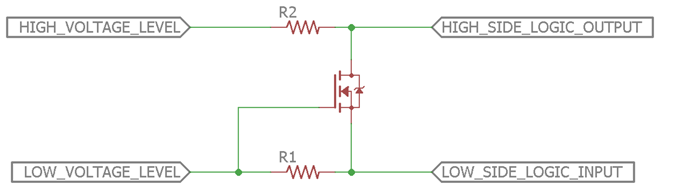

3.3、LVDS到HSTL的連接

CML和HSTL的互連推薦采用交流耦合。

編輯:hfy

-

lvds

+關注

關注

2文章

1043瀏覽量

65860 -

邏輯電平

+關注

關注

0文章

152瀏覽量

14437 -

HSTL

+關注

關注

0文章

4瀏覽量

9657

發布評論請先 登錄

相關推薦

hdmi是什么電平?hdmi信號里有幾對差分還有幾個單端的,差分的信號是不是cml電平?

ADS5404可以使用LVDS或LVPECL的時鐘源頭嗎?

請問DAC3161的DACCLK能否支持LVDS電平輸入嗎?

當ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

LMK00725是否支持LVDS或者LVPECL的差分交流耦合輸入呢?

邏輯電平輸出是什么意思

TUSB542/TUSB551這類re-driver的TX,RX接口類型是屬于哪種?

探索高性能:MEMS 可編程 LVPECL/LVDS 振蕩器 SiT9122 系列(220 至 625 MHZ)

SN65LVELT23 3.3雙通道差分LVPECL/LVDS緩沖器至LVTTL轉換器數據表

SN65LVDS20/SN65LVP20帶使能功能的LVPECL和LVDS中繼器/轉換器數據表

SN65CML100D 1.5 Gbps LVDS/LVPECL/CML-TO-CML轉換器/中繼器數據表

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

評論