云服務(wù)和5G的推出推動(dòng)了數(shù)據(jù)流量的大幅增長(zhǎng),這為滿足網(wǎng)絡(luò)日益增長(zhǎng)的帶寬要求帶來了挑戰(zhàn),路由器和交換機(jī)接線端口密度、光學(xué)標(biāo)準(zhǔn)的擴(kuò)展以及光纖網(wǎng)絡(luò)帶寬的更新是成本能夠滿足帶寬需求的主要制約因素,轉(zhuǎn)換為58G收發(fā)器是非常重要的一步,在相同的條件下它能夠?qū)崿F(xiàn)400G以上的數(shù)據(jù)傳輸速率。

PAM4技術(shù)的發(fā)展

圖1:每年FPGA收發(fā)器的速率變化

NRZ(non-return-to-zero,不歸零碼)是25Gb/s的標(biāo)準(zhǔn)編碼方案,然而對(duì)于不斷增長(zhǎng)的容量、遠(yuǎn)程應(yīng)用程序和數(shù)據(jù)傳輸速率的需求仍在增加,傳統(tǒng)的NRZ信號(hào)高速互聯(lián)的數(shù)據(jù)速率已經(jīng)達(dá)到25Gb/s的上限,PAM4(4級(jí)脈沖調(diào)制)目前被廣泛認(rèn)為是25Gb/s以上數(shù)據(jù)傳輸速率下最健壯、最靈活的信令標(biāo)準(zhǔn)。

采用NRZ技術(shù)你可以在給定的頻率下每個(gè)時(shí)鐘周期傳輸一位信息(1/0),與NRZ相比PAM4通過在每個(gè)符號(hào)中多傳輸兩位比特將給定數(shù)據(jù)速率的帶寬減少一半,這允許用戶在不增加所需帶寬的情況下將信道中的比特率提高一倍。

雖然25Gb/s比特速率以25Gbaud/s的速度傳輸,NRZ信令的Nyquist頻率為14GHz,56Gb/s比特速率以25Gbaud/s傳輸同時(shí)PAM4信令Nyquist頻率為14GHz(參見圖2)。

圖2:PAM4背板測(cè)試——復(fù)用現(xiàn)有的平臺(tái)和設(shè)施

PAM4技術(shù)的優(yōu)勢(shì)

系統(tǒng)供應(yīng)商面臨的一個(gè)挑戰(zhàn)是他們提供的傳統(tǒng)背板和電氣互連不能夠承受超過25Gb/s的傳輸速率,另一個(gè)挑戰(zhàn)是現(xiàn)在基礎(chǔ)設(shè)施中的整套材料、連接器、背板,因?yàn)閺?qiáng)大的基于DSP均衡的Virtex UltraScale+ FPGA GTM收發(fā)器和頻道損失將類似25G線速率,現(xiàn)有的25G背板和走線可以再利用56G信號(hào)流,GTM收發(fā)器可以利用相同的材料同時(shí)使得帶寬加倍。Xilinx一直在使用各種接線和背板進(jìn)行測(cè)試,從而確保當(dāng)Xilinx FPGA用戶遷移到下一代平臺(tái)和高性能互聯(lián)時(shí)之前的任何設(shè)計(jì)都能夠正常工作。

Xilinx演示58G 的GTM收發(fā)器,在雙通道上采用100G以太網(wǎng)

Xilinx展示了100G以太網(wǎng)在雙通道上通過Xilinx 58G GTM收發(fā)器和Virtex UltraScale+ FPGA集成的100G以太網(wǎng)子系統(tǒng)。

結(jié)合經(jīng)過驗(yàn)證的高端Virtex UltraScale+ FPGA以及完全兼容的PAM4技術(shù),Virtex UltraScale+ 58G FPGA可用于數(shù)據(jù)中心和大型網(wǎng)絡(luò)。下一代調(diào)制技術(shù)即將到來,Xilinx讓我們的客戶有充分的時(shí)間準(zhǔn)備下一代平臺(tái),同時(shí)保留現(xiàn)有的基礎(chǔ)設(shè)施,你準(zhǔn)備好了嗎?

編輯:hfy

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3429瀏覽量

106018 -

路由器

+關(guān)注

關(guān)注

22文章

3732瀏覽量

113840 -

pam4

+關(guān)注

關(guān)注

2文章

36瀏覽量

14428

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD Versal自適應(yīng)SoC GTM如何用XSIM仿真和觀察PAM4信號(hào)

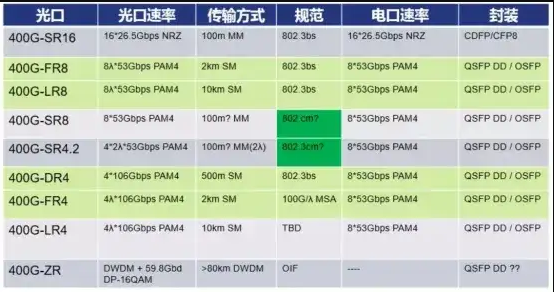

400G光模塊有哪些分類

“又見112G” | Samtec和Keysight展示新型112 Gbps PAM4連接性

了解高速56G PAM-4串行鏈路的時(shí)鐘需求

古希臘掌管224G 的神 | Samtec 224G PAM4 高速互連大合集!

安費(fèi)諾OverPass電纜組件開啟高速線纜新時(shí)代

一文了解Samtec 超微型連接器 | 可靠性極高的56 Gbps PAM4性能

DS560MB410低功耗56Gbps PAM4 4通道線性轉(zhuǎn)接驅(qū)動(dòng)數(shù)據(jù)表

100G QSFP28雙纖單波光模塊的高性價(jià)比解決方案

Samtec技術(shù)前沿 | 新型 Samtec前面板電纜系統(tǒng)帶來112 Gbps PAM4優(yōu)異性能

SG3225EEN在PAM4光模塊和400G,QSFP-DD光模塊中的應(yīng)用

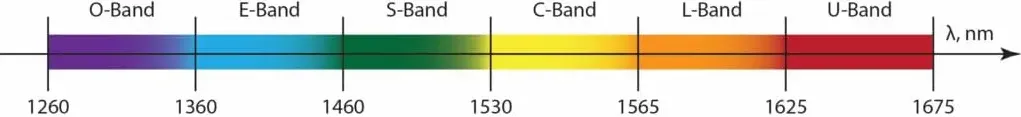

O-Band——真正的100G DWDM解決方案

AMD硅芯片設(shè)計(jì)中112G PAM4串?dāng)_優(yōu)化分析

三星將展示16Gb GDDR7技術(shù),重點(diǎn)關(guān)注PAM3優(yōu)化TRX均衡和ZQ校準(zhǔn)

如何克服PAM4調(diào)制的仿真挑戰(zhàn)呢?

先進(jìn)58G PAM4技術(shù)的部署和發(fā)展

先進(jìn)58G PAM4技術(shù)的部署和發(fā)展

評(píng)論