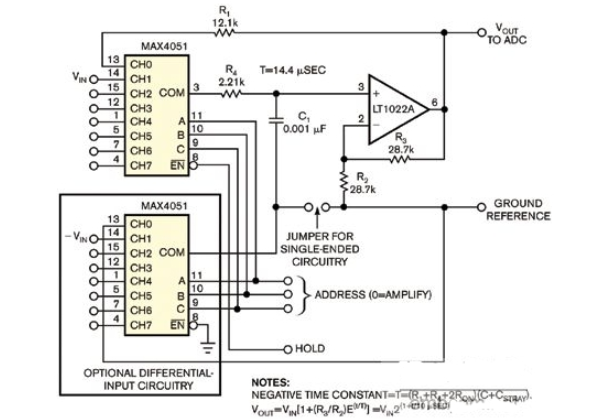

ADC需要有充足的信號采集模擬接口,才能獲得性能。傳統的通用ADC前端包括多個差分輸入通道,數字可編程增益,以及跟蹤與保持功能。本設計實例給出了一個完整的高性能、低元件數的全新ADC前端,實現了整套的標準功能(圖1)。不過,它還帶有飛跨電容差分輸入概念,以及早先一個設計實例所描述的發散指數負時間常數(參考文獻1)。本設計實例為該電路增加了多工輸入以及一個通用的跟蹤保持功能。

圖1:這款高性能、低元件數的ADC前端實現了標準功能組。

多路器地址與保持模式狀態位控制著信號的采集與整形。當保持態為零,多路器地址等于所選的輸入通道時,飛跨電容C1連接到正、負差分輸入端,用于輸入電壓的采集。保持態轉換為1時將C1與輸入端隔離。于是多路器地址為0,保持態返回0,開始對輸入電壓作負時間常數的指數放大。從這一點,直到再次保持,并且連接的ADC作采樣,以及轉換輸出電壓的點,輸入電壓和輸出電壓都是時間的發散指數函數,增益等于2(1+t/10μs)。

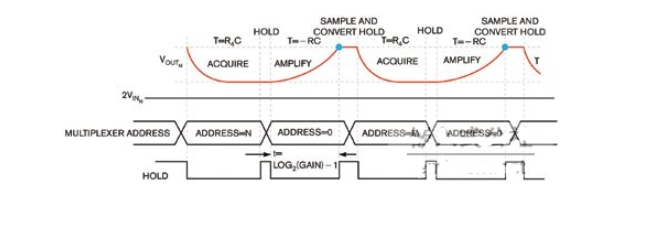

圖2:只有放大期間時序的分辨率限制著增益設定的 。

這個新電路建立在較早設計的基礎上,擁有多臺儀器差分輸入所需要的特性。另外,電阻匹配問題和運放的CMR(共模抑制)都不會限制電路的 CMR。雜散電容是對CMR的一個影響因素,但可以通過電路的精心布局,盡可能減少這一電容。電路亦有軌至軌的輸入,以及幾乎無限制的可編程增益。此外,增益設置的分辨率只受放大期間的時序分辨率影響(圖2和圖3)。此電路亦有±10V的輸出幅度,比單片數字可編程增益儀表放大器要高出一至三倍。

圖3:這個輸入、輸出電壓增益圖給出了跟蹤/放大邏輯轉換的持續時間。

所選運放的固有噪聲與直流、指數時序生成的與可重復性、ADC采樣分辨率,以及RC時間常數的穩定性等,都是信號處理性能和放大器的主要限制因素,如其增益設定、直流誤差、噪聲以及抖動等。在電路中,1 ns的放大期間時序誤差或抖動就相當于0.007%的增益設定誤差。

編輯:hfy

-

放大器

+關注

關注

143文章

13627瀏覽量

214145 -

adc

+關注

關注

99文章

6533瀏覽量

545654 -

信號處理

+關注

關注

48文章

1041瀏覽量

103387

發布評論請先 登錄

相關推薦

高性能、低元件數的全新ADC前端設計實例

高性能、低元件數的全新ADC前端設計實例

評論