在基于IP復用的SoC設計中,片上總線設計是最關鍵的問題。為此,業界出現了很多片上總線標準。其中,由ARM公司推出的AMBA片上總線受到了廣大IP開發商和SoC系統集成者的青睞,已成為一種流行的工業標準片上結構。AMBA規范主要包括了AHB(Advanced High performance Bus)系統總線和APB(Advanced Peripheral Bus)外圍總線。 AMBA 2.0規范包括四個部分:AHB、ASB、APB、AXI和Test Methodology。AHB的相互連接采用了傳統的帶有主模塊和從模塊的共享總線,接口與互連功能分離,這對芯片上模塊之間的互連具有重要意義。AMBA已不僅是一種總線,更是一種帶有接口模塊的互連體系。

1.1.1AMBA協議的演進

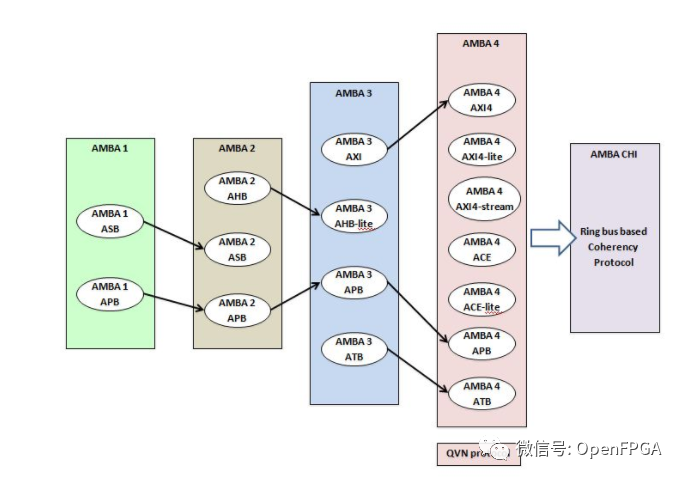

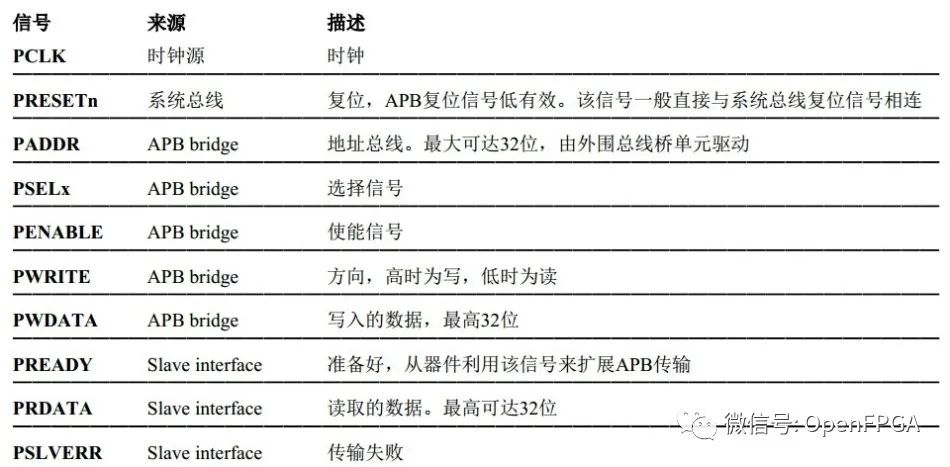

圖4?4 AMBA協議的演進 ·AMBA 1只有ASB和APB協議; ·AMBA 2引入AHB協議用于高速數據傳輸; ·AMBA 3,為適應高吞吐量傳輸和調試引入AXI和ATB,增加高級可擴展接口,而AHB協議縮減為AHB-lite,APB協議增加了PREADY和PSLVERR,ASB由于設計復雜而不再使用; ·AMBA 4,AXI得到了增強,引入QOS和long burst的支持,根據應用不同可選AXI4,AXI4-lite,AXI4-stream,同時為滿足復雜SOC的操作一致性引入ACE和ACE-lite協議,APB和ATB也同時得到增強,比如APB加入了PPROT和PSTRB,另外為改善總線數據傳輸引入QVN協議; ·適應更加復雜的高速NOC設計,引入環形總線協議,推出的AMBA CHI協議。 V1.0 ASB、APB是第一代AMBA協議的一部分。主要應用在低帶寬的外設上,如UART、 I2C,它的架構不像AHB總線是多主設備的架構,APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。APB的協議也十分簡單,甚至不是流水的操作,固定兩個時鐘周期完成一次讀或寫的操作。其特性包括:兩個時鐘周期傳輸,無需等待周期和回應信號,控制邏輯簡單,只有四個控制信號。傳輸可用如下狀態圖表示,

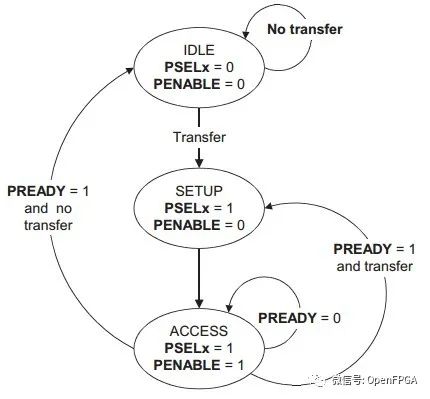

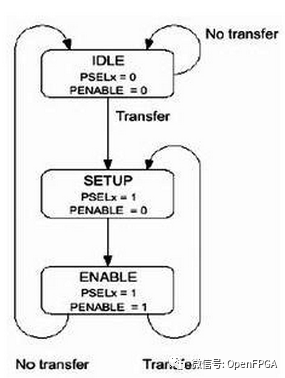

圖4?5 傳輸狀態圖 ·系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。 ·當有傳輸要進行時,PSELx=1,PENABLE=0,系統進入SETUP狀態,并只會在SETUP 狀態停留一個周期。當PCLK的下一個上升沿時到來時,系統進入ENABLE 狀態。 ·系統進入ENABLE狀態時,維持之前在SETUP 狀態的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之后就已完成。之后如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。 V2.0 AHB是第二代AMBA協議最重要的一部分。AHB總線規范是AMBA總線規范的一部分,AMBA總線規范是ARM公司提出的總線規范,被大多數SoC設計采用,它規定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高時鐘頻率的系統結構,典型的應用如ARM核與系統內部的高速RAM、NAND FLASH、DMA、Bridge的連接。APB用于連接外部設備,對性能要求不高,而考慮低功耗問題。ASB是AHB的一種替代方案。

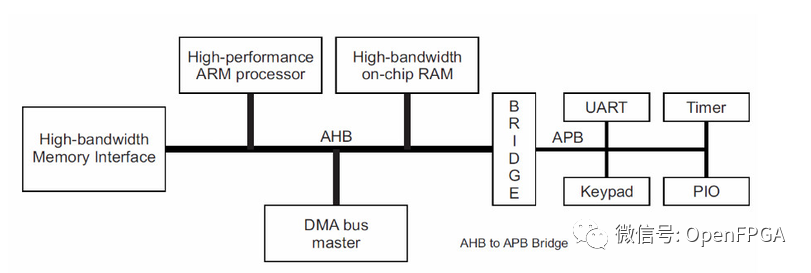

圖4?6 相比于APB,區分了地址周期和數據周期 AHB總線強大之處在于它可以將微控制器(CPU)、高帶寬的片上RAM、高帶寬的外部存儲器接口、DMA總線控制器,以及各種AHB接口的控制器等連接起來構成一個獨立的完整SOC系統,還可以通過AHB-APB橋來連接APB總線系統。

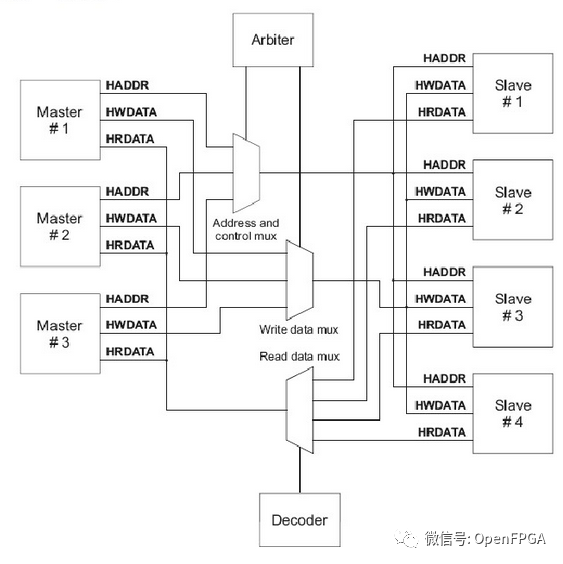

圖4?7 通過AHB-APB橋來連接APB總線系統 AHB總線由主設備Master、從設備Slave,內部包括仲裁器,譯碼器,數據多路和地址控制多路組成。 ·主設備發起一次讀/寫操作,某一時刻只允許一個主設備使用總線。 ·從設備響應一次讀/寫操作,通過地址映射選擇使用哪一個從設備。 ·仲裁器允許某一個主設備控制總線 ·譯碼器通過地址譯碼決定選擇哪一個從設備 仲裁機制 仲裁機制保證了任意時刻只有一個master可以接入總線。arbiter決定哪個發出接入請求的master可以接入總線,這通過優先級算法實現。AHB規范并沒有給出優先級算法,設計者需要根據具體的系統要求定義。一般情況下arbiter不會中斷一個burst傳輸,將總線接入權讓給其他master。當然未定義長度的burst傳輸是可以打斷的,這要看優先級算法是如何規定的。如果一筆burst被打斷,master再度獲得接入權限時,會傳遞剩余的部分。如一筆長度為INCR8的傳輸在傳遞3 beat后被打斷,master再次獲得接入授權后,會繼續傳輸剩余的5 beat,剩余部分可以由一個SINGLE和一個INCR4組成,或者一個INCR。 地址譯碼器 地址譯碼器用于為總線上每個slave提供選擇信號HSELx,選擇信號是通過組合邏輯對地址碼譯碼產生的。只有當前的數據傳輸完成后(HREADY為高),slave才會采樣地址和控制信號以及HSELx。在一定條件下可能會出現這樣的情況:產生HSELx信號而HREADY為低,在當前傳輸后slave會改變。每個slave最小的地址空間為1KB,所有的master的burst傳輸上限也是1KB,如此設計保證了不會出現地址越界問題。當一個設計不會用到所有的地址空間時,可能出現訪問到一個不存在的地址的情況,這就需要增加一個附加的默認slave來為上面的情況提供一個響應。當SEQ或NONSEQ傳輸訪問到一個不存在的地址,默認slave應該提供ERROR響應;當IDLE或BUSY傳輸訪問到一個不存在的地址,默認slave會響應OKAY。地址譯碼器會帶有實現默認slave的功能。 表4?1 各個信號描述

| Name | Source | To | Description |

| HCLK | clock source | 各module | 總線時鐘,上升沿采樣 |

| HRESETn | reset controller | 各module | 總線復位,低電平有效 |

| HADDR[31:0] | Master | Decoder mux to slave arbiter | 32位系統地址總線 |

| HTRANS[1:0] | Master | mux to slave | 當前傳輸類型NONSEQ, SEQ, IDLE, BUSY |

| HWRITE | Master | mux to slave | 1為寫,0為讀 |

| HSIZE[2:0] | Master | mux to slave | 每一個transfer傳輸的數據大小,以字節為單位,最高支持1024位 |

| HBURST[2:0] | Master | mux to slave | burst類型,支持4、8、16 burst,incrementing/wrapping |

| HPROT[3:0] | Master | mux to slave | 保護控制信號,需要slave帶保護功能,一般不用 |

| HWDATA[31:0] | Master | mux to slave | 寫數據總線,Master到Slave |

| HRDATA[31:0] | Slave | mux to master | 讀數據總線,Slave到Master |

| HREADY | Slave |

mux to master arbiter |

高:Slave指出傳輸結束 低:Slave需延長傳輸周期 |

| HRESP[1:0] | Slave |

mux to master arbiter |

Slave發給Master的總線傳輸狀態OKAY, ERROR, RETRY, SPLIT |

| HSELx | Decoder | slave | slave選擇信號 |

HRESP[1:0] 響應信號 傳輸響應HRESP[1:0] 00: OKAY 01: ERROR 10: RETRY 傳輸未完成,請求主設備重新開始一個傳輸,arbiter會繼續使用通常的優先級 11: SPLIT 傳輸未完成,請求主設備分離一次傳輸,arbiter會調整優先級方案以便其他請求總線的主設備可以訪問總線 表4?2 AHB仲裁信號

| Name | Source | To | Description |

| HBUSREQx | Master | arbiter | master給仲裁器的請求獲得總線使用權的請求信號,最多支持16個master |

| HLOCKx | Master | arbiter | 如果一個master希望自己在傳輸期間不希望丟掉總線,則需要向仲裁器發送這個鎖定信號 |

| HGRANTx | arbiter | master | 授權信號,當前bus master x的優先級最高。當HREADY和HGRANTx同時為高時,master獲取系統總線的權利 |

| HMASTER [3:0] | arbiter | 具有split功能的slave | 仲裁器為每一個master分配的ID,指出哪個主設備正在進行傳輸,提供進行split的信息,用于地址控制多路選擇哪個主設備接入總線。 |

| HMASTLOCK | arbiter | 具有split功能的slave | 表示當前的master正在執行Locked操作。這個信號和HMASTER有這相同的時序 |

| HSPLITx[15:0] | slave | arbiter | 從設備用這個信號告訴仲裁器哪個主設備運行重新嘗試一次split傳輸,每一位對應一個主設備 |

V3.0 AXI(Advanced eXtensible Interface)是一種總協議,該協議是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0協議中最重要的部分。 ·高性能、高帶寬、低延遲的片內總線 ·地址/控制和數據相位是分離的,分離的讀寫數據通道。控制和數據通道分離,就可以不等需要的操作完成,就發出下一個操作,流水線操作,數據吞吐量增加達到提速的作用。 ·單向通道體系結構,使得片上信息流只是以單方向傳輸,減少了延時,更小的面積,更低的功耗,獲得優異的性能。 AXI4 是第四代AMBA協議重要的一部分,AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-streamAXI4.0-lite是AXI的簡化版本,ACE4.0 是AXI緩存一致性擴展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA進行以數據為主導的大量數據的傳輸應用。 · 適合高帶寬低延時設計,無需復雜的橋就實現高頻操作,向下兼容已有的AHB和APB接口。 ·分離地址/控制、數據相位 ·分離的讀寫數據通道,提供低功耗DMA ·使用字節線支持非對齊的數據傳輸 ·使用基于burst的傳輸,只需傳輸首地址 ·支持多種傳輸方式,支持亂序傳輸 ·允許容易的添加寄存器來進行時序收斂 AXI架構分為5個獨立的傳輸通道,讀地址通道、讀數據通道、寫地址通道、寫數據通道、寫響應通道。基于VALID/READY的握手機制數據傳輸協議,傳輸源端使用VALID表明地址/控制信號、數據是有效的,目的端使用READY表明自己能夠接受信息。數據總線可為(8/16/32/64/128/256/512/1024bit),最大為單次傳輸一個字節的數據。 信號描述 表4?3 全局信號

| 信號名 | 源 | 描述 |

| ACLK | 時鐘源 | 全局時鐘信號 |

| ARESETn | 復位源 | 全局復位信號,低有效 |

表4?4 寫地址通道信號

| 信號名 | 源 | 描述 |

| AWID | 主機 | 寫地址ID,用來標志一組寫信號 |

| AWADDR | 主機 | 寫地址,給出一次寫突發傳輸的寫地址 |

| AWLEN | 主機 | 突發長度,給出突發傳輸的次數 |

| AWSIZE | 主機 | 突發大小,給出每次突發傳輸的字節數 |

| AWBURST | 主機 | 突發類型 |

| AWLOCK | 主機 | 總線鎖信號,可提供操作的原子性 |

| AWCACHE | 主機 | 內存類型,表明一次傳輸是怎樣通過系統的 |

| AWPROT | 主機 | 保護類型,表明一次傳輸的特權級及安全等級 |

| AWQOS | 主機 | 質量服務QoS |

| AWREGION | 主機 | 區域標志,能實現單一物理接口對應的多個邏輯接口 |

| AWUSER | 主機 | 用戶自定義信號 |

| AWVALID | 主機 | 有效信號,表明此通道的地址控制信號有效 |

| AWREADY | 從機 | 表明“從”可以接收地址和對應的控制信號 |

表4?5 寫數據通道信號

| 信號名 | 源 | 描述 |

| WID | 主機 | 一次寫傳輸的ID tag |

| WDATA | 主機 | 寫數據 |

| WSTRB | 主機 | 寫數據有效的字節線,用來表明哪8bits數據是有效的 |

| WLAST | 主機 | 表明此次傳輸是最后一個突發傳輸 |

| WUSER | 主機 | 用戶自定義信號 |

| WVALID | 主機 | 寫有效,表明此次寫有效 |

| WREADY | 從機 | 表明從機可以接收寫數據 |

表4?6 寫響應通道信號

| 信號名 | 源 | 描述 |

| BID | 從機 | 寫響應ID tag |

| BRESP | 從機 | 寫響應,表明寫傳輸的狀態 |

| BUSER | 從機 | 用戶自定義 |

| BVALID | 從機 | 寫響應有效 |

| BREADY | 主機 | 表明主機能夠接收寫響應 |

表4?7讀地址通道信號

| 信號名 | 源 | 描述 |

| ARID | 主機 | 讀地址ID,用來標志一組寫信號 |

| ARADDR | 主機 | 讀地址,給出一次寫突發傳輸的讀地址 |

| ARLEN | 主機 | 突發長度,給出突發傳輸的次數 |

| ARSIZE | 主機 | 突發大小,給出每次突發傳輸的字節數 |

| ARBURST | 主機 | 突發類型 |

| ARLOCK | 主機 | 總線鎖信號,可提供操作的原子性 |

| ARCACHE | 主機 | 內存類型,表明一次傳輸是怎樣通過系統的 |

| ARPROT | 主機 | 保護類型,表明一次傳輸的特權級及安全等級 |

| ARQOS | 主機 | 質量服務QoS |

| ARREGION | 主機 | 區域標志,能實現單一物理接口對應的多個邏輯接口 |

| ARUSER | 主機 | 用戶自定義信號 |

| ARVALID | 主機 | 有效信號,表明此通道的地址控制信號有效 |

| ARREADY | 從機 | 表明“從”可以接收地址和對應的控制信號 |

表 4?8 讀數據通道信號

| 信號名 | 源 | 描述 |

| RID | 從機 | 讀ID tag |

| RDATA | 從機 | 讀數據 |

| RRESP | 從機 | 讀響應,表明讀傳輸的狀態 |

| RLAST | 從機 | 表明讀突發的最后一次傳輸 |

| RUSER | 從機 | 用戶自定義 |

| RVALID | 從機 | 表明此通道信號有效 |

| RREADY | 主機 | 表明主機能夠接收讀數據和響應信息 |

表4?9 低功耗接口信號

| 信號名 | 源 | 描述 |

| CSYSREQ | 時鐘控制器 | 系統退出低功耗請求,此信號從“時鐘控制器”到“外設” |

| CSYSACK | 外設 | 退出低功耗狀態確認 |

| CACTIVE | 外設 | 外設請求時鐘有效 |

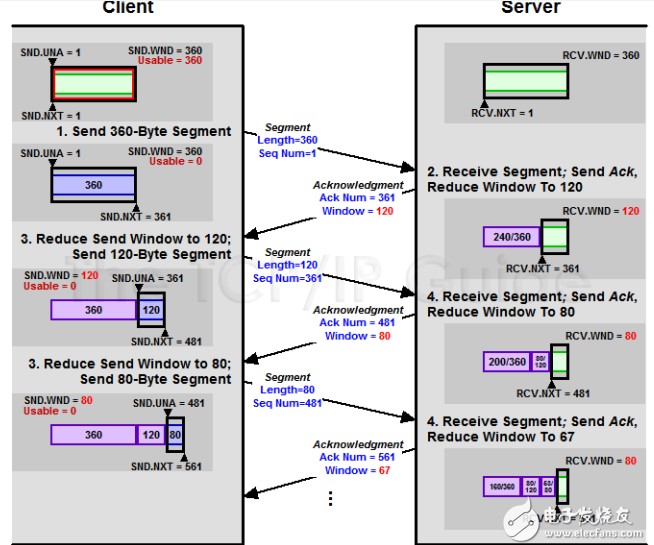

每個數據通道有獨立的xVALID/xREADY握手信號對。 VALID與READY信號作為一對握手信號,為防止死鎖,進行讀操作時,必須等讀地址通道握手完成,讀數據通道才可進行下一步操作。進行寫操作時,寫地址通道與寫數據通道互相獨立,但同樣必須等最后一組數據寫完成寫響應通道握手完成。 AXI協議是基于burst的,主機只給出突發傳輸的第一個字節的地址,從機必須計算突發傳輸后續的地址。突發傳輸不能跨4KB邊界(防止突發跨越兩個從機的邊界,也限制了從機所需支持的地址自增數)。 ·突發長度 ARLEN[7:0]決定讀傳輸的突發長度,AWLEN[7:0]決定寫傳輸的突發長度。AXI3只支持1~16次的突發傳輸(Burst_length=AxLEN[3:0]+1),AXI4擴展突發長度支持INCR突發類型為1~256次傳輸,對于其他的傳輸類型依然保持1~16次突發傳輸(Burst_Length=AxLEN[7:0]+1)。 ·傳輸規則 wraping burst ,burst長度必須是2,4,8,16,burst不能跨4KB邊界,不支持提前終止burst傳輸。 ·突發大小 ARSIZE[2:0],讀突發傳輸;AWSIZE[2:0],寫突發傳輸。 AxSIZE[2:0] bytes in transfer ‘b0001 ‘b0012 ‘b0104 ‘b0118 ‘b10016 ‘b10132 ‘b11064 ‘b111128 ·突發類型 FIXED:突發傳輸過程中地址固定,用于FIFO訪問 INCR:增量突發,傳輸過程中,地址遞增。增加量取決AxSIZE的值。 WRAP:回環突發,和增量突發類似,但會在特定高地址的邊界處回到低地址處。回環突發的長度只能是2,4,8,16次傳輸,傳輸首地址和每次傳輸的大小對齊。最低的地址整個傳輸的數據大小對齊。回環邊界等于(AxSIZE*AxLEN)。 AxBURST[1:0]burst type ‘b00FIXED ‘b01INCR ‘b10WRAP ‘b11Reserved Start_Address=AxADDR Number_Bytes=2^AxSIZE Burst_Length=AxLEN+1 Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。 對于INCR突發和WRAP突發但沒有到達回環邊界,地址由下述方程決定: Address_N=Aligned_Address+(N-1)xNumber_Bytes WRAP突發,突發邊界: Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length) 讀寫響應結構 讀傳輸的響應信息是附加在讀數據通道上的,寫傳輸的響應在寫響應通道。 RRESP[1:0],讀傳輸 BRESP[1:0],寫傳輸 OKAY(‘b00):正常訪問成功 EXOKAY(‘b01):Exclusive 訪問成功 SLVERR(‘b10):從機錯誤。表明訪問已經成功到了從機,但從機希望返回一個錯誤的情況給主機。 DECERR(‘b11):譯碼錯誤。一般由互聯組件給出,表明沒有對應的從機地址。

1.1.2AMBA概述

AMBA (Advanced Microcontroller Bus Architecture) 高級處理器總線架構 AHB (Advanced High-performance Bus) 高級高性能總線 ASB (Advanced System Bus) 高級系統總線 APB (Advanced Peripheral Bus) 高級外圍總線 AXI (Advanced eXtensible Interface) 高級可拓展接口 這些內容加起來就定義出一套為了高性能SoC而設計的片上通信的標準。 AHB主要是針對高效率、高頻寬及快速系統模塊所設計的總線,它可以連接如微處理器、芯片上或芯片外的內存模塊和DMA等高效率模塊。 APB主要用在低速且低功率的外圍,可針對外圍設備作功率消耗及復雜接口的最佳化。APB在AHB和低帶寬的外圍設備之間提供了通信的橋梁,所以APB是AHB或ASB的二級拓展總線。 AXI:高速度、高帶寬,管道化互聯,單向通道,只需要首地址,讀寫并行,支持亂序,支持非對齊操作,有效支持初始延遲較高的外設,連線非常多。 表 4?10 幾種AMBA總線的性能對比分析

| 總線 | AXI | AHB | APB |

| 總線寬度 | 8, 16, 32, 64, 128, 256, 512, 1024 | 32, 64, 128, 256 | 8, 16, 32 |

| 地址寬度 | 32 | 32 | 32 |

| 通道特性 | 讀寫地址通道、讀寫數據通道均獨立 | 讀寫地址通道共用讀寫數據通道 | 讀寫地址通道共用讀寫數據通道不支持讀寫并行操作 |

| 體系結構 | 多主/從設備仲裁機制 | 多主/從設備仲裁機制 | 單主設備(橋)/多從設備無仲裁 |

| 數據協議 | 支持流水/分裂傳輸支持猝發傳輸支持亂序訪問字節/半字/字大小端對齊非對齊操作 | 支持流水/分裂傳輸支持猝發傳輸支持亂序訪問字節/半字/字大小端對齊不支持非對齊操作 | 一次讀/寫傳輸占兩個時鐘周期不支持突發傳輸 |

| 傳輸方式 | 支持讀寫并行操作 | 不支持讀寫并行操作 | 不支持讀寫并行操作 |

| 時序 | 同步 | 同步 | 同步 |

| 互聯 | 多路 | 多路 | 無定義 |

1.1.3AHB總線

AHB的組成 Master:能夠發起讀寫操作,提供地址和控制信號,同一時間只有1個Master會被激活。 Slave:在給定的地址范圍內對讀寫操作作響應,并對Master返回成功、失敗或者等待等狀態。 Arbiter:負責保證總線上一次只有1個Master在工作。仲裁協議是規定的,但是仲裁算法可以根據應用決定。 Decoder:負責對地址進行解碼,并提供片選信號到各Slave。 每個AHB都需要1個仲裁器和1個中央解碼器。

圖4?8 AHB的組成 AHB基本信號 HADDR:32位系統地址總線 HTRANS:M指示傳輸狀態,NONSEQ、SEQ、IDLE、BUSY HWRITE:傳輸方向1-寫,0-讀 HSIZE:傳輸單位 HBURST:傳輸的burst類型 HWDATA:寫數據總線,從M寫到S HREADY:S應答M是否讀寫操作傳輸完成,1-傳輸完成,0-需延長傳輸周期。需要注意的是HREADY作為總線上的信號,它是M和S的輸入;同時每個S需要輸出自HREADY。所以對于S會有兩個HREADY信號,一個來自總線的輸入,一個自己給到多路器的輸出。 HRESP:S應答當前傳輸狀態,OKAY、ERROR、RETRY、SPLIT。 HRDATA:讀數據總線,從S讀到M。 AHB基本傳輸 兩個階段 地址周期(AP),只有一個cycle 數據周期(DP),由HREADY信號決定需要幾個cycle 流水線傳送 先是地址周期,然后是數據周期 AHB突發傳輸與AXI突發傳輸的特點 AHB協議需要一次突發傳輸的所有地址,地址與數據鎖定對應關系,后一次突發傳輸必須在前次傳輸完成才能進行。 AXI只需要一次突發的首地址,可以連續發送多個突發傳輸首地址而無需等待前次突發傳輸完成,并且多個數據可以交錯傳遞,此特征大大提高了總線的利用率。 AHB總線與AXI總線均適用于高性能、高帶寬的SoC系統,但AXI具有更好的靈活性,而且能夠讀寫通道并行發送,互不影響;更重要的是,AXI總線支持亂序傳輸,能夠有效地利用總線的帶寬,平衡內部系統。因此SoC系統中,均以AXI總線為主總線,通過橋連接AHB總線與APB總線,這樣能夠增加SoC系統的靈活性,更加合理地把不同特征IP分配到總線上。

1.1.4APB總線

主要應用在低帶寬的外設上,如UART、 I2C,它的架構不像AHB總線是多主設備的架構,APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。APB的協議也十分簡單,甚至不是流水的操作,固定兩個時鐘周期完成一次讀或寫的操作。其特性包括:兩個時鐘周期傳輸,無需等待周期和回應信號,控制邏輯簡單,只有四個控制信號。APB上的傳輸可用如圖所示的狀態圖來說明。 1、系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。 2、當有傳輸要進行時,PSELx=1,,PENABLE=0,系統進入SETUP狀態,并只會在SETUP狀態停留一個周期。當PCLK的下一個上升沿到來時,系統進入ENABLE狀態。 3、系統進入ENABLE狀態時,維持之前在SETUP狀態的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之后就已完成。之后如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。

圖4?9 APB總線

-

AMBA

+關注

關注

0文章

68瀏覽量

14998 -

AMBA協議

+關注

關注

0文章

7瀏覽量

6463

原文標題:AXI協議詳解-AMBA總線協議AHB、APB、AXI對比分析

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMBA協議的基礎知識介紹

AMBA協議的基礎知識介紹

評論