有人在使用STM32G0芯片的ADC模塊時,往往因為掃描模式的理解不到位或選擇不當導致些問題。這里就該話題做點簡單分享介紹,不妨以一個實例展開。

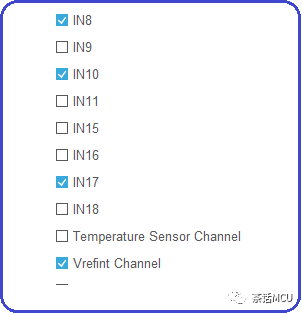

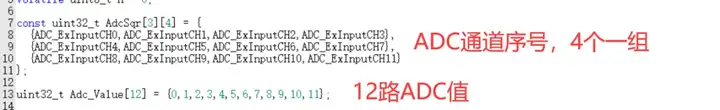

現在共用到ADC1模塊的4個ADC通道,即1個片內Vrefint通道和其它三個外部通道CH8,CH10,CH17。下面測試代碼中使用DMA傳輸,定時器觸發ADC.

它們的硬件連接情況如下,其中VRefint為內部參考電壓,其電壓值大概1.2V樣子。

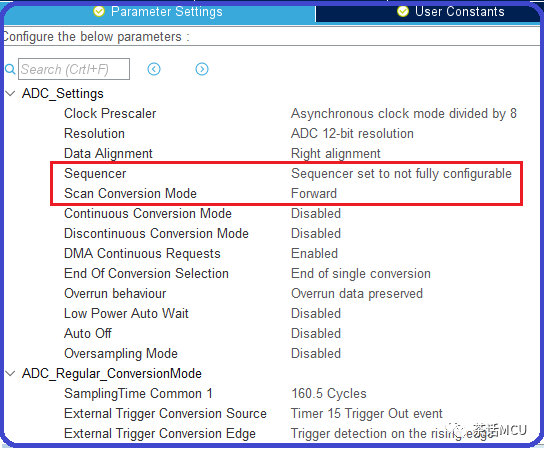

對于STM32G0系列,ADC掃描模式可以有兩種,分別是不完全配置序列模式和完全配置序列模式。我們先看看不完全配置序列模式。

不完全配置序列模式

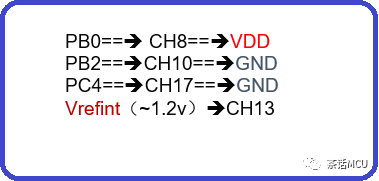

在該模式下,ADC_CFGR1寄存器中的CHESELRMOD位必須被清零。

被轉換通道的掃描順序按照ADC通道固有序號的大小順序依次進行,掃描方向可以軟件配置為向前【forward】或后退【backward】。任何ADC通道都可以配置進該序列中,總的序列長度由寄存器ADC_CHSELR中被置位的CHSELx個數決定,最多可配置18個通道。

我們以上面提到的CH8、CH10、CH17和VRefint通道【它對應ADC通道CH13】為例,若將上述4個通道配置為不完全序列模式,只需將ADC_CHSELR寄存器中的CHSELx相應位進行置1即可。如下圖所示:

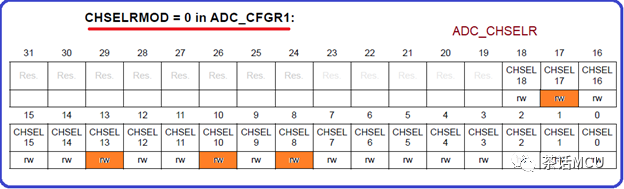

若選擇forward掃描模式,則按通道號從小到大的順序依次實施轉換,生成對應于CH8、CH10、CH13、CH17的結果。使用STM32CubeMx的配置如下:

既然掃描按默認通道號大小順序進行,自然就無須RANK順序的配置了。

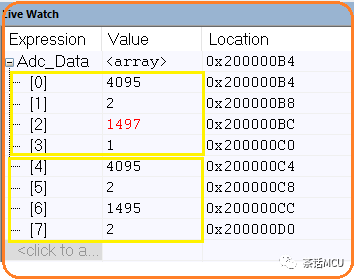

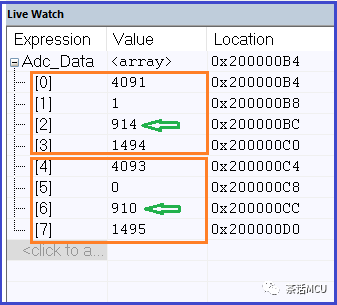

編譯運行后可以看到結果,我在內存里放了兩組數據以便比較觀察。

從結果來看跟實際情況是一致的,轉換結果依次來自CH8/CH10/CH13/CH17。其中那個149x數值來自對內部Vrefint的轉換結果。

那么,對于同樣的ADC通道及硬件連接,若采用完全配置序列模式會怎么樣呢?

完全配置序列模式

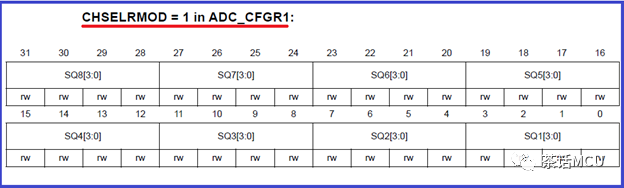

在該模式下,ADC_CFGR1寄存器中的CHESELRMOD位必須被置1。

全序列可支持的通道數最多8個,掃描順序不是依照硬件約定的通道號來安排,而是依據ADC_CHSELR寄存器中的從SQ1[3:0]到SQ8[3:0]所選擇的通道順序進行,即按照我們在CubeMX或代碼中配置的RANK順序進行,不再涉及掃描方向forward/backward的配置,并且只有通道0 到 通道14可以被選擇!

還有,當SQn[3:0]里的賦值等于0b1111,即0x0f時則該通道選擇域以及后續SQn的通道選擇無效。比方說,假設SQ3[3:0]的數據為0b1111,則表示從SQ3[3:0]開始直到SQ8[3:0]的通道選擇無效。由于SQn[3:0]才4位,所有它也沒法選擇高于14的有效通道號。【請特別注意這些特性!】

看到這里,我們不禁想到前面預先安排的4個通道中的有個CH17,顯然不適合這種模式。如果被錯誤地強行使用該模式,基于CubeMx配置和現有Cube庫所產生的代碼運行結果會怎么樣呢?

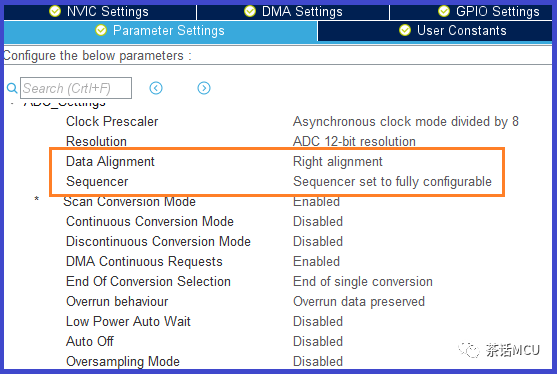

先用CubeMX進行配置:

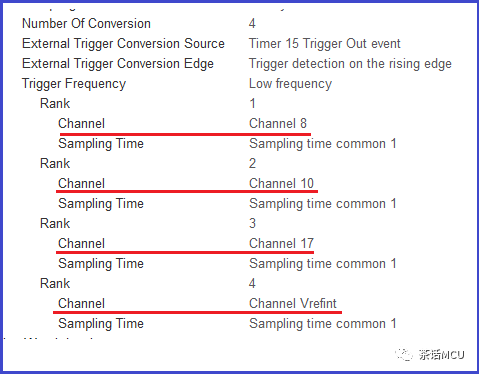

4個通道的掃描順序配置如下,相比前面多了RANK順序配置。

先撇開CH17合法性不談,不難看出這里跟前面的掃描順序配置有點不一樣,這里的配置為我們提供了更多的自主性及便利性,轉換掃描并不固定于通道號的順序,具體由SQn[3:0]的配置選擇決定。我這里讓SQ1選擇CH8,SQ2選擇CH10,SQ3選擇CH17,SQ4選擇CH13,分別對應配置中的RANK1、RANK2、RANK3、RANK4順序。

編譯運行查看結果:

前面說過,CH17硬件上是接地的,顯然此時對應于CH17的轉換值【綠色箭頭所指】跟實際情況完全不符,其它三個倒是跟實際情況吻合。409x對應CH8接VDD,0對應CH10接GND,149x對應內部vrefint。

我嘗試將CH17接到VDD,轉換結果還是跟實際情況還是完全不相符。

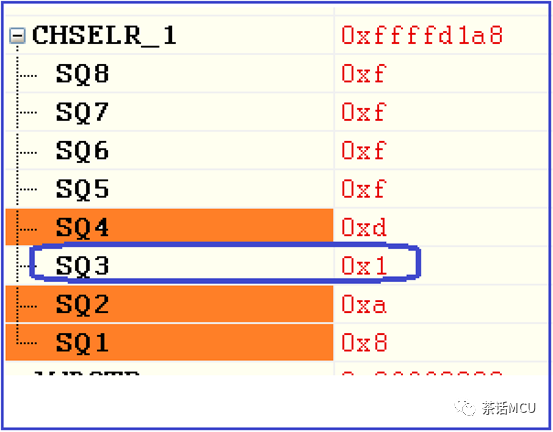

結合上面的介紹,我們知道對于完全配置序列模式不能選用高于通道14的通道號。我們不妨通過寄存器進一步看看,當我們錯誤地強行使用CH17時在現有庫代碼的情況下,對應的SQ3[3:0]真正的值是多少?到底選擇了什么通道?還是CH17嗎?

在調試環境下,打開通道選擇寄存器,可以看到下面結果:

從上面通道選擇寄存器不難看出,除了SQ3外,其它三個配置都是正確的,跟我們預設的通道是一致的。但是,SQ3被錯誤地配置為CH1了,也就是說上面看到的所謂CH17的轉換結果都是來自CH1.難怪不論怎么改變CH17的外部連接時,SQ3選擇通道所對應的轉換結果沒有相應變化,跟CH17的管腳電壓也沒啥關系。

看到這里有人可能會想,如果我們在前面規劃ADC通道時把CH1同時規劃進來、硬件上恰好也接地,這時就可能發生誤判!這種巧合性的誤判,有時可能給我們的調試帶來極大隱患而一會半會又找不到原因。當然,具體會發生些什么要因具體應用而定。這里只是簡單提醒下,就此打住。

總之,這點在STM32G0 ADC應用中是個很容易出錯的地方,將本不該用在完全配置序列模式的通道被錯誤地強行使用,雖有轉換結果,而轉換結果卻來自別的通道,往往為此覺得問題詭異、不可思議而備受折騰。

最后,稍微小結下。對于STM32G0系列的ADC模塊來說,其ADC通道在被轉換時涉及到轉換序列配置問題,這里有兩種轉換序列配置模式,即不完全配置序列模式和完全配置序列模式。

所謂不完全配置序列模式,在進行多個通道AD轉換時,轉換順序由各通道自身的硬件序列號和掃描方向決定,其中硬件序列號即CHn在數據手冊里已經明確定義,掃描方向通過寄存器配置。整個轉換序列可支持的通道數多達18個,沒有被排除在外的通道。

而完全配置序列模式呢,在進行多個通道AD轉換時,轉換順序由通道選擇寄存器中通道選擇域SQn[3:0]來決定,即按照SQ1,SQ2.。。。。SQ7,SQ8的順序,而且SQn[3:0]只能選擇CH0到CH14的通道,整個序列最多支持8個通道。顯然,CH15~CH18不能使用該模式。

說到這里,或許有人會問,如果只使用1個ADC通道,還有這個轉換序列模式的選擇問題嗎?你把1個通道看成一個特殊的轉換序列來理解就知道有沒有這個模式選擇問題了。

芯片設計人員在此提供了兩種轉換序列模式,本意旨在讓我們能在實際應用中可以根據實際需求靈活選擇,然而,往往由于開發人員的慣性思維和無視手冊導致在這個地方遇上點麻煩或困惑。在此分享之,祝君好運!

-

adc

+關注

關注

98文章

6501瀏覽量

544741 -

定時器

+關注

關注

23文章

3250瀏覽量

114865 -

dma

+關注

關注

3文章

561瀏覽量

100603

原文標題:STM32G0系列ADC掃描序列模式解讀

文章出處:【微信號:stmcu832,微信公眾號:茶話MCU】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

測試代碼中使用DMA傳輸,定時器觸發ADC

測試代碼中使用DMA傳輸,定時器觸發ADC

評論